курсовые работы / курсовая работа по организации эвм (mcs 51, скорубский) / Отчет / Курсовая

.pdf

Кафедра Вычислительной Техники СПбГУ ИТМО

Содержание |

|

Введение ............................................................................................................................................... |

3 |

Часть 1. Описание схемы .................................................................................................................... |

4 |

Шинная организация........................................................................................................................ |

4 |

Иерархический принцип.................................................................................................................. |

4 |

Синхронизация ................................................................................................................................. |

4 |

Система прерываний........................................................................................................................ |

4 |

Микрокомандное управление ......................................................................................................... |

5 |

Часть 2. Вспомогательное программное обеспечение. .................................................................... |

7 |

Ассемблер микрокоманд ................................................................................................................. |

7 |

Симулятор (модель) процессора..................................................................................................... |

7 |

Литература ............................................................................................................................................ |

9 |

Приложение №1. Иерархия блоков ЭВМ. ....................................................................................... |

10 |

Приложение №2. Описание формата микрокоманд. ...................................................................... |

11 |

Приложение №3. Полный код микропрограммы. .......................................................................... |

15 |

Приложение №4. Исходный код ассемблера микрокоманд и сопутствующих утилит. ............. |

27 |

Ассемблер микрокоманд ............................................................................................................... |

27 |

Утилита mcd2mif ............................................................................................................................ |

40 |

Утилита labelmap2mif .................................................................................................................... |

43 |

Приложение №5. Исходный код симулятора.................................................................................. |

45 |

Раевский Сергей Сергеевич, группа 2103 |

2 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Введение

Целью курсового проекта являлась разработка традиционной архитектуры и схем ЭВМ с микропрограммным управлением в технологии ПЛИС.

Исходными данными являлись программная модель микро-ЭВМ MCS51 на уровне Ассемблера, перечень команд, выполняемых схемой, и элементная база Quartus.

Задание на курсовую работу - перечень команд, выполняемых схемой:

orl a, @Ri

orl a, #immediate

da a

mov direct, direct mov direct, @Ri

cjne @Ri, #immediate, rel

Раевский Сергей Сергеевич, группа 2103 |

3 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Часть 1. Описание схемы

Шинная организация

В соответствии с рекомендациями из методического пособия [1], за основу схемы взята шинная организация соединений. Через всю схему проходят две основные шины данных – BusB и BusC. Все пересылки между любыми регистрами выполняются через эти две шины. Так же, одной из основных шин является адресная шина BusA, которая используется для адресации памяти Data и регистров Sfr.

При помощи микрокомандного управления можно выставить на шину тот или иной регистр и записать это значение с шины в какой-либо регистр-приемник.

Иерархический принцип

Схема состоит из нескольких блоков, которые образуют собой иерархическую структуру. На верху структуры находится главный блок, который по сути и является микро-ЭВМ. Он подразделяется на несколько более простых блоков, которые, в свою очередь состоят из еще более простых. Такой подход к проектированию имеет множество преимуществ, таких как:

Возможность независимой разработки и отладки блоков (в том числе, различными людьми)

Возможность легко понимать схему, т.к. каждый блок в отдельности имеет простое устройство и небольшое количество составляющих частей.

Перспектива – создание конвейерной обработки инструкций, где необходимо выполнять несколько действий одновременно.

Полный список блоков и их иерархия приведены в приложении [1].

Синхронизация

В схеме использована 4-рехтактная синхронизация (4 такта на машинный цикл). Это сделано для того, чтобы исключить влияния переходных процессов в блоках на работу схемы в целом. За тактами закреплены следующие действия:

1)Первый такт – на шину ROMM выставляется адрес выполняемой микрооперации. На все шины данных выставляются нужные значения регистров.

2)Второй такт – происходит запись в регистры/память.

3)Третий такт – происходит инкремент счетчиков или загрузка их новыми значениями.

4)Четвертый такт – происходит предвыборка следующей микрокоманды (для проверки условия If).

Система прерываний

Раевский Сергей Сергеевич, группа 2103 |

4 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Реализованная в схеме двухприоритетная система прерываний совместима с системой прерываний MCS 51. Принцип ее работы заключается в постоянном опросе входов запросов на прерывание (INT0-INT6). Если на одном из входов присутствует высокий уровень и не выполняется обработка прерывания этого или более высокого приоритета, происходит запись номера прерывания во внутренний регистр-защелку и одновременное выставление флага IntrFlag, который используется в микропрограммном управлении. Приоритеты прерываний выставляются при помощи соответствующих битов регистра IP, а разрешение прерываний – при помощи битов регистра IE (как и в оригинальном MCS 51). Для обеспечения программного доступа к этим регистрам, в блок контроллера прерываний введены шины

BusA, BusB и BusSfr.

Микрокомандное управление

Всхеме используется микрокомандное управления для обеспечения функционирования вычислительного процесса. Процесс исполнения каждой инструкции процессора подразделяется на несколько стадий, называемых микрооперациями. Это может быть пересылка регистра в регистр, выполнение арифметических операций и т.п. - все, что необходимо для обеспечения требуемой функциональности. Для облегчения и ускорения процесса декодирования инструкции в схеме промена таблица соответствия кода инструкции

иадреса в памяти микрокоманд. Каждая микропрограмма обработки инструкции должна заканчиваться директивой Goto для перехода на метку выборки следующей инструкции. Полный список микрокомандных директив приведен в приложении [2] и в программном коде ассемблера микрокоманд.

Входе работы было реализовано в общей сложности 53 различные инструкции (47 помимо 6 входящих в задание), что было необходимо для всестороннего тестирования схемы

иполучения опыта работы с системой Quartus и опыта проектирования схем. Полный код микрокопрограммы приведен в приложении [3].

Рассмотрим принцип работу микропрограмм на примере инструкции mov direct, direct. Вот часть микрокода, отвечающая за исполнение этой инструкции:

1. .....

2.

3.@Next: # Next instruction

4.If=!IntrFlag;BusB16=Code;PC++;SetInstruction

6......

8.@$85: # mov dest_direct, src_direct

9.BusC16=Code;PC++;Wrk1Src=BusC;SetWrk1;Romm++

10.BusA=Wrk1;BusB8=Data[BusA];Wrk2Src=BusB;SetWrk2;Goto;Romm=@MOV_Wrk2Dest;

12. .....

13.

14.@MOV_Wrk2Dest:

15.BusC16=Code;PC++;Wrk1Src=BusC;SetWrk1;Romm++

16.BusA=Wrk1;BusB8=Wrk2;BusB->Data[BusA];Goto;Romm=@Next

(часть кода, не относящаяся к данной инструкции, пропущена)

Раевский Сергей Сергеевич, группа 2103 |

5 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Прокомментируем каждую строчку отдельно. В строках 1-2 пропущенный код инициализирует контроллер, записывая нули в регистры Acc, B и т.д., а так же, устанавливает SP в 0x07. Строчка 4 – выборка инструкции. Сначала происходит проверка условия отсутствия запроса на прерывание (директива If=!IntrFlag). Если прерываний не поступало, то микрооперация выполняется, иначе – пропускается. При выполнении микрооперации, на шину BusB подаѐтся выход памяти Code (в качестве адреса по умолчанию используется значение регистра PC). Директива SetInstruction записывает текущее значение с шины BusB в регистр IR (Instruction Register), а так же устанавливает счетчик микрокоманд в значение соответствующее адресу начала микропрограммы обработки инструкции. Директива PC++ инкрементирует программный счетчик (как уже было отмечено, запись регистров происходит на такте 2, а инкремент счетчиков – на такте 3, поэтому PC инкрементируется после записи в регистр IR).

После этого, в регистре-счетчике микрокоманд оказывается адрес начала микропрограммы mov direct, direct (метка @$85). В девятой строке на шину подается память кода по адресу PC++ (BusC16=Code;PC++;) и происходит запись байта с шины во временный регистр Wrk1 (Wrk1Src=BusC;SetWrk1;). Последняя директива (Romm++) увеличивает значение счетчика микропрограмм на 1 (для перехода к следующей микрооперации). В строке 10 происходит подача значения регистра Wrk1 на адресную шину BusA и подача значения из памяти Data по адресу с шины BusA через шину BusB в регистр Wrk2. Таким образом, эти две строки обеспечили выборку адреса источника и запись значения источника во временный регистр. После этого происходит безусловный переход на метку @MOV_Wrk2Dest (Goto;Romm=@MOV_Wrk2Dest;). Безусловные переходы в микрокомандах обеспечивают повторное использование кода различными микропрограммами и уменьшают требования к памяти микропрограмм.

По метке @MOV_Wrk2Dest находятся микрокоманды выборки адреса приемника и записи значения из регистра Wrk2 в приемник. Последняя микрокоманда содержит директиву Goto;Romm=@Next, которая делает переход по метке @Next для выборки следующей инструкции.

Раевский Сергей Сергеевич, группа 2103 |

6 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Часть 2. Вспомогательное программное обеспечение.

Ассемблер микрокоманд

Для облегчения перевода микрокоманд из текстовой форму в двоичную, был разработан ассемблер микрокоманд mca. Эта программа переводит микрокод из входного текстового файла в файлы промежуточные фалы .mcd (содержит микрокод) и .labelmap. (содержит адреса меток) Затем, две дополнительные утилиты создают из этих фалов файлы

.mif, пригодные для использования их в системе Quartus.

Ассемблер поддерживает метки, что облегчает создание и отладку микрокода. Метку можно объявить, если начать строку с символа @ (например, @Metka:). Объявления меток обязательно должны заканчиваться двоеточием. При использовании меток в тексте (в командах перехода) нужно так же начинать их имена с символа @. По принятому соглашению, метки вида @$XX: расцениваются как адреса точек входа в обработчик инструкции с шестнадцатеричным кодом XX (например, @$02: для ljmp). Адреса таких меток потом переводятся в таблицу, загружаемую в rom-память блока управления.

Ассемблер использует хорошо известную технику двойного прохода по тексту, где в первом проходе вычисляются адреса меток, а во втором - подставляются в текст.

Полный исходный код ассемблера mca и сопутствующих утилит на языке C# приведен в приложении [4].

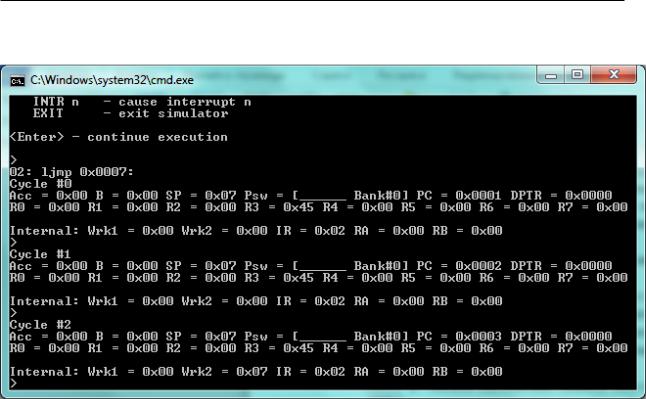

Симулятор (модель) процессора

Симулятор процессора позволяет быстро проверить работу микрокоманд, не прибегая к разработке/изменению схемы. Симулятор выполнен в виде консольной программы для системы Windows. Общение с пользователем происходит в текстовом режиме посредством текстовых команд. Такой интерфейс был выбран для ускорения процесса разработки.

Симулятор поддерживает следующие команды:

CODE b l – вывести l байт кода начиная с адреса b

DATA b l - вывести l байт памяти данных начиная с адреса b

SETR r d – установить регистр r значением d (r=a, b, psw, sp, pc, dptr, r0-r7).

При установке PC сбрасывается счетчик микрокоманд. REGS - вывести все регистры

SETD a - начать заполнение памяти data с адреса a SETC a - начать заполнение памяти code с адреса a INTR n – создать прерывание с номером n

EXIT – покинуть симулятор

<Enter> - продолжить исполнение микрокоманд

В симуляторе реализована поддержка всех инструкций из задания + инструкций ljmp и reti для работы с прерываниями. Для облегчения задания начальной программы и регистров симулятор поддерживает скриптовые файлы инициализации. В них можно пользоваться всеми приведенными выше командами, а заканчиваться файл должен символом «.» (обязательное условие). Исходный текст симулятора на языке C# и примера инициализационного скрипта приведен в приложении [5].

Раевский Сергей Сергеевич, группа 2103 |

7 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Окно симулятора в процессе работы показано на рисунке 1.

Рис. 1 Окно симулятора sim51

Раевский Сергей Сергеевич, группа 2103 |

8 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Литература

1.П.С. Довгий, В.И. Скорубский ПРОЕКТИРОВАНИЕ ЭВМ. Пособие к выполнению курсового проекта. Спб.: СПБГУ ИТМО 2009

2.Б.С. Иванов. Энциклопедия начинающего радиолюбителя. М: Патриот 1992

Раевский Сергей Сергеевич, группа 2103 |

9 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Приложение №1. Иерархия блоков ЭВМ.

BE_Mutilation – главный блок ЭВМ

Clock – схема делителя частоты синхронизации Core – микропроцессорное ядро

Code_xdata – блок памяти кода и XData

Code – блок памяти кода и регистров PCH/L Control – блок управления

Interrupts – блок контроллера прерываний (управляется непосредственно блоком

Control)

Interrupts-fetch – блок детектора прерываний

Datasfr – блок памяти Data и основных регистров Sfr (Acc, B, Psw, SP, DPTR) Datasfr_mem – блок памяти и регистров Sfr

Data_ram – блок памяти Ram (адреса 0..127)

Acc – Блок регистра-аккумулятора, сдвиговых операций и десятичной коррекции.

B_sp_sfr – блок регистров B и SP PSW – блок регистра PSW DPTR – блок регистров DPTR

Wrk_regs – регистры для хранения промежуточных значений

BusA_Selector – блок выбора значения для шины BusA (формирует так же адреса

R0..R7)

MulDiv – блок аппаратного умножения и деления (управляется блоком DataSfr) Alu – арифметико-логическое устройство

Bit – блок обработки битовых данных Cn_mcr – ПЗУ констант

Ports – блок портов ввода-вывода.

BIDI x4 – блоки соответствующих портов, имеющие одинаковое устройство.

Раевский Сергей Сергеевич, группа 2103 |

10 |

Кафедра Вычислительной Техники СПбГУ ИТМО

Приложение №2. Описание формата микрокоманд.

1)Блок Control/If (блок проверки условия выполнения микрокоманды) Поле If (5 бит).

Значение |

Описание |

00000 |

True |

00001 |

PSW.CF |

00010 |

PSW.AF |

00011 |

PSW.OV |

00100..01011 |

Wrk1[0]..Wrk1[7] |

01100 |

AluPSW.CF |

01101 |

AluPSW.AF |

01110 |

AluPSW.OV |

01111 |

Wrk1=0 |

10000 |

!IntrFlag |

10001-11111 |

Зарезервировано (True) |

2) Блок Control/Control (блок управления исполнением микрокоманд) |

|

Бит |

Действие |

0 |

увеличить счетчик микрокоманд на 1 |

1 |

выборка инструкции |

2 |

безусловный переход |

3-12 |

Адрес безусловного перехода |

Управление контроллером прерываний: |

|

13 |

очистить флаг прерывания |

14 |

завершить обработку прерывания |

15 |

выставить на шину BusB адрес обработчика в векторе прерываний |

3) Блок DataSfr (блок памяти дата и основных регистров Sfr)

Бит |

Действие |

0 |

Записать значение с шины BusB в память Data[BusA] |

1Записать значение с шины BusB в регистр Acc

2^ --- B

3^ --- SP

4инкрементировать SP

5декрементировать SP

6Записать значение шины BusB в регистр Psw

7инкрементировать DPTR

8Записать значение шины BusB в регистр DPL

9Записать значение шины BusB в регистр DPH 10-13 Выбор источника для шины BusB

0000 Null (использовать, если не требуется значение из этого блока)

0001 Wrk2

0010 Wrk1

0011 DPH

0100 DPL

Раевский Сергей Сергеевич, группа 2103 |

11 |