- •Курсовая работа

- •2. Разработка структуры цп

- •2.1 Структурная схема разрабатываемой системы

- •2.2 Структура регистровой памяти

- •2.3 Форматы данных, команд и способы адресации

- •2.3.1 Форматы данных

- •2.3.2 Формат команд

- •2.3.3 Способы адресации

- •2.4 Внутренняя организация

- •2.5 Основные алгоритмы функционирования

- •2.6 Алгоритмы выполнения отдельных операций.

- •2.7 Алгоритмы выполнения операций на шине.

2. Разработка структуры цп

2.1 Структурная схема разрабатываемой системы

Рис. 1

В курсовом проекте разрабатывается процессор, предназначенный для внутренних применений. В соответствии с техническим заданием, в структурной схеме системы (см. рис. 1) выделены раздельные шины данных и адреса. Команды программ хранятся в специальной памяти команд, а данные впамяти данных.

Процессор (рис. 2) имеет совмещенную шину адреса и данных (AD). Сигнал ALE используется для фиксации адреса на внешнем регистре-защелке, а пара сигналов HLD и HLDA – для реализации механизма захвата шины. Сигналы INT и INTA являются сигналами запроса и подтверждения прерывания. Если на корпусе имеется достаточное число свободных выводов, то целесообразно ввести несколько уровней запроса на прерывание.

Линии RD (Чтение), WR (Запись), BHE (Разрешение записи старшего байта) задают выполняемую на шине операцию. Линия FRAME используется для организации режима пакетного обмена между ОЗУ и внутренними кэшами. Появление данного сигнала на шине означает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним.

16

Рис. 2

Контакт READY (Готовность) служит для приема сигнала готовности от медленных внешних устройств. Назначение выводов питания, RESET и CLC (Синхронизация) очевидны.

Для реализации был выбран стандартный процессор на 68 выходов. Неиспользуемые выходы дублируют выходы на землю.

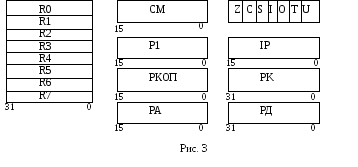

2.2 Структура регистровой памяти

В соответствии с техническим заданием

необходимо реализовать 8 тридцати двух

разрядных универсальных регистра общего

назначения. Каждому регистру условно

присвоено имяR0 –

R7(см. рис. 3).

соответствии с техническим заданием

необходимо реализовать 8 тридцати двух

разрядных универсальных регистра общего

назначения. Каждому регистру условно

присвоено имяR0 –

R7(см. рис. 3).

Регистры R0 – R7доступны для пользователя, как на чтение, так и на запись.

Регистры IP,Flags, СМ, Р1, РКОП, РК,РД и РАявляются системными (см. рис. 3).

Регистр IPпредставляет собой счётчик команд, в котором постоянно хранится адрес следующей команды, которую необходимо выполнить. Данный регистр недоступен для пользователя, однако существует один из способов его изменения – это команды перехода.

В регистре Flagsхранится состояние процессора (см. рис. 3).

Z– признак нулевого результата;

C– признак переноса из старшего разряда;

S– знак результата;

O– признак переполнения результата;

I– разрешение прерывания;

T– пошаговый режим;

U– режим супервизор/пользователь.

Регистр РК представляет собой регистр команд, в который записывается выполняемая команда.

Регистр РД – регистр данных.

Регистр РКОП – регистр кода операции.

Регистр РА– регистр адреса.

Регистры СМ и Р1 предназначены для хранения 1-го и 2-го операндов.

2.3 Форматы данных, команд и способы адресации

2.3.1 Форматы данных

Разрабатываемый процессор, в соответствии с техническим заданием, работает с тремя форматами данных: слово, двойное слово и число с плавающей точкой одинарной точности (см. рис. 3).

Р ис.

3

ис.

3

2.3.2 Формат команд

а) команды для арифметических операций

б) команды для работы с памятью

в) команды условных переходов

СА А1 СА

А2 РЕГ

КОП

а)

31 25 24

23 22 18 17 10 9

8 7 0

РЕГ А1

КОП 31 25 24

22

б

21 0

disp

КОП 31 25

в)

24 0

КОП- код выполняемой операции

Биты СА указывают способ адресации:

СА=00 – прямая адресация;

СА=01 – косвенная адресация;

СА=10 или СА1=11 – относительная адресация.

РЕГ– регистр-приемник (для варианта б) - номер регистра, содержащий в зависимости от кода операции либо адрес для сохранения значения ячейки ОП по адресуA1 в регистре, либо записи значения из РЕГ в ячейку ОП с адресомA1)

disp - смещение

А1 и А2 - регистры-источники данных