- •Министерство образования рф

- •Курсовая работа

- •Содержание.

- •1. Задание на проектирование

- •2. Введение

- •3. Форматы команд и типы данных

- •4. Типы команд

- •5. Форматы данных

- •5.1 Целые числа

- •5.2 Числа в формате с плавающей точкой (пт)

- •6. Формат команд

- •7. Структурная схема разрабатываемой системы

- •8. Регистровая модель процессора

- •9. Система команд процессора

- •7. Организация памяти

- •1 Гбайт 0.5 Гбайт 0.5 Гбайт 2 Гбайт

- •2 Гбайт

- •10. Структура внешних выводов процессора

- •11. Внутренняя организация центрального процессора

- •12. Структурная схема процессора

- •13. Алгоритм функционирования процессора

- •14. Временные диаграммы процесса считывания на шине

- •Заключение

7. Организация памяти

Поскольку модель памяти должна удовлетворять требованиям, предъявляемым ОС UNIX, то предлагается следующая модель организации виртуальной памяти.

Режим ядра

1 Гбайт 0.5 Гбайт 0.5 Гбайт 2 Гбайт

Режим

Режим

пользователя

2 Гбайт

Поскольку заданием задан размер памяти 4 Гбайт, то предлагается разделять имеющуюся память на следующие блоки. Память размером 2 Гбайт доступна процессам в пользовательском режиме. Страницы этой памяти являются кэшируемыми и перемещаемыми. Оставшаяся память объемом 2 Гбайт становится доступной только в режиме ядра (супервизора, системном). Предложено разделить ее на следующие блоки:

0.5 Гбайт под ядро ОС. Эта память является неперемещаемой (не используется переадресация через буфер TLB), но кэширование страниц разрешено.

0.5 Гбайт под порты ввода-вывода, так как по заданию работа с портами осуществляется как с ячейками памяти. Эта память является некэшируемой и неперемещаемой.

1 Гбайт памяти дополнительно доступно для процессов в системном режиме (режиме ядра). Эта память является кэшируемой и перемещаемой.

2 Гбайт памяти доступно для процессов в пользовательском режиме

10. Структура внешних выводов процессора

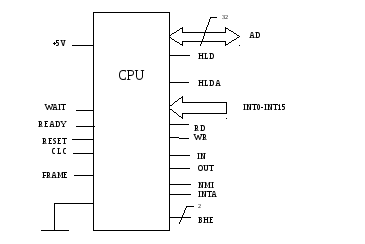

Рисунок 2.

Структура внешних выводов центрального процессора

На рисунке 2 приведена структура внешних выводов центрального процессора.

На схеме:

AD - 32-разрядная совмещенная шина данных и адреса;

HLD - реализация механизма захвата шины;

HLDA - разрешение на захват шины;

INT0 - INT15 - сигналы запросов на прерывание;

NMI - запрос немаскируемых прерываний;

INTA - сигнал подтверждения прерывания;

RD - сигнал чтения из памяти;

WR - сигнал записи в память;

IN - сигнал чтения из порта;

OUT - сигнал записи в порт;

READY - сигнал готовности от медленного внешнего устройства;

RESET - сигнал сброса;

CLC - сигнал синхроимпульсов;

+5V - +5V;

WAIT - используется для организации взаимодействия с внешним сопроцессором;

BHE - разрешение записи старшего полуслова, слова, двойного слова;

FRAME - организация режима пакетного обмена между ОЗУ и внутренними КЭШами.

Общее число выводов процессора составляет 65, поэтому процессор размещается в стандартном 68 выводном корпусе. Оставшиеся ножки могут быть использованы для дублирования контактов «Земля» или «Питание».

11. Внутренняя организация центрального процессора

Внутренняя организация центрального процессора приведена на рисунке 3.

Внутренняя организация центрального процессора

В процессоре реализован двухступенчатый конвейер обработки команд. Для двухступенчатого конвейера выделяются фаза выборки команды и фаза выполнения команды. Параллельно и асинхронно могут работать два процессора: процессор памяти и исполнительный процессор. Процессор памяти обеспечивает работу с памятью команд и памятью данных, а также с кэш-памятью. На исполнительный процессор возлагаются функции, связанные с дешифрацией и выполнением команд.