- •Министерство образования рф

- •Курсовая работа

- •Содержание.

- •1. Задание на проектирование

- •2. Введение

- •3. Форматы команд и типы данных

- •4. Типы команд

- •5. Форматы данных

- •5.1 Целые числа

- •5.2 Числа в формате с плавающей точкой (пт)

- •6. Формат команд

- •7. Структурная схема разрабатываемой системы

- •8. Регистровая модель процессора

- •9. Система команд процессора

- •7. Организация памяти

- •1 Гбайт 0.5 Гбайт 0.5 Гбайт 2 Гбайт

- •2 Гбайт

- •10. Структура внешних выводов процессора

- •11. Внутренняя организация центрального процессора

- •12. Структурная схема процессора

- •13. Алгоритм функционирования процессора

- •14. Временные диаграммы процесса считывания на шине

- •Заключение

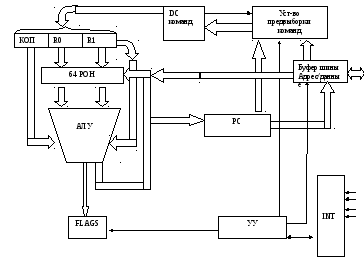

12. Структурная схема процессора

На рисунке 4 приведена структурная схема центрального процессора.

Р исунок

4.

исунок

4.

Структурная схема центрального процессора

Устройство предвыборки команд осуществляет опережающую выборку. Это позволяет избежать простоя процессора в циклах выборки команд. Устройство предвыборки считывает из памяти слова, начиная с адреса на 1 большего значения записанного в PC. Очередное слово из очереди подается на дешифратор. Освободившаяся позиция заполняется следующей командой.

Дешифратор команд получает слово от устройства предвыборки и дешифрует его. Преобразованный код записывается в регистр команд.

Регистр команд хранит команду, полученную от дешифратора.

Счетчик команд содержит адрес выполняемой в данный момент команды.

Устройство управления осуществляет координацию работы отдельных блоков процессора и осуществляет его взаимодействие с внешней шиной.

Контроллер равноприоритетных прерываний осуществляет выборку приходящих программных прерываний.

Буфер A/D служит для взаимодействия процессора с системной шиной и может переводить процессор в Z состояние, отключая его тем самым от шины.

АЛУ - выполняет операции над данными из РОНов. Используется для операций над числами с ФТ и ПТ.

Регистр флагов включает в себя 8 флагов 4 из которых соответствуют различным признакам результата.

13. Алгоритм функционирования процессора

На рисунке 5 приведён алгоритм функционирования центрального процессора.

Чтение

команды из ОЗУ

Дешифрация

Спец

операция

Фор.

адреса

Выб.

операндов Фор.

адреса

Вып

операции Зап

рез-та Вып

операции Зап

рез-та Вып.

операции Измен.

РС Фор.

адреса Изм

РС. Обработка

Рисунок 5.

Алгоритм функционирования центрального процессора

14. Временные диаграммы процесса считывания на шине

На рисунке 6 приведена временная диаграмма процесса считывания на синхронной шине.

Рисунок 6.

Временная диаграмма процесса считывания на синхронной шине

T1,T2,T3 – время цикла шины

~MREQ – указывает, что осуществляется доступ к памяти, а не к устройству.

~RD – указывает, что осуществляется чтение, а не запись.

~WAIT – чтобы ЦП не ожидал поступления данных, если память работает слишком медленно.

Обычно за раз передаётся одно слово. При использовании кэш памяти желательно сразу вызывать всю строку кэш-памяти (то есть 16 последовательных 32-битных слов). Часто передача блока может быть более эффективна, чем последовательная передача информации.

На рисунке 7 изображена такая же схема, как и на рисунке 6, только здесь появился дополнительный сигнал FRAME, появление которого означает начало транзакции, а снятие – то, что следующий цикл передачи данных является последним.

В данном примере считывание блока из 4 слов занимает 6 циклов вместо 12.

Рисунок 7.

Временная диаграмма процесса считывания на синхронной шине в пакетном режиме