- •«Санкт-Петербургский государственный электротехнический университет

- •Вариант задания: 2 (Традиционная архитектура)

- •1. Уточнение структуры системы

- •4. Формат команд.

- •5. Методы адресации:

- •6. Модель памяти и организация виртуальной памяти.

- •7. Реализация механизма прерываний.

- •8. Регистровая модель процессора и сопроцессора.

- •9. Команды процессора и сопроцессора

- •10. Временные диаграммы выполнения основных операций на шине.

- •11. Обобщенные алгоритмы функционирования процессора и сопроцессора.

- •Приложение 1. Руководство пользователя

- •Приложение 2. Текст программы

6. Модель памяти и организация виртуальной памяти.

Для традиционной архитектуры модель памяти должна удовлетворять требованиям, предъявляемым многопользовательской многозадачной ОС типа UNIX. При разработке модели памяти необходимо обеспечить размещение невыгружаемого ядра ОС в фиксированных ячейках памяти. Итак, графически модель памяти, используемой процессором в данной работе, можно представить следующим образом.

При этом все адресное пространство разбивается на блоки по 4Кбайт, называемые страницами. Каждый абсолютный 32-х битный адрес байта в памяти условно делится на две части: младшие 12 битов – это номер байта в нужной странице, старшие 20 битов интерпретируются как номер страницы с нужным байтом. Идея виртуальной памяти состоит в том, что страницы с последовательными номерами не обязательно должны последовательно размещаться в памяти. Более того, поскольку программы практически никогда не используют все адресное пространство процессора, то некоторые страницы вообще могут отсутствовать в памяти. Для реализации этого принципа в процессоре должна быть предусмотрена соответствующая аппаратная поддержка. Он должен транслировать обращение программы к данным по какому-то адресу в обращение к реальной физической памяти. Понятно, что тогда нужно точно знать, какая страница настоящей физической памяти хранит нужную страницу виртуального адресного пространства программы. Для этого в оперативной (физической) памяти должна быть создана специальная структура данных, называемая таблицей страниц. Каждый ее элемент соответствует какой-либо странице виртуального адресного пространства, а число этих элементов равно их (страниц) количеству. При адресации программы по какому-либо виртуальному адресу, процессор по номеру его страницы ищет элемент с таким же номером в таблице страниц и считывает оттуда нужные данные. О структуре каждого элемента я скажу чуть ниже, а сейчас замечу, что число страниц виртуальной памяти может превышать число страниц в физической оперативной памяти. Более того, каждой запущенной программе выделяется число виртуальных страниц, соответствующее максимальному размеру виртуального пространства, с которым программе можно работать. Если программа захочет использовать страницу в своем адресном пространстве, под которую не отведена реальная память, то возникнет исключительная ситуация и процессор запишет "проблемный" адрес в специальный регистр BVA (Bad Virtual Address), а указатель на элемент в таблице страниц в ОЗУ. Далее процессор перейдет к выполнению обработчика исключений, обычно принадлежащего ОС. ОС отведет для страницы участок физической памяти, а если она будет вся занята, то можно другую страницу переписать в файл на диске, пометить в таблице страниц, что ее нет, свободное место отдать нашей текущей странице, записать этот факт в таблицу страниц. Обработчик исключения будет закончен и процессор перейдет к повторному выполнению операции обращения к памяти программой, которая ничего не заметит. Но ведь при наличии данного механизма в памяти можно держать несколько программ, причем у них будет одинаковая модель адресного пространства, и все программы будут в него загружаться по одинаковому адресу. Для этого нужно поставить в соответствие каждой программе свою таблицу страниц и загружать ее начальный адрес в физической памяти в специальный регистр, который я называю PTP (Page Table Pointer).

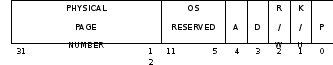

Каждый элемент таблицы страниц имеет следующую структуру.

Описание битов атрибутов и полей элемента таблицы страниц:

1) Поле "PHYSICAL PAGE NUMBER" хранит, как видно его названия, номер физической страницы, то есть номер одного из 4 Кбайтных кусочков, на которые условно разбита установленная в системе оперативная память. На обозначенный таким образом участок оперативной памяти и будет отображается виртуальная страница, элемент которой мы рассматриваем. Понятно, что при такой организации содержимое виртуальных страниц в оперативной памяти может храниться не где попало, начиная не с любого байта, а только с байтов, чьи физические адреса кратны 4 Кбайтам. Рассматриваемое поле имеет значение только в том случае, если страница реально присутствует в оперативной памяти, то есть бит P ее элемента таблицы страниц равен "1".

2) Бит-атрибут P (PRESENT) равен "1", если виртуальная страница хранится в оперативной памяти (то есть странице поставлен в соответствие ее кусочек), или "0" в противном случае. Данный бит проверяется процессором при попытке программы обратится по виртуальному адресу, попадающему в рассматриваемую виртуальную страницу и при его (бита) нулевом значении возникает исключение отсутствующей страницы. (Подробно об исключениях – в следующем разделе.)

3) Бит-атрибут K/U (KERNEL/USER) равен "1", если прикладной программе, работающей в режиме пользователя, разрешено обращаться к данной виртуальной странице. В противном случае работать с ней оказывается возможным только находясь в режиме ядра. При нарушении прав доступа процессор генерирует исключение страничной защиты.

4) Бит-атрибут R/W (READ/WRITE) равен "1", если разрешена запись в страницу, в противном случае к ней можно обращаться только по чтению. Опять же, если что, то процессор генерирует исключение обращения к странице.

5) Бит-атрибут D (DIRTY) устанавливается в "1" процессором при каждой записи в страницу, что говорит ОС о необходимости ее сохранения, поскольку страница была модифицирована. Считается, что ОС должна обнулять этот бит после сохранения страницы во внешней памяти.

6) Бит-атрибут A (ACCESED) устанавливается в "1" процессором не только в случае записи в страницу, как бит D, но и при чтении из нее. Помогает ОС отличить используемые в настоящий момент страницы от неиспользуемых. Обычно при нехватке оперативной памяти ОС сбрасывает этот бит у всех страниц, и через некоторое время проверяет его. Страницы с единичным значением этого бита нельзя переносить во внешнюю память, так как с ними осуществляется работа.

7) Поле "OS RESERVED" процессором никак не используется. ОС может применять его как захочет. К примеру, она может хранить тут "возраст" страницы в некоторых условных единицах. + данной технологией пользуются разработчики Microsoft(резервирование байтов).

При такой организации виртуальной памяти возникает проблема – оперативная память слишком медленная, чтобы каждый раз читать из нее элементы таблицы страниц. Поэтому при первом обращении к какой-то странице описывающий ее элемент из таблицы страниц помещается в буфер ассоциативной трансляции TLB (Translation Lookaside Buffer). В большинстве процессоров он представляет собой четырехканальный наборно-ассоциативный кэш на 64 (в данной работе) и более элементов таблицы страниц. Если свободных мест в TLB нет, то приходится новый элемент писать в уже занятую позицию, причем выбор ее осуществляется случайным образом. Ясно, что при перезагрузке PTP буфер TLB процессору необходимо очищать. Если ОС что-то меняет в таблице страниц, то она обязана перезагрузить регистр PTP (очистив тем самым TLB), даже если адрес таблицы остается прежним.

Очень важно, что механизм виртуальной адресации предназначен не только для увеличения числа доступной программам памяти, но и для изоляции их друг от друга. В этой связи следует упомянуть, что в разрабатываемом процессоре, как и во многих других, есть два режима работы: режим пользователя и режим ядра. В режиме ядра на программу не накладываются какие-либо ограничения, и она может делать все, что захочет. Это, прежде всего, необходимо для кода и данных ядра ОС, а также для кода и данных загружаемых ею модулей. Находясь в памяти, ОС имеет возможность работать с устройствами через порты ввода-вывода, обрабатывать прерывания и исключения, организовывать виртуальную память для себя и загружаемых ею прикладных программ и прочее. Данные возможности, а также некоторые другие, нельзя использовать прикладным программам, обычно работающим в режиме пользователя. Если программа пытается выполнить недопустимые действия, то процессор сгенерирует исключение защиты и передаст управление ядру ОС, с тем чтобы оно разобралось с возникшей ситуацией. Но не только неразрешенные в режиме пользователя команды могут стать причиной исключения защиты. Дело в том, что в каждом элементе таблицы страниц хранится информация и о правах доступа к этой странице. То есть прикладным программам не разрешается работать с памятью, используемой ОС под свои нужды. Обращение по неразрешенным адресам тоже вызовет исключение страничной защиты. Исходя из изложенных ограничений становится совершенно ясно, что модели памяти для ОС, работающей в режиме ядра и прикладных программ, работающих в режиме пользователя, скорее всего будут отличаться. В задании на данную курсовую работу сказано о необходимости обеспечить поддержку многозадачной ОС типа UNIX. Графические представления моделей памяти, используемой этой ОС, я уже приводил в начале этого раздела. Теперь настало время объяснить, каким же образом ОС может реализовать данные модели при применении разрабатываемого RISC-процессора. Общая идея виртуальной памяти и механизмов ее защиты была изложена выше, но надо пояснить, на какие же части делится виртуальная память в разных режимах работы процессора, каков их размер, как осуществляется работа с ними. Как я уже вскользь упоминал, в задании мне предписано использовать совмещенную шину адреса и данных, разрядностью 32 бита. В связи с тем, что разрядность регистров процессора равна 64 бита, то при обращении к памяти при косвенной адресации со смещением значащей будет являться только младшая половина используемого в команде регистра. Точнее, к этому регистру (как к числу без знака) будет сначала прибавлено смещение, а уже из полученной суммы будут взяты младшие 32 бита как адрес нужной ячейки памяти, то есть можно сказать, что оперативная память как бы свернута в кольцо – при переполнении в ту или иную сторону обращение произойдет к другому ее концу. Итак, при отсутствии каких бы то ни было ограничений (правильно построенная модель памяти), процессор в принципе способен адресовать вплоть до 4 Гбайт памяти (исходя из разрядности шины адреса). В разных режимах работы процессора это адресное пространство разбито на части тем или иным образом. В режиме пользователя все довольно просто. Для каждой прикладной программы ОС формирует виртуальное адресное пространство размером 2 Гбайт, причем оно располагается в нижней, "младшей" половине 4-х Гбайтного адресного диапазона. Если программа попытается превысить выделенный ей диапазон, то возникнет исключение страничной защиты, далее все зависит от ОС. Несколькими строчками выше я написал "ОС формирует". Надо разобраться, как она может это сделать. Механизм защиты и отображения виртуальных адресов памяти на физические мной уже подробно описан. Но, можно вспомнить, что в задании есть такой пункт "размер прямоадресуемой памяти", и для этого варианта его значение равно 512 Мбайт. Отсюда следует вывод – переадресация процессором будет использоваться не всегда. Должен, согласно заданию да и здравому смыслу (при сбросе ведь процессор должен адресоваться к командам, а таблицы страниц еще нет), присутствовать 512 Мбайтный диапазон адресов (в виртуальном адресном пространстве), которые должны быть жестко "привязаны" к первым 512 Мбайтам физической оперативной памяти. Надо выбрать место размещения этого диапазона. Ясно, что он должен располагаться выше ("старше") 2-х Гбайтов виртуальной памяти пользовательского режима, поскольку прикладные программы не должны иметь к нему доступ. Более того, лучше разместить его в самом конце адресного пространства, тогда, во-первых, в таблице страниц не будет "дырки", во-вторых, при сбросе процессоры часто устанавливают свой счетчик команд PCR на самый конец адресного пространства, и, поскольку к этому времени таблица страниц еще не сформирована и PTP не инициализирован, этот адрес должен входить в прямоадресуемую память и принадлежать BIOS. Итак, прямоадресуемая память всегда находится в диапазоне 3,5 – 4,0 Гбайт, обращение к ней разрешено исключительно в режиме ядра. При обращении к адресам ниже 3,5 Гбайт используется переадресация через таблицу страниц размером 3,5 Мбайт, начало которой хранится в регистре PTP. Если эта ОС типа UNIX, то для реализации принятой в ней модели памяти пользовательского режима обращение к нижней части виртуальной памяти ("Сегмент 0" – 2 Гбайт) в этом режиме должно быть разрешено, а к оставшимся 1,5 Гбайт – запрещено (для запрещения нужно сбросить соответствующий бит в нужных элементах таблицы страниц). Самое интересное, что при переходе в режим ядра (скорее всего, по прерыванию или исключению) в таблице страниц ничего не нужно будет менять, также как не придется менять и содержимое регистра PTP, поскольку полученная модель памяти в точности будет соответствовать структуре модели памяти, используемой в режиме ядра ОС типа UNIX, а именно в ней будут присутствовать следующие сегменты: "Сегмент 1" (младшие 2,0 Гбайт) – это виртуальная память прикладной программы, "Сегмент 2" (1,5 Гбайт) – виртуальная память для модулей ОС, "Сегмент 3" (старшие 512 Мбайт) – прямоадресуемая память под ядро ОС, BIOS, таблицы страниц, таблицу векторов прерываний (об этом в следующем разделе) и прочие системные нужды.