- •«Санкт-Петербургский государственный электротехнический университет

- •Вариант задания: 2 (Традиционная архитектура)

- •1. Уточнение структуры системы

- •4. Формат команд.

- •5. Методы адресации:

- •6. Модель памяти и организация виртуальной памяти.

- •7. Реализация механизма прерываний.

- •8. Регистровая модель процессора и сопроцессора.

- •9. Команды процессора и сопроцессора

- •10. Временные диаграммы выполнения основных операций на шине.

- •11. Обобщенные алгоритмы функционирования процессора и сопроцессора.

- •Приложение 1. Руководство пользователя

- •Приложение 2. Текст программы

10. Временные диаграммы выполнения основных операций на шине.

При создании этого раздела у меня встала проблема выбора: сделать так, чтобы точно работало, но медленно, или попытаться сделать побыстрее, но тогда возникают некоторые проблемы. О чем я говорю ? В идеале мой процессор должен выполнять одну команду за один такт. В худшем случае, ему придется выполнять последовательность команд для работы с памятью и внешними устройствами, причем их может быть больше, чем длина буфера команд. Получается, что процессору за каждый такт придется выполнять два шинных цикла: считать саму команду, а потом выполнить ее. Ясно, что это невозможно. Ситуация усугубляется тем, что у меня совмещенная шина адреса и данных. То есть на шину нужно будет выставить сначала адрес, а потом данные. И это за пол такта. Невыполнимая задача. Можно либо смирится с тем, что процессор будет иногда простаивать, либо можно в несколько раз увеличить частоту шины. Второй вариант предпочтительней, потому что скорость работы всей системы станет выше. Во сколько раз эту частоту повышать ? Можно в 4 раза, тогда один цикл обмена с памятью и внешними устройствами будет занимать 2 такта, но вот если попытаться выполнить один цикл обмена по совмещенной шине за один такт, то частоту шины можно будет поднять только в два раза относительно частоты процессора, или же вообще не поднимать, тогда процессор хотя и будет простаивать, но меньше, чем при двухтактной длительности цикла обмена. Я попытаюсь сделать именно так, чтобы цикл обмена с памятью занимал один такт. Следует отметить, что хотя я и ориентируюсь на процессор Intel 8086, но все же шинные циклы делаю я сам, поэтому они могут и скорее всего будут отличаться от стандартных. Но в задании не указано, что они должны соответствовать какому-либо стандарту. Но ближе к делу.

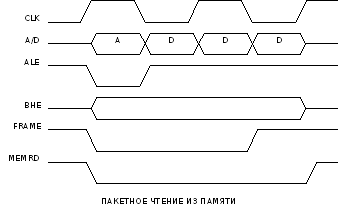

Циклы чтения и записи при обмене с памятью и с внешними устройствами очень похожи. В первом случае используются сигналы MEMRD и MEMWR, во втором – IORD и IOWR. Сами циклы чтения и записи тоже практически идентичны. В первом случае данные на шину выставляются оперативной памятью или внешними устройствами (сигналы MEMRD и IORD), во втором – процессором или сопроцессором (сигналы MEMWR и IOWR). Исходя из сказанного, имеет смысл привести диаграмму только для одной операции, а не четырех. Вот как выполняется цикл чтения памяти. В начале цикла, по фронту CLK, процессор выставляет сигналы ALE (сообщает, что по шине будет передаваться адрес) и BHE (помогают определить, сколько байт данных нужно передать), а также одновременно с ними сигнал MEMRD. Потом выставляет 32-х разрядный адрес. По спаду сигнала CLK, процессор убирает сигнал ALE, сообщая памяти, что готов принять данные. Память держит данные на шине до тех пор, пока по следующему фронту процессор либо снова не установит сигнал ALE, либо не уберет сигнал MEMRD. В течении всего цикла чтения, не упомянутые мною сигналы управления должны иметь высокий уровень, то есть не быть активными. Что касается сигнала READY, то если он активен (равен нулю), то процессор ждет один или несколько тактов, пока этот сигнал не пропадет (это относится к медленным внешним устройствам, так как только они изменяют READY, а в остальных случаях он всегда не активен, то есть равен единице). И еще замечание, относящееся ко всем диаграммам: горизонтальные линии, которые располагаются в середине между уровнями нуля и единицы говорят о том, что на линии в этот момент могут быть любые значения сигналов, но они не относятся к рассматриваемому циклу.

Вот еще одна диаграмма, но уже для пакетного чтения памяти. Процессор выставляет сигнал FRAME, что означает начало пакетного обмена, а перед окончанием (за 1 цикл) снимает этот сигнал. Особенность работы памяти в том, что она принимает адрес только в самом начале пакетного обмена, а потом передает подряд расположенные данные. То есть, по сути, можно за один такт передать в два раза больше данных, чем при обычнрм обмене. Это позволяет отчасти решить проблему нехватки пропускной способности шины, о которой я уже говорил выше.

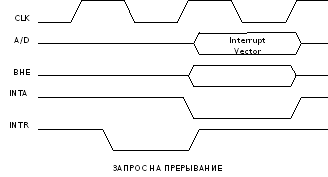

Теперь надо проиллюстрировать процесс передачи запроса на прерывание от внешнего устройства к процессору. При прерывании устройство выставляет сигнал INTR на шину. Процессор заканчивает текущую операцию и выставляет сигнал INTA, подтверждающий запрос на прерывание. Устройство, получив этот сигнал, снимает сигнал INTR и выставляет на шину вектор прерывания. Вот эта диаграмма.

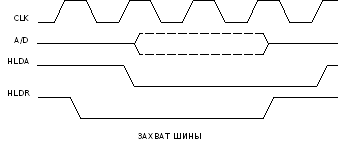

Осталось показать, как устройство может попросить процессор предоставить ему возможность захватить шину. Если устройство хочет захватить шину, то оно выставляет сигнал HLDR. Процессор заканчивает текущий цикл обмена и передает управление устройству, потребовавшему шину, выставляя сигнал HLDA. Устройство начинает обмен с любым другим устройством (или с памятью) причем оно является ведущим и, соответственно, само выставляет все необходимые сигналы.

Что касается процессора и сопроцессора, то в некоторых системах они обмениваются данными по шине, используя операции ввода-вывода. Но у меня нет таких инструкций обмена, поэтому процессор и сопроцессор в моей работе через шину не взаимодействуют.