- •1. Техническое задание

- •1.1. Предмет проектирования

- •1.2. Общие требования к разрабатываемому процессору

- •1.3. Исходные данные для курсового проектирования

- •1.4. Результаты проектирования

- •2. Последовательность выполнения курсового проекта

- •2.1. Общая последовательность

- •2.2. Разработка архитектуры цп

- •2.2.1. Уточнение структуры системы

- •2.2.2. Разработка архитектуры внешних выводов

- •2.2.3. Выбор форматов данных

- •2.2.5. Выбор форматов команд

- •2.2.7. Внутренняя организация

- •Р1, р2

- •Алу _

- •Y2 y9 y13, y14

- •3. Алгоритмы выполнения отдельных операций

- •3.1. Выборка команды оПкоманд y1 y2 x1 y4 ram d fl a rdwr rgрд

- •3.2. Обработка адресной части команды

- •Память данных

- •3.4. Передача управления

- •Flags fl

2.2. Разработка архитектуры цп

2.2.1. Уточнение структуры системы

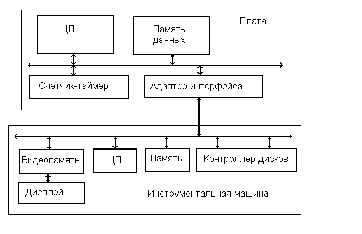

Рис. 1

Обобщенная структура процессора, соответствующая гарвардской архитектуре, приведена на рис. 1. Она представляет собой одноплатную ЭВМ, предназначенную для встроенных применений. На плате размещаются: ЦП, память данных, счетчик-таймер, адаптер интерфейса. Кроме того, на плате могут размещаться вспомогательные схемы и интерфейсные схемы для подключения внешних устройств (на рис. 2 эти схемы не показаны).

Разрабатываемая плата не имеет собственной дисковой памяти, дисплея и клавиатур. Предполагается, что разработка и отладка программного обеспепечения осуществляются на инструментальной машине с использованием кросс-систем программирования. В качестве инструментальной машины может использоваться, например рабочая станция, имеющая в своем составе дисплей, клавиатуру, дисковую память и т. п.

2.2.2. Разработка архитектуры внешних выводов

Для

разрабатываемого процессора выбираем

стандартный корпус с 132 выводами.

Frame

BHE

OUT

RD

INTA

WR

INT

HLDA

HLD

ALE

64

AD

CPU

+5V

Reset

CLC

Рис. 2

Процессор (рис. 2) имеет совмещенную шину адреса и данных (AD), разрядностью 64. Сигнал ALE используется для фиксации адреса на внешнем регистре-защелке, а пара сигналов HLD и HLDA – для реализации механизма захвата шины. Сигналы INT и INTA являются сигналами запроса и подтверждения прерывания. Если на корпусе имеется достаточное число свободных выводов, то целесообразно ввести несколько уровней запроса на прерывание. Линии RD (Чтение), WR (Запись), IN (Ввод), OUT (Вывод), BHE (Разрешение записи старшего байта) задают выполняемую на шине операцию. Линия FRAME используется для организации режима пакетного обмена между ОЗУ и внутренними кэшами. Появление данного сигнала на шине означает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним. Оставшиеся выводы используем для дублирования питания и заземления.

2.2.3. Выбор форматов данных

Разрабатываемый процессор, в соответствии с техническим заданием, работает с двумя форматами данных: байт и слово (см. рис. 2).

Числа

с фиксированной точкой представляют

собой целые со знаком или без него. Целые

числа со знаком представляются в

дополнительных кодах. 6 0 S Байт 7 14 0 S Слово 15

Рис. 2

Адреса представляются в виде целых чисел без знака.

2.2.4. Определение модели памяти и структуры регистровой памяти

В соответствии с техническим заданием необходимо реализовать 64 шестнадцати разрядных функционально ориентированных регистра общего назначения. Каждому регистру условно присвоено имя R0 – R63. Все регистры общего назначения разделены на 3 группы по своей функциональной ориентации.

R32

R62

R63

R0

R1

.

.

R30

R31

R33

.

.

R60

R61

R54

R55

16

0

16

0

16

0

R0 – R15 регистры для хранения данных

R32 – R55 регистры для хранения базовых адресов

R60 – R63 регистры для хранения индексов

IP

15

0

Flags

РК

63

0

РД

15

0

РА

15

0

РКОП

15

0

Р1

15

0

Р2

15

0

Р3

15

0

Р4

15

0

Регистры R0 – R63 доступны для пользователя, как на чтение, так и на запись.

Регистры IP, Flags, Р1-P4, РКОП, РК, РД и РА являются системными .

Регистр IP представляет собой счётчик команд, в котором постоянно хранится адрес следующей команды, которую необходимо выполнить. Данный регистр недоступен для пользователя, однако существует один из способов его изменения – это команды перехода.

В регистре Flags хранится состояние процессора (см. рис. 3).

Z – признак нулевого результата;

C – признак переноса из старшего разряда;

S – знак результата;

O – признак переполнения результата;

I – разрешение прерывания;

T – пошаговый режим;

U – режим супервизор/пользователь.

Регистр РК представляет собой регистр команд, в который записывается выполняемая команда.

Регистр РД – регистр данных.

Регистр РКОП – регистр кода операции.

Регистр РА– регистр адреса.

Регистры Р1, Р2, Р3 и Р4 это внутренние регистры АЛУ. Они предназначены для хранения 1-го и 2-го операндов, а также результатов и флагов выполнения операции. Это внутренние регистры и они недоступны для программиста.