- •1. Техническое задание

- •1.1. Предмет проектирования

- •1.2. Общие требования к разрабатываемому процессору

- •1.3. Исходные данные для курсового проектирования

- •1.4. Результаты проектирования

- •2. Последовательность выполнения курсового проекта

- •2.1. Общая последовательность

- •2.2. Разработка архитектуры цп

- •2.2.1. Уточнение структуры системы

- •2.2.2. Разработка архитектуры внешних выводов

- •2.2.3. Выбор форматов данных

- •2.2.5. Выбор форматов команд

- •2.2.7. Внутренняя организация

- •Р1, р2

- •Алу _

- •Y2 y9 y13, y14

- •3. Алгоритмы выполнения отдельных операций

- •3.1. Выборка команды оПкоманд y1 y2 x1 y4 ram d fl a rdwr rgрд

- •3.2. Обработка адресной части команды

- •Память данных

- •3.4. Передача управления

- •Flags fl

3. Алгоритмы выполнения отдельных операций

3.1. Выборка команды оПкоманд y1 y2 x1 y4 ram d fl a rdwr rgрд

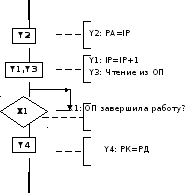

На

рис. 8 приведён фрагмент структуры

процессора, относящийся к выборке

команды, а на рис. 9 – соответствующая

ей микропрограмма.

Y3

Рис. 3

У разрабатываемого процессора разрядность команды и разрядность ячейки памяти в которой она хранится совпадают. Исходными данными является адрес размещения команды в памяти ЭВМ, который хранится в счётчике адреса команд IP. Содержимое IP передаётся в регистр адреса РА оперативной памяти, осуществляется чтение из оперативной памяти команд хранящейся в ней информации в регистр даных РД. После чтения из ОП, требуемая команда будет находиться в регистре РД. Далее осуществляется передача содержимого РД на РК.

Рис. 4

3.2. Обработка адресной части команды

Рис. 5

РК

A

RG

ИР

ПА

Дш

0

1

2

3

DC

1

2

R60

X0

RG

R63

X3

RG

SE0

SE7

K

MUX

D0

.

.

D7

D8

E

E

СмИ

SM

D

РА

RG

D

E

Y8

Y7

Y5

Y6

X2

Aисп

Если

не используется прямая или непосредственная

адресация, то необходимо вычислить

исполнительный адрес при помощи

относительной адресации. Для реализации

относительной адресации в процессоре

предусмотрено 4 индексных регистра R60

– R63.

На сумматоре производится сложение адресной части РК с индексом, находящимя в одном из индексных регистров R60 – R63. Для определения номера индексного регистра, в команде отведены поля ИР1, ИР2, ИР3. После этого исполнительный адрес заносится в РА. Структурная схема и микропрограмма приведены на рис. 10 и рис. 11.

3.3. Арифметические и логические операции

Рис. 6

РК

A3

RG

A1

INS

K

MUX

D1

SE3

SE2

РА

RG

D

E

Y9

Память данных

RAM

D

END

A

RD

WR

RG

РД

Y3

Y16

АЛУ

ALU RG

RG3

Р3

ST

RG4

Р4

INS

RG2

Р2

D

E

RG1

Р1

D

E

FL

Y13

Y14

Y15

X3

A2

SE1

D2

D1

Y10

Y12

Y11

Y9,Y10

X1

Y13

Y9,Y10: РА=А1

X1: ОП завершила работу?

Y13: Р1=РД

Y3

Y9,Y11

Y3

X1

Y14

1

1

Y15

X3

Y9,Y12

X1

Y16

Y3: Чтение из ОП

Y9,Y11: РА=А2

Y14: Р2=РД

Y15: Запуск АЛУ

X3: АЛУ закончило работу?

Y9,Y12: РА=А3

Y16: Запись в ОП

Рис. 7

X1

В регистре команд уже находится очередная считанная команда в результате выборки команды. На первом этапе из памяти данных читается первый операнд, адрес которого находится в поле А1 регистра команд (то есть в текущей выполняемой команде). Операнд из РД передаётся в регистр Р1 АЛУ. Аналогично из памяти данных считывается второй операнд и заносится в Р2 АЛУ. Далее запускается устройство управления АЛУ. В соответствии с кодом операции, поступающим на АЛУ из РК, АЛУ выполняет требуемую микропрограмму. В процессе выполнения микропрограммы на Р4 АЛУ формируется результат операции, а на Р3 фиксируются признаки результата операции (равенство нулю, переполнение, перенос…). По завершении выполнения операции, АЛУ вырабатывает сигнал X1. После этого результат выполнения операции из Р4 помещается в ОП по адресу, указанному в поле А3 регистра команд.