- •1.История развития цифровой вычислительной техники. Цвм 1-го и 2-го поколения.

- •История развития цвм 3-го и последующих поколений.

- •Понятие об архитектуре системы. Cisk и risk системы

- •4. Классификация цвм

- •Организация операционных устройств.

- •Организация операционной части (оч).

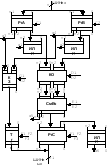

- •Пример структурной организации оч, реализующей логические операции.

- •Организация интегральных операционных частей (оч)

- •Пример структурной реализации бму серии к584 ву1.

Пример структурной организации оч, реализующей логические операции.

Error: Reference source not found

Вершину 1 можно реализовать, используя регистры (для выполнения двуместных операций потребуется два регистра). Для выполнения логический операций выбирается соответствующий цифровой узел (блок конъюнкторов, дизъюнкторов, сумматор по модулю два и т.д.). Для сохранения результата можно использовать регистр, но в отличие от входных регистров, у него желательно иметь отключаемый выход, т.к. выходная шина ОЧ может подключатся на магистраль, к которой присоединены выходные шины других ОЧ

Error: Reference source not found

В качестве входных регистров используются РгА и РгВ – это параллельные n-разрядные регистры с неотключаемым выходом; могут быть различных типов, например, с начальным сбросом (C1, D1) и приемом (C2, D2), либо с параллельной записью без начальной установки. Требуемый набор логических операций выполняется в блоке логических операций (БЛО). Каждая операция активизируется по соответствующей микрооперации (E1, E2,... и т.д.). Блок комбинационный, не хранящий результат, поэтому для двуместных операций должен иметь две параллельные шины. Результат на выходе БЛО присутствует, пока на входах есть операнды и на управлении есть сигнал микрооперации. Поэтому для сохранения результата необходим выходной регистр РгС, который, в отличие от входных регистров, будет иметь дополнительную микрооперацию – выдача (открытие выхода). Логика работа и последовательность действий ОЧ описывается структурной схемой алгоритма (ГСА – граф-схема алгоритма) в обозначении микроопераций (E1, E2,..., F1, F2 и т.п.). Для этой цели предварительно составляется таблица расшифровки МО и таблица описания ЛУ.

|

МО |

Описание |

|

|

D1, F1 |

Сброс регистра | |

|

C1 |

| |

|

D2, F2 |

Запись в регистр | |

|

C2 |

| |

|

F3 |

Чтение с открытием выхода РгС | |

|

E1 |

ЛО... | |

|

E2 |

ЛО... |

Error: Reference source not found

Каждая вершина ГСА соответствует одному микрокомандному циклу, а весь граф соответствует микропрограмме. Отображение исходного алгоритма в ГСА неоднозначно и зависит от выбранных систем элементов и структуры. В нашем случае регистры требовали начального сброса. Ввод операндов разнесен на две вершины (2 и 3), что связано со структурой подключения входной шины, по которой невозможно сразу передать два параллельных операнда. В тоже время в 3-ей вершине ГСА, учитывая возможности элементов и узлов, ввод второго операнда совмещен с выполнением операции и фиксацией результата.

ГСА должен сопровождаться двумя таблицами:

- таблица расшифровки микроопераций.

- таблица описания логических условий.

В нашем примере ветвлений нет, следовательно таблица описания ЛУ не нужна. Каждая вершина ГСА содержит сигналы из поля микроинструкций соответствующей микрокоманды. Если этих сигналов несколько в микроинструкции, то говорят о совместной микрооперации. Если одна, то микрооперация несовместна.

8, Пример разработки операционной части из дискретных компонент для реализации операции суммирования чисел в прямых кодах.

Пример реализации ОЧ для суммирования чисел с фиксированной запятой в прямых кодах.

Error: Reference source not found

Описание буфера операций

|

Микрооперации |

Примечание |

|

|

C1, C2, F1, M1 |

Приём в Рг | |

|

D1 |

Прямая передача | |

|

D2 |

Перекрёстная передача | |

|

E1 |

Суммирование | |

|

E2 |

Вычитание | |

|

G1 |

Передача знака А | |

|

G2 |

Передача знака В | |

|

M2, F2 |

Выдача результата | |

|

F3, M3 |

Сброс Рг С |

|

Расшифровка логических условий |

| |

|

Логические условия |

Примечание |

|

|

1 |

=0, если А=0 =1, если А0 | |

|

2 |

=0, если В=0 =1, если В0 | |

|

3 |

=0, если А≥0 =1, если А0 | |

|

4 |

=0, если В≥0 =1, если В0 | |

|

5 |

=0, если ()≥0 =1, если иначе | |

|

6 |

=0, если ()=0 =1, если иначе. | |

Error: Reference source not found

Структурная схема операционной части (ОЧ) может быть реализована в нескольких вариантах, что зависит от налагаемых условий по быстродействию, использованию элементной базы, стоимости реализации и прочее.

В рассматриваемом примере для удешевления

используется одноформатная шина ввода,

что приводит к последовательному воду

данных в вершинах С1 (1 вершина) и С2 (2

вершина) (снижается быстродействие).

Сравнение знаков в примере выполняется

программой, сначала знак А (8 вершина),

потом знак В (8 или 9 вершина). Если бы в

схему был дополнительно введён сумматор

по модулю 2, то сравнение знаков произвелось

бы за 1 такт. Если один из операндов равен

нулю, то в примере выполняется холостое

суммирование со вторым операндом (4 или

7 вершины). Чтобы ускорить этот процесс,

можно было бы ввести средство передачи

операнда сразу во входной регистр (с

помощью дополнительных коммутаторов),

что позволило бы ускорить этот процесс

и так далее. Поэтому в силу неоднозначности

структурной реализации и отображения

будет наблюдаться и неоднозначно

отображаться исходный алгоритм в виде

микрокоманд.

рассматриваемом примере для удешевления

используется одноформатная шина ввода,

что приводит к последовательному воду

данных в вершинах С1 (1 вершина) и С2 (2

вершина) (снижается быстродействие).

Сравнение знаков в примере выполняется

программой, сначала знак А (8 вершина),

потом знак В (8 или 9 вершина). Если бы в

схему был дополнительно введён сумматор

по модулю 2, то сравнение знаков произвелось

бы за 1 такт. Если один из операндов равен

нулю, то в примере выполняется холостое

суммирование со вторым операндом (4 или

7 вершины). Чтобы ускорить этот процесс,

можно было бы ввести средство передачи

операнда сразу во входной регистр (с

помощью дополнительных коммутаторов),

что позволило бы ускорить этот процесс

и так далее. Поэтому в силу неоднозначности

структурной реализации и отображения

будет наблюдаться и неоднозначно

отображаться исходный алгоритм в виде

микрокоманд.

9, Общие понятия об интегральной операционной части. Пример интегральной операционной части.