- •1. Классификация аналоговых электронных устройств.

- •2. Основные параметры усилительных устройств.

- •3. Основные характеристики усилительных устройств.

- •4. Режимы работы усилительных каскадов: а, в, ав.

- •5. Задание рабочей точки биполярного транзистора (бт) в схеме с фиксированным током базы. Основные расчетные соотношения.

- •6. Задание рабочей точки бт в схеме с фиксированным напряжением база-эмиттер. Основные расчетные соотношения.

- •7. Стабилизация рабочей точки бт в схеме с коллекторной стабилизацией. Основные расчетные соотношения.

- •8. Стабилизация рабочей точки бт в схеме с эмиттерной стабилизацией. Основные расчетные соотношения.

- •9. Эквивалентные представления усилительного каскада в виде управляемого источника напряжения и управляемого источника тока.

- •10.Ук на бт с оэ в области средних частот: эквивалентная схема, вх и вых сопротивление, ку по току и апряжению.

- •11. Ук на бт с об в области средних частот: эквивалентная схема, вх и вых сопротивление, ку по току и напряжению.

- •12 Ук на бт с ок (эмиттерный повторитель) в области средних частот. Эквивалентная схема, входное и выходное сопротивление, коэффициент усиления по току и напряжению.

- •13. Обратные связи в усилительных устройствах: основные понятия, классификация.

- •14. Коэффициент передачи усилителя охваченного ос. Влияние обратных связей на параметры и характеристики усилителя.

- •15. Сравнительная характеристика параметров ук на бт с оэ, ок и об: коэффициенты усиления по току и напряжению, входное и выходное сопротивление, полоса пропускания.

- •16. Усилительные каскады на пт с общим истоком.

- •17. Усилители постоянного тока (упт) на бт: способы устранения дрейфа нуля, согласование уровней постоянного напряжения между каскадами.

- •18. Двухтактный бестрансформаторный оконечный каскад в режиме класса в. Переходные искажения.

- •19. Двухтактный бестрансформаторный оконечный каскад в режиме класса ав.

- •20.Дифференциальные усилительный каскад: принцип действия.

- •21.Дифференциальный усилительный каскад : вх и вых сопротивление, коэффициенты усиления синф. И диф. Сигналов, Косс.

- •22. Способы улучшения параметров дифференциальных усилительных каскадов.

- •23. Классификация и параметры операционных усилителей(оу).

- •24. Инвертирующий усилитель на оу.

- •25. Неинвертирующий усилитель на оу.

- •26. Схема сумматора на оу.

- •27. Дифференцирующий усилитель на оу.

- •28. Интегрирующий усилитель на оу.

- •29. Логарифмирующий усилитель на оу.

- •30. Антилогарифмирующий усилитель на оу.

- •31 . Ключ на бт: принципиальная схема, передаточная характеристика, статический режим работы.

- •32 . Ключ на бт: принципиальная схема, динамический режим работы.

- •33. Способы повышения быстродействия ключей на бт

- •34. Ключи на мдп-транзисторах

- •35. Ключ на комплементарных мдп-транзисторах

- •36.Логические элементы, логические функции, основные законы алгебры логики

- •37.Принцип построения лог. Элементов на основе полупроводниковых диодов.

- •37.Принцип построения лог. Элементов на основе полупроводниковых диодов.

- •38.Базовый логический элемент транзистрно-транзисторной логики (ттл).

- •39. Базовый логический элемент эммитерно-связанной логики (эсл).

- •40.Интегрально-инжекционная логика.

- •41. Основные параметры являются общими для всех существующих и возможных логических имс и позволяют сравнивать между собой микросхемы различных типов. Основными параметрами являются:

- •42.Rs–триггер

- •43. Синхронный rs-триггер.

- •44. D-триггер

- •45. Т-триггер

- •46.Jk-триггер

- •47.Мультивибратор на логических элементах

- •48.Особенности диапазона свч. Деление свч диапазона на поддиапазоны.

- •49. Особенности эп свч с динамическим управлением электронным потоком. Общий принцип действия и характеристики эп свч.

- •50. Конструкция, принцип действия и параметры двухрезонаторного пролетного клистрона.

- •51. Устройство и принцип действия лампа бегущей волны о-типа (лбво)

- •52.Конструкция, принцип действия и условия самовозбуждения лампа обратной волны о-типа

- •53.Движение электронов в скрещенных постоянных электрическом и магнитном полях.

- •54.Конструкция,принцип действия, амплитудное и фазовое условия самовозбуждения многорезонаторного магнетрона. Парабола критического режима.

- •55. Диоды Ганна. Эффект Ганна. Особенности многодолинных полупроводников.

- •56. Автогенераторы на диодах Ганна. Конструкции, эквивалентная схема. Режимы работы. Параметры генераторов, области применения.

- •58. Оптические квантовые генераторы (лазеры) на твердом теле: конструкция, принцип действия, параметры, области применения.

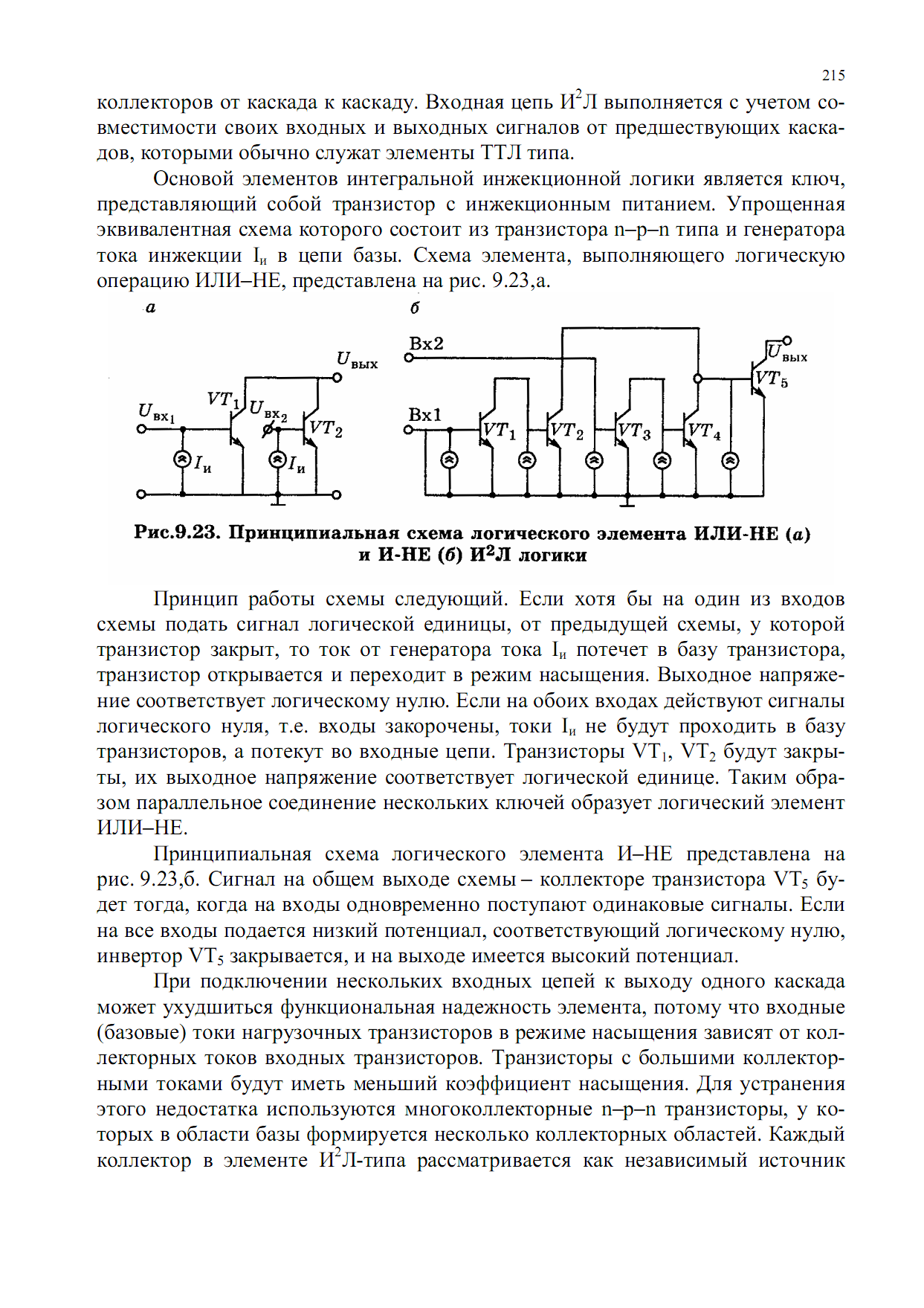

40.Интегрально-инжекционная логика.

41. Основные параметры являются общими для всех существующих и возможных логических имс и позволяют сравнивать между собой микросхемы различных типов. Основными параметрами являются:

1. реализуемая логическая функция;

2. быстродействие;

3. коэффициент объединения по выходу (нагрузочная способность);

4. помехоустойчивость;

5. потребляемая мощность;

6. устойчивость против внешних воздействий;

7. степень

интеграции, надежность.

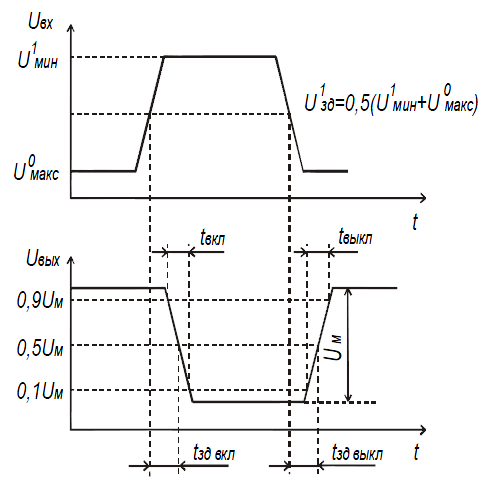

Быстродействие ИС определяется средним временем задержки сигнала. Среднее время задержки определяется временем прохождения сигнала через одну микросхему в устройстве. При определении средней задержки в качестве границ временных интервалов обычно берут точки на фронтах, соответствующие половине перепада напряжения, или точки, соответствующие уровням 0,1 и 0,9 этого перепада

По среднему времени задержки ИС делятся на: сверхбыстродействующие tзад ср < 5 нс; быстродействующие 5 нс < tзад ср < 10 нс. среднего быстродействия 10 нс < tзад ср < 100нс; низкого быстродействия tзад ср > 100 нс.

Коэффициент объединения по входу – это максимальное число входов, которое может иметь логический элемент. С увеличением коэффициента объединения по входу расширяются логические возможности микросхемы за счет выполнения функции с большим числом э в на одном типовом элементе. Увеличение коэффициента объединения по входу ухудшает другие параметры микросхемы: быстродействие, помехоустойчивость, нагрузочную способность. Чаще всего коэффициент объединения по входу не превышает 8, что определяется ограниченным числом выводов ИС.

Коэффициент разветвления по выходу "n" (нагрузочная способность) определяется числом схем этой же серии, входы которых могут быть подключены к выходу данной схемы без нарушения ее работоспособности. Чем выше "n", тем шире логические возможности микросхемы и тем меньше число микросхем необходимо для построения сложного вычислительного устройства. Однако увеличение "n", т.е. увеличение числа нагрузок, ухудшает помехоустойчивость и быстродействие.

Помехоустойчивость Uп макс – наибольшее значение напряжения на входе микросхемы, при котором еще не происходит изменения уровней выходного напряжения. Помехоустойчивость определяется работоспособностью логического элемента при наличии различных помех, действующих на входе ИМС наряду с полезным сигналом. Помехи могут возникать как в самих логических схемах, так и наводиться от посторонних устройств. Помехи бывают статические и динамические. Под статическими понимают помехи, длительность которых значительно превышает длительность переходных процессов в логических элементах. К импульсной (динамической) помехе относятся кратковременные импульсы, длительность которых cоизмерима с длительностью переходных процессов в логических элементах. По статической помехоустойчивости логические элементы условно можно разделить на элементы: с низкой помехоустойчивостью Uп ст = 0,2…0,4 В; со средней помехоустойчивостью Uп ст = 0,4…0,8 В; с высокой помехоустойчивостью Uп ст > 0,8 В.

Импульсная помехоустойчивость всегда выше статической. Это вызвано тем, что при коротком импульсе помехи паразитные емкости в логическом элементе не успевают перезарядиться до пороговых уровней переключения микросхемы. По потребляемой мощности ИМС делятся на:

1.мощные 25 ≤ Рср ≤ 250 мВт (ЭСЛ-схемы);

2.средней мощности 3 ≤ Рср ≤ 25 мВт (ТТЛ-схемы); маломощные 0,3 ≤ Рср ≤ 3 мВт;

3.микромощные 1 ≤ Рср ≤ 300 мкВт (КМОП-схемы);

4.нановаттные Рср < 1 мкВт (интегральная инжекционная логика).

Потребляемая мощность зависит от напряжения источника питания Uип. Напряжение Uип должно соответствовать одному из значений стандартного ряда напряжений питания: 1,2; 1,6; 2,0; 2,4; 3,0; 4,0; 5,0; 6,3; 9,0; 12,6 В. Для цифровых микросхем на биполярных транзисторах типовые значения Uип составляют 2…5 В, для схем на МДП-транзисторах 5…9 В.