- •Алгоритм Тамасуло

- •Алгоритм Тамасуло

- •Схема процессора для реализации алгоритма Тамасуло

- •Состав процессора

- •Схема процессора для реализации алгоритма Тамасуло

- •Этапы исполнения инструкции

- •Устройство СР

- •Планирование инструкций

- •Ожидание готовности операндов, исполнение, сохранение результатов

- •Обработка инструкций загрузки и сохранения.

- •Порядок исполнения инструкций загрузки и сохранения.

- •Файл переименования

- •Обозначения

- •Такт 0

- •Такт 1

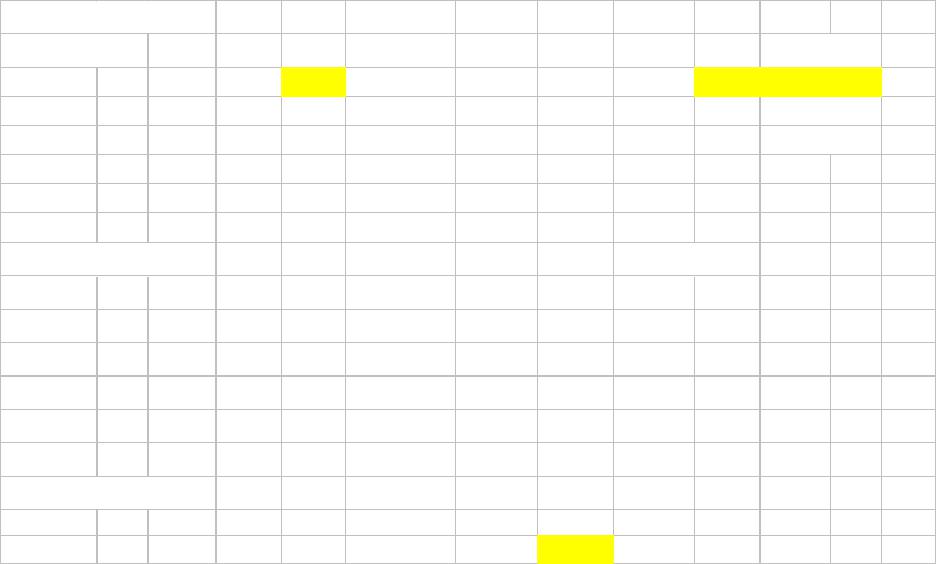

- •Такт 2

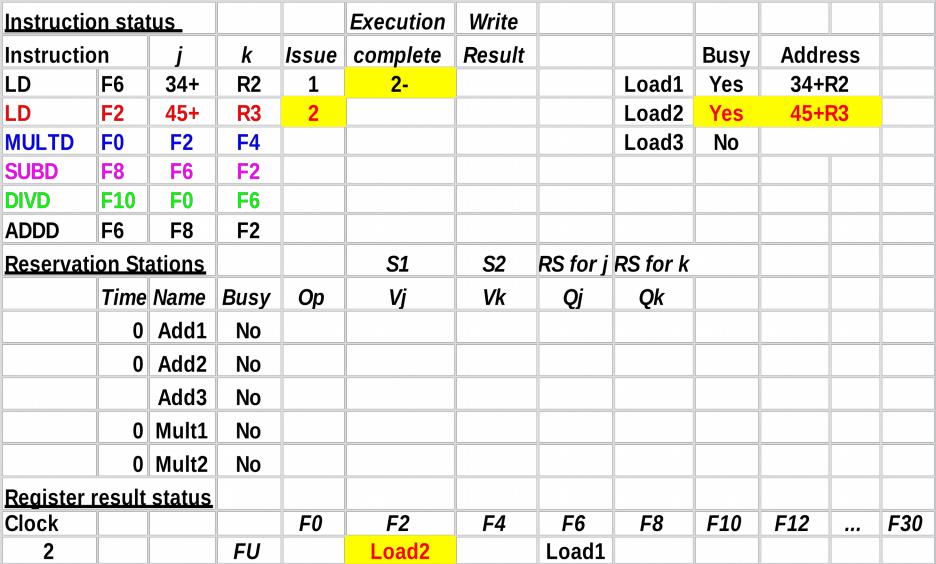

- •Такт 3

- •Такт 4

- •Такт 5

- •Такт 6

- •Такт 7

- •Такт 8

- •Такт 9

- •Такт 10

- •Такт 11

- •Такт 12

- •Такт 15

- •Такт 16

- •Такт 56

- •Такт 57

- •Такт 0

- •Такт 4

- •Такт 5

- •Такт 6

- •Такт 7

- •Такт 8

- •Такт 9

- •Такт 15

- •Такт 16

- •Такт 17

- •Такт 18

- •Такт 19

- •Такт 20

- •Такт 21

- •Такт 57

- •Такт 58

- •Общее описание алгоритма

- •Достоинства и недостатки алгоритма.

- •Пример задачи

Порядок исполнения инструкций загрузки и сохранения.

•Определяется наличием зависимостей между инструкциями по ячейкам памяти.

•Адреса ячеек вычисляются на первом этапе.

•Инструкция загрузки ожидает завершения всех предшествующих инструкций сохранения по данному адресу.

•Инструкция сохранения ожидает завершения всех предшествующих инструкций загрузки и сохранения по данному адресу.

Файл переименования

•Находиться в РФ.

•Содержит имена переименованных

регистров. |

Регистр |

Ссылка |

•Состоит из двух полей:

•Если значение находиться в регистре, то ссылка равна нулю, если нет то ссылка указывает на СР, которая его вычислит.

1.L.D

F6,34(R2)

2.L.D

F2,45(R3)

3.MUL.D

F0,F2,F4

4.SUB.D

F8,F2,F6

5.DIV.D

F10,F0,F6

6.ADD.D

F6,F8,F2

Пример 1

Допущения

1.Латентность загрузки/сохранения : 2

2.Латентность сложения/вычитания : 2

3.Латентность умножения : 10

4.Латентность деления: 40

5.СР для загрузки/сохранения: 3

6.СР для простых арифм. орпер. : 3

7.СР для сложных арифм. орпер. : 2

8.Планирование инструкций происходит отдельно от процесса исполнения.

Обозначения

Op — операция, которая будет выполняться Vj, Vk— готовые значения операндов.

Qj, Qk— ссылка на СР, на которой будет рассчитан соответствующий операнд. Значение «0» – данные записаны в Vj или Vk соответственно.

Busy — флаг занятости.

Issue — стадия планирования инструкции.

Complete — стадия выполнения и завершения выполнения.

Result — стадия сохранения результата

Такт 0

Такт 1

Instruction status |

|

|

Execution |

Write |

|

|

|

|

|

|

||

Instruction |

j |

k |

Issue |

complete |

Result |

|

|

Busy |

Address |

|

||

LD |

F6 |

34+ |

R2 |

1 |

|

|

|

Load1 |

Yes |

34+R2 |

|

|

LD |

F2 |

45+ |

R3 |

|

|

|

|

Load2 |

No |

|

|

|

MULTD |

F0 |

F2 |

F4 |

|

|

|

|

Load3 |

No |

|

|

|

SUBD |

F8 |

F6 |

F2 |

|

|

|

|

|

|

|

|

|

DIVD |

F10 |

F0 |

F6 |

|

|

|

|

|

|

|

|

|

ADDD |

F6 |

F8 |

F2 |

|

|

|

|

|

|

|

|

|

Reservation Stations |

|

|

S1 |

S2 |

RS for j |

RS for k |

|

|

|

|

||

|

Time |

Name |

Busy |

Op |

Vj |

Vk |

Qj |

Qk |

|

|

|

|

|

0 |

Add1 |

No |

|

|

|

|

|

|

|

|

|

|

0 |

Add2 |

No |

|

|

|

|

|

|

|

|

|

|

|

Add3 |

No |

|

|

|

|

|

|

|

|

|

|

0 |

Mult1 |

No |

|

|

|

|

|

|

|

|

|

|

0 |

Mult2 |

No |

|

|

|

|

|

|

|

|

|

Register result status |

|

|

|

|

|

|

|

|

|

|

||

Clock |

|

|

|

F0 |

F2 |

F4 |

F6 |

F8 |

F10 |

F12 |

... |

F30 |

1 |

|

|

FU |

|

|

|

Load1 |

|

|

|

|

|

Такт 2

Такт 3

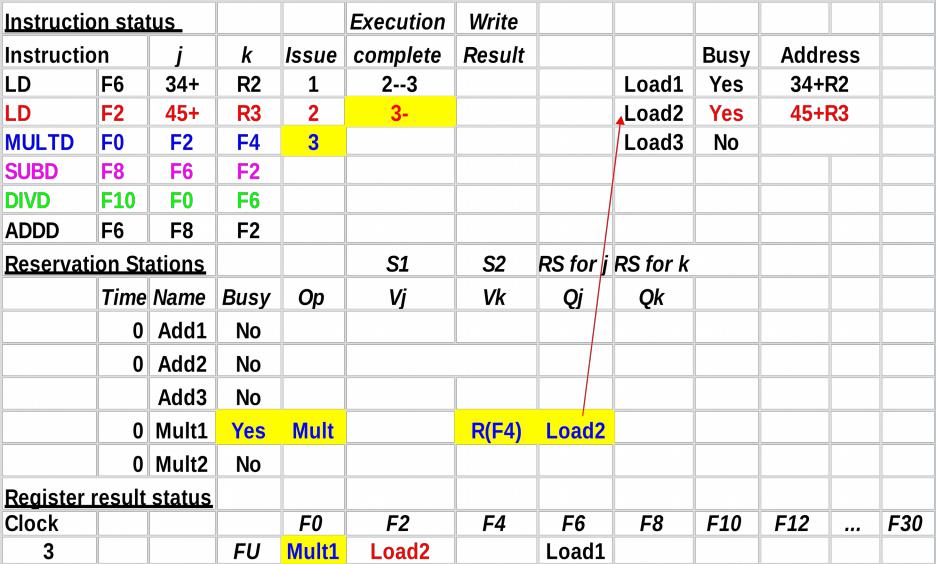

Такт 4

Instruction status |

|

|

Execution |

Write |

|

|

|

|

|

|

|

||

Instruction |

j |

k |

Issue |

complete |

Result |

|

|

Busy |

Address |

|

|

||

LD |

F6 |

34+ |

R2 |

1 |

2--3 |

4 |

|

Load1 |

No |

|

|

|

|

LD |

F2 |

45+ |

R3 |

2 |

3--4 |

|

|

Load2 |

Yes |

45+R3 |

|

|

|

MULTD |

F0 |

F2 |

F4 |

3 |

|

|

|

Load3 |

No |

|

|

|

|

SUBD |

F8 |

F6 |

F2 |

4 |

|

|

|

|

|

|

|

|

|

DIVD |

F10 |

F0 |

F6 |

|

|

|

|

|

|

|

|

|

|

ADDD |

F6 |

F8 |

F2 |

|

|

|

|

|

|

|

|

|

|

Reservation Stations |

|

|

S1 |

S2 |

RS for j |

RS for k |

|

|

|

|

|

||

|

Time |

Name |

Busy |

Op |

Vj |

Vk |

Qj |

Qk |

|

|

|

|

|

|

0 |

Add1 |

Yes |

Sub |

M(A1) |

|

|

Load2 |

|

|

|

|

|

|

0 |

Add2 |

No |

|

|

|

|

|

|

|

|

|

|

|

|

Add3 |

No |

|

|

|

|

|

|

|

|

|

|

|

0 |

Mult1 |

Yes |

Mult |

|

R(F4) |

Load2 |

|

|

|

|

|

|

|

0 |

Mult2 |

No |

|

|

|

|

|

|

|

|

|

|

Register result status |

|

|

|

|

|

|

|

|

|

|

|

||

Clock |

|

|

|

F0 |

F2 |

F4 |

F6 |

F8 |

F10 |

F12 |

... |

|

F30 |

4 |

|

|

FU |

Mult1 |

Load2 |

|

M(A1) |

Add1 |

|

|

|

|

|

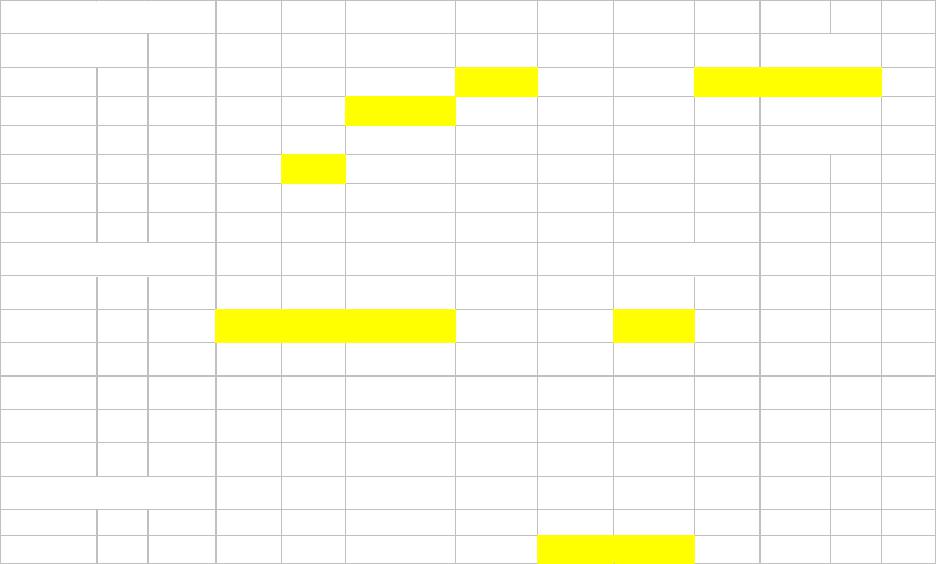

Такт 5

Instruction status |

|

|

Execution |

Write |

|

|

|

|

|

|

||

Instruction |

j |

k |

Issue |

complete |

Result |

|

|

Busy |

Address |

|

||

LD |

F6 |

34+ |

R2 |

1 |

2--3 |

4 |

|

Load1 |

No |

|

|

|

LD |

F2 |

45+ |

R3 |

2 |

3--4 |

5 |

|

Load2 |

No |

|

|

|

MULTD |

F0 |

F2 |

F4 |

3 |

|

|

|

Load3 |

No |

|

|

|

SUBD |

F8 |

F6 |

F2 |

4 |

|

|

|

|

|

|

|

|

DIVD |

F10 |

F0 |

F6 |

5 |

|

|

|

|

|

|

|

|

ADDD |

F6 |

F8 |

F2 |

|

|

|

|

|

|

|

|

|

Reservation Stations |

|

|

S1 |

S2 |

RS for j |

RS for k |

|

|

|

|

||

|

Time |

Name |

Busy |

Op |

Vj |

Vk |

Qj |

Qk |

|

|

|

|

|

2 |

Add1 |

Yes |

Sub |

M(A1) |

M(A2) |

|

|

|

|

|

|

|

0 |

Add2 |

No |

|

|

|

|

|

|

|

|

|

|

|

Add3 |

No |

|

|

|

|

|

|

|

|

|

|

10 |

Mult1 |

Yes |

Mult |

M(A2) |

R(F4) |

|

|

|

|

|

|

|

0 |

Mult2 |

Yes |

Div |

|

M(A1) |

Mult1 |

|

|

|

|

|

Register result status |

|

|

|

|

|

|

|

|

|

|

||

Clock |

|

|

|

F0 |

F2 |

F4 |

F6 |

F8 |

F10 |

F12 |

... |

F30 |

5 |

|

|

FU |

Mult1 |

M(A2) |

|

M(A1) |

Add1 |

Mult2 |

|

|

|