Введение

Развитие интегральной технологии производства электронных схем позволило вернуться к построению ЗУ на полупроводниковых элементах. По сравнению с ферритовой памятью полупроводниковая память имеет ряд достоинств: большее быстродействие, компактность, меньшую стоимость, совместимость по сигналам с логическими схемами, общие с другими электронными устройствами ЭВМ технологические и конструктивные принципы построения. Недостатком полупроводниковых ЗУ является то, что они в режиме хранения информации потребляют энергию и теряют информацию при выключении напряжения питания.

Подавляющее большинство ЗУ в настоящее время является адресными. В таких ЗУ каждой ячейке присваивается номер, называемый адресом.

Для выполнения обращения к какой-либо ячейке накопителя информации используются схемы, позволяющие отыскивать по заданному адресу нужную ячейку и осуществлять запись информации в нее или считывать информацию из нее.

По технологии изготовления и типу запоминающих элементов различают ЗУ на биполярных транзисторах ( ТТЛ- или эСЛ-схемами) и ЗУ на МОП-транзисторах.

ЗУ на биполярных транзисторах имеют более высокое быстродействие (время выборки составляет 10-30 и 40-100 нc соответственно для ЭСЛ- и ТТЛ-схем), но меньшую плотность размещения запоминающих элементов на кристалле и, следовательно, меньшую емкость для одного кристалла (256 бит - 4 Кбит), большую потребляемую емкость и большую стоимость. Запоминающими элементами в таких ЗУ являются статические ТТЛ- или ЭСЛ-триггеры (статическая память).

ЗУ на МОП-транзисторах благодаря более простой технологии изготовления МОП-схем, меньшим размерам транзисторов, меньшей потребляемой мощности имеют значительно большую емкость одного кристалла (4-64 Кбит), значительно меньшую стоимость (в пересчете на один запоминаемый бит), но существенно меньшее быстродействие (время выборки 200-350 нс). Запоминающим элементом в таком ЗУ может быть как МОП-триггер (статическое ЗУ), так и хранящая электрический заряд емкость затвора МОП-транзистора (динамическое ЗУ).

Рассмотрим статические ОЗУ

-

Статические озу

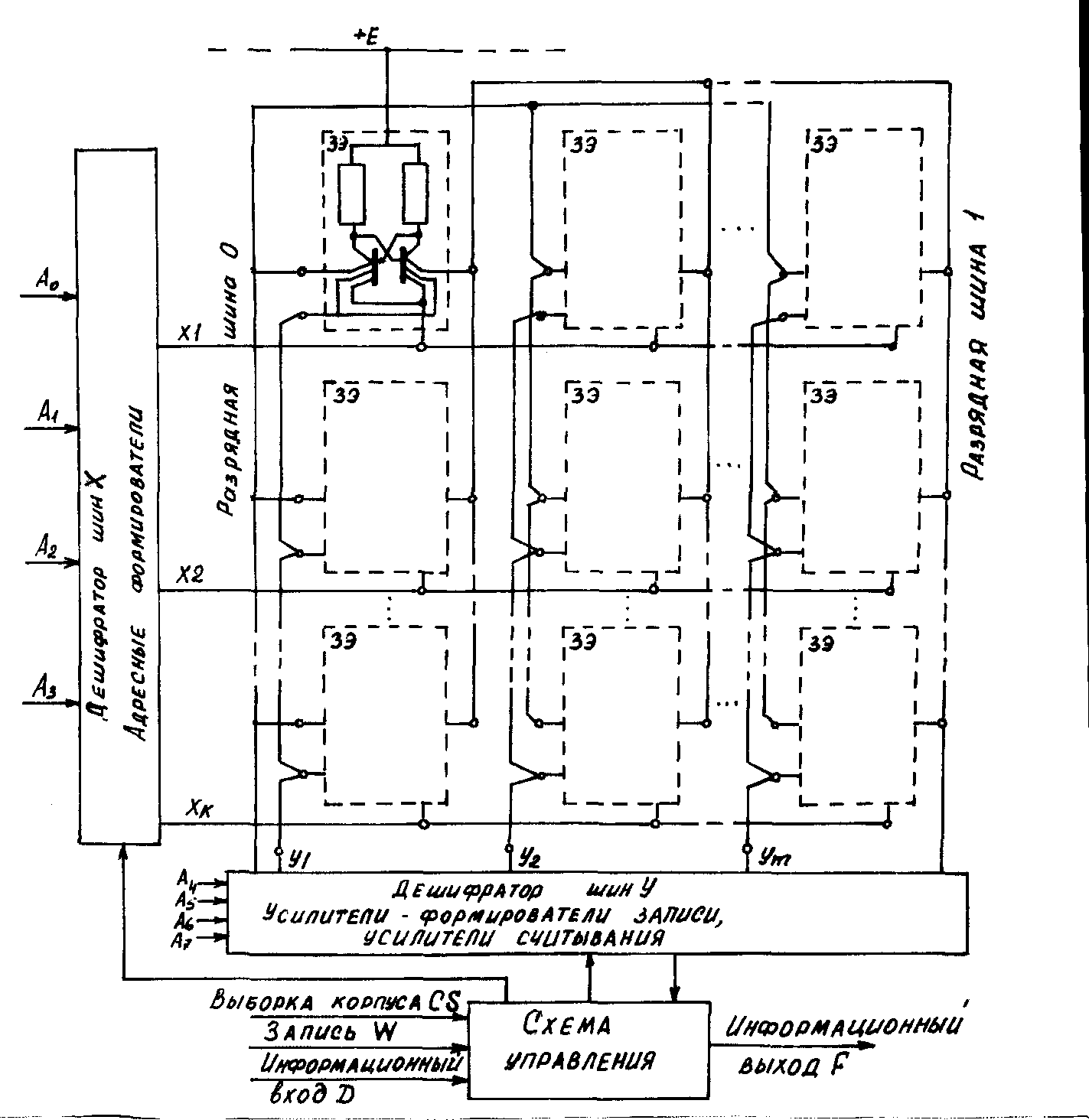

Интегральная схема ОЗУ на биполярных элементах представляет собой кристалл кремния, в котором образованы массив запоминающих элементов (триггеров) со всеми соединениями между собой, адресные дешифраторы, усилители-формирователи записи и считывания и другие схемы для управления адресной выборкой, записью и считыванием. Для примера на рис.1 представлена схема одного корпуса (модуля) биполярного ЗУ, предназначенного для хранения 256 одноразрядных чисел (256 х I).

Модуль имеет восемь адресных входов А0 А1,...,А7 , входы для сигналов выбора корпуса CS , разрешения записи W и информационные вход D и выход F.

В отсутствии сигнала CS и сигналов адресной выборки модуль находится в режиме хранения информации.

Для считывания информации поступает сигнал выбора корпуса CS, подается и дешифрируется код адреса А0, А1 ..., А7 . При этом выбираются соответствующие адресные шины Xi и Yi , на которые поступает потенциал логической I, Считанная с выбранного запоминающего элемента ( ЗЭ ) информация по разрядным шинам поступает на усилители считывания и далее на информационный выход F . Запись производится подачей кода адреса, сигнала выбора корпуса CS , сигнала записи W и значения разряда записываемой информации на информационный вход D , При наличии указанных сигналов значение разряда (0 или I) записывается в избранный запоминающий элемент.

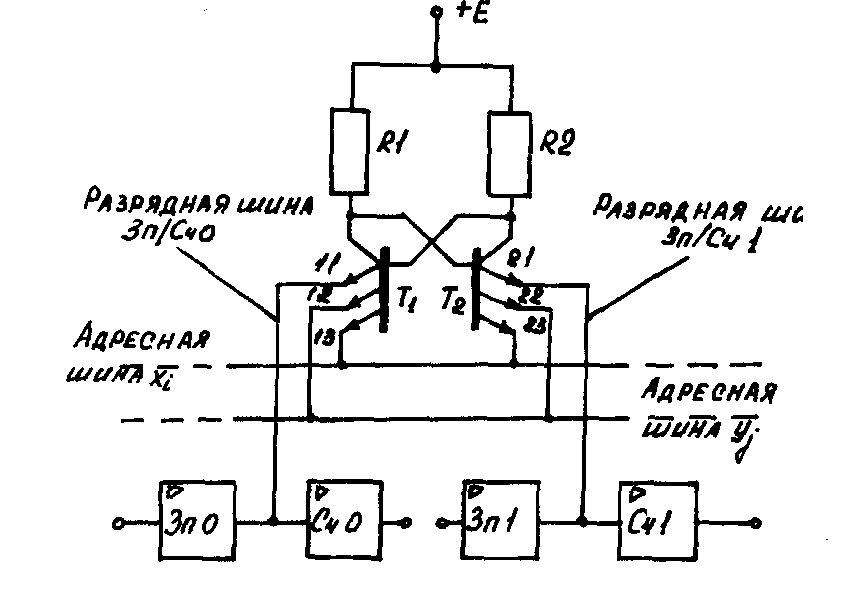

В биполярных ЗУ в качестве запоминающего элемента ЗЭ используется статический триггер на двух многоэмиттерных транзисторах Т1 и Т2 с непосредственными связями (рис.2 ).

Рис.1 . Структурная схема модуля биполярного ЗУ

Рис.2 Запоминающий элемент биполярного ЗУ

Разрядные (или информационные) эмиттеры II и 21 служат для записи в запоминающий элемент и считывания из него бита информации, а остальные (адресные) эмиттеры - для выборки запоминающего элемента. Информационные эмиттеры II и 21 всех ЗЭ модуля ЗУ подсоединяются к общим разрядным шинам 0 и I соответственно.

В таком ЗЭ информационные сигналы, соответствующие I и О, как при записи, так и при считывании имеют один и тот же уровень потенциала, но поступают или снимаются (в зависимости от режима работы) с разных шин: разрядной шины 0 или разрядной шины I.

К каждой из разрядных шин (нуля и единицы) подключены разрядные усилитель записи и усилитель считывания - соответственно О и I. К левому плечу триггера подключены усилители, производящие запись и считывание 0, а к правому - усилители, записывающие и считывающие I. Примем, что ЗЭ находится в состоянии 0, если транзистор T1 открыт.

ЗЭ может находиться в трех режимах: хранение информации, считывание и запись.

В режиме хранения эмиттерный ток открытого транзистора замыкается на землю через адресные эмиттеры и адресные шины, находящиеся под потенциалом логического нуля ( <+0,4В ). При этом информационные эмиттеры II и 21 должны быть заперты. Для этого на них подается потенциал (I - 1,5 В) с усилителя записи, который больше потенциала адресных эмиттеров (больше уровня логического 0, но меньше минимального значения сигнала логической I, составляющего 2,4 В), с тем, чтобы при выборе ЗЭ через информационные эмиттеры протекали токи, необходимые для операций считывания и записи.

При выборке данного ЗЭ на его адресные эмиттеры с выходов адресных дешифраторов подается потенциал логической 1 ( > 2,4В ), превышающий потенциал информационных эмиттеров. При этом адресные эмиттеры запираются и коллекторный ток открытого транзистора течет через его информационный эмиттер. Этим обеспечивается возможность считывания из ЗЭ или записи в него информации.

Состояние I или О ЗЭ распознается по наличию тока соответственно в разрядной шине 0 (открыт транзистор Т1 ) или в разрядной шине I (открыт транзистор Тг ). Считывание происходит без разрушения информации. Хранимая в ЗЭ информация доступна для считывания все время, пока ЗЭ находится в выбранном состоянии и в него не производится запись (отсутствует импульс "разрешение записи"). При считывании на входы обоих усилителей записи (ЗпО и Зп1) подается потенциал логического нуля. В результате чего на выходах этих усилителей оказывается потенциал логической I, запирающий усилители записи и тем самым предотвращающий ответвление в них тока считывания (тока информационного эмиттера). Ток считывания вытекает из информационного эмиттера открытого транзистора (например Т1 ) и втекает в базовую цепь входного транзистора усилителя считывания 0, усиливается в нем и поступает на выход. При хранении I открыт транзистор Т2 и ток считывания поступает на усилитель считывания I, усиливается в нем и поступает на выход схемы.

При записи в ЗЭ I или 0 с соответствующего усилителя записи на подключенный к нему информационный эмиттер подается потенциал логического 0 ( <0,4В ), а на другой информационный эмиттер продолжает поступать с его невозбужденного усилителя записи потенциал, равный (I - 1,5 В).

Если допустим, что производится запись I в триггер, находившийся перед этим в состоянии I (открыт транзистор t2 ), то подача потенциала низкого уровня на эмиттер 21 не меняет состояния триггера.

Если до записи триггер находился в состоянии 0 (открыт транзистор t1 ), то подача потенциала низкого уровня на эмиттер 21 (запись I) открывает транзистор Т2 . При этом транзистор Т1 закрывается и триггер устанавливается в состояние I.

Такую схему ЗЭ имеет в ЗУ, построенном по структуре 3D . В том случае, когда биполярное ЗУ имеет структуру типа 2D в качестве ЗЭ используют двухэмиттерные транзисторы (одна из адресных шин Хi или Yi отсутствует).

Для построения ЗУ с большим количеством разрядов и (или) слов, чем в запоминающем массиве модуля (корпуса) применяют несколько корпусов. Наличие в корпусе специального входа выбора корпуса CS позволяет строить ЗУ большей емкости, чем емкость одного корпуса. В таком ЗУ сигналом на вход CS можно производить блокировку выборки или отдельных корпусов.

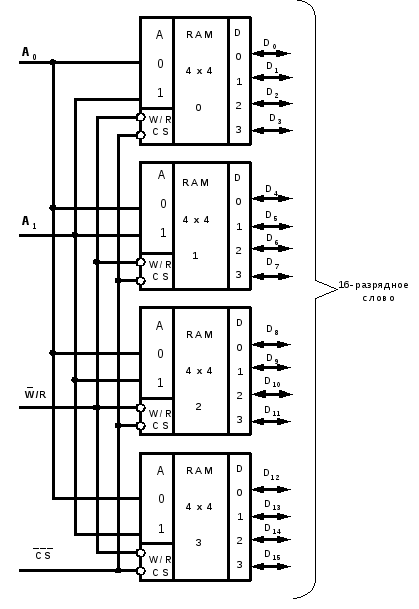

Так как полупроводниковые ЗУ выпускаются в интегральном исполнении, то для увеличения емкости ЗУ производится их каскадирование. Известны два основных способа увеличения емкости памяти ЗУ: способ наращиваемой разрядности хранимого слова и способ наращиваемого числа хранимых слов.

Структурно-функциональная организация ЗУ с наращиваемой разрядностью хранимого слова. При этом способе каскадирования необходимо:

соединить друг с другом адресные входы, входы выбора микросхемы и входы записи/считывания всех К каскадируемых ЗУ;

объединить все выходы ЗУ в шину данных с числом линий (разрядов), равным KxN, где N — число разрядов в слове каскадируемого ЗУ.

В качестве примера на рис.3 изображена схема ЗУ, полученная при каскадировании устройств с однокоординатной адресацией (2D). Построенное ЗУ имеет организацию памяти 4x16.

Рис.3 Структурно-функциональная организация ОЗУ с наращиваемой разрядностью хранимого слова

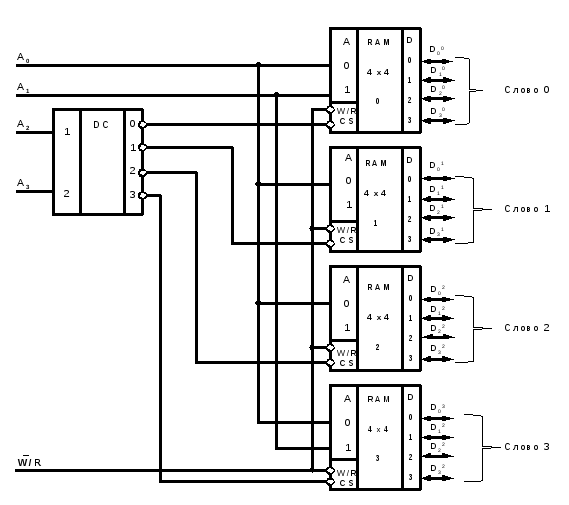

Структурно-функциональная организация ЗУ с наращиваемым числом хранимых слов. Для реализации этого способа каскадирования ЗУ необходимо располагать, по крайней мере, одним дешифратором. Кроме того, ЗУ должны иметь не менее одного входа выбора микросхемы.

Принцип наращивания числа хранимых слов рассмотрим на примере схемы, изображенной на рис.5. В ее состав входят:

дешифратор DC 2x4.

четыре оперативных запоминающих устройства RAM0-RAM3.

Одноименные адресные входы А1 Ао и входы записи/ считывания W/R всех ЗУ соединены друг с другом. Входы выбора микросхемы CS запоминающих устройств RAM0-RAM3 соединены соответственно с выходами дешифратора 0-3.

Рис.4. . Структурно-функциональная организация ОЗУ с наращиваемым числом хранимых слов

Старшие разряды А3, А2 адресного кода активизируют один из выходов дешифратора, устанавливая на нем уровень логического 0. Если, например, активным является выход 2, то на вход RAM2 поступает сигнал CS = 0 и в зависимости от значения сигнала W/R происходит запись или считывание данных в ячейку памяти RAM-2, определяемую младшими разрядами A1 A0 адресного кода. Так как на входы других ЗУ поступает сигнал CS = 1, они находятся в нерабочем состоянии.

Основными недостатками статических 3Э являются значительная мощность рассеяния и большое число активных элементов, что ведет к увеличению габаритов и стоимости ЗУ на них. Поэтому ЗУ на статических ЗЭ главным образом используются в качестве сверхоперативных ЗУ.