Применение в логических выражениях арифметических операторов.

Используются унарные операции присваивания знака, также сложения и вычитания. Операндами этих операторов могут быть группы и числа. Если оба операнда группы, то число разрядов в них должно быть одинаково. Если оба операнда числа, то автоматически выравнивается число разрядов в их двоичном представлении. Если один операнд число, а второй группа, то число представляется в двоичном виде. Если число разрядов двоичного представления меньше числа разрядов второго операнда, то число расширяется нулями, если больше, то выдается сообщение об ошибке.

-a[4..1] = !a[4..1] + 1

c[7..0] + d[7..0]

В логических выражениях используются также операции сравнения. Результатом является логический “0” (GND) если условия сравнения не выполнены и логическая “1” (VCC) в противном случае. Операторы сравнения делятся на логические и арифметические. Операндами операторов логического сравнения могут быть одноразрядные переменные, группы переменных и выводов, а также числа. Недопустимо использование троичных векторов. При логическом сравнение операнды сравниваются по битам. Поэтому число их разрядов должно быть одинаково. Если один операнд группа, а второй число, то число преобразуется в двоичное. Если число разрядов в двоичном числе меньше числа разрядов второго операнда, то оно расширяется нулями, если больше, то выдается сообщение об ошибке.

Операторы арифметического сравнения позволяют сравнивать группы переменных (выводов), а также числа. При арифметическом сравнении группа рассматривается как положительное двоичное число, число разрядов которого соответствует числу разрядов в группе, поэтому операнды должны иметь одинаковое число разрядов. Если один операнд число, а второй группа, то число преобразуется в двоичное. Если число разрядов в двоичном числе меньше числа разрядов второго операнда, то оно расширяется нулями, если больше, то выдается сообщение об ошибке.

Примитивы языка.

Функции реализующиеся вентилями можно описать с помощью логической функции. В AHDLиспользуется 2 типа примитивов: примитивы буферов и примитивы синхронных триггеров, а также триггеров отсечки.

1. Буфер цепочного переноса (CARRY)

В

языкеAHDLэтот буфер

представляет описание прототипа:OUT=CARRY(IN).

Буфер полезен только для устройств типаFLEX.

В

языкеAHDLэтот буфер

представляет описание прототипа:OUT=CARRY(IN).

Буфер полезен только для устройств типаFLEX.

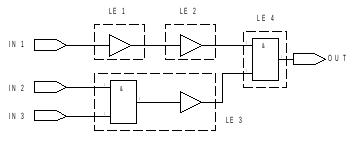

ЛММ – локальная матрица межсоединений

В LEимеетсяLABфункция генератора реализующая 1 функцию от 4-х переменных или 2 функции от 3-х переменных

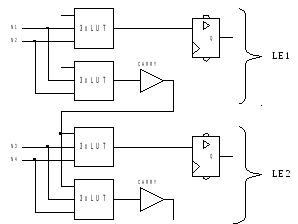

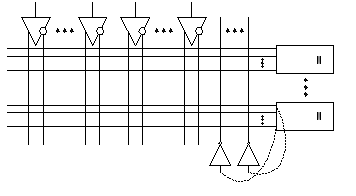

В LEесть схемы переноса и каскадирования, а также триггеров. Эти схемы переноса и каскадирования связывают соседние элементы без использования ЛММ. Буфер цепочного переноса указывает компилятору на возможность использования схем переноса логических элементов. Применение буфера проиллюстрировано следующим рисунком:

Правила использования буфера цепочного переноса (CARRY):

Выходной сигнал буфера можно поставить на вход только одного ЛЭ.

LUTгенератор на вход которого поступает сигнал из буфера переноса преобразовывается компилятором в две 3-х входовые таблицы. Выход второй таблицы должен находится на входе следующего буфера переноса. Если буфер переноса используется неправильно, то он игнорируется компилятором, и выдается соответствующее предупреждение. Компилятор может автоматически вставлять или удалять этот буфер при синтезе логики, если включена опцияCARRYCHAIN.

2 .

Буфер каскадного наращивания булевой

функции (CASCADE) –

каскадирование.

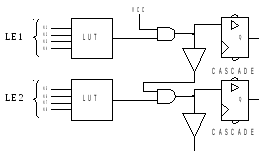

.

Буфер каскадного наращивания булевой

функции (CASCADE) –

каскадирование.

OUT = CASCADE (IN)

Э тот

буфер указывает компилятору на

необходимость приминения схем

каскадированияLE

типа FLEX.

тот

буфер указывает компилятору на

необходимость приминения схем

каскадированияLE

типа FLEX.

ПЛЛМ – программируемая локальная матрица межсоединений.

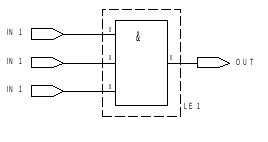

На вход буфера должен поступать сигнал с 2-х входовых элемента “И” (“ИЛИ”). Выход подается на вход 2-х входового элемента “И” (“ИЛИ”).

Цепочка каскадного наращивания должна содержать либо “И”, либо (“ИЛИ”).

Если буфер используется неправильно, то он игнорируется компилятором и выводить сообщение. Можно разрешить компилятору автоматически вставлять и удалять этот буфер при синтезе, если включить опцию CASCADE CHAIN.

3 .

Буфер логического расширителяEXP.

.

Буфер логического расширителяEXP.

OUT=EXP(IN)

Его можно использовать как инвертор.

Этот буфер указывает компилятору на необходимость использования расширителя промежуточных шин в устройствах типа MAX.

Каждый LUTмодуль создает программируемую матрицу “И” и ряд макроячеек. Макроячейки включают дизъюнктор.

Путем программирования макроячейки можно одну или несколько промежуточный шин матрицы “И” связать с дополнительными макроячейками, соединив с расширителем промежуточных шин.

Если выбрать не МАХ устройство, то этот буфер будет рассматриваться как инвертор.

4 .

Буфер глобальной цепи распределения

управляемого сигнала (GLOBAL).

.

Буфер глобальной цепи распределения

управляемого сигнала (GLOBAL).

OUT = GLOBAL (IN)

Этот буфер указывает компилятору на

необходимость использования глобальных

входов, которые имеются у многих ПЛИС.

Эти входы связаны с цепями, проходящими

через всю ПЛИС и использующие для

тактового сигнала GLOBALCLOCK, сигнала сброса

триггеровGLOBALCLEAR,

разрешение выходаGLOBALOUTPUTENABLE,

установка сигнала триггеровGLOBALPRESET. Выход буфера может

соединяться со входами триггера:PRN,CLRN,CLR,ENA(асинхронной установки, очистки буфера,

синхронизации, входом записи), а также

со входом разрешения буфераTRIв некоторых микросхемах типаFLEXможно подавать сигналы, порождаемые на

входных цепях. Если буфер используется

неправильно, то выводиться предупреждение.

Глобальные входы ПЛИС можно использовать

посредствам установки опцииAUTOMATICGLOBAL, посредством командыAssign

GlobalProjectLogicSynthesis.

GlobalProjectLogicSynthesis.

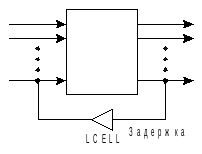

5. Буфер реализации логической ячейки LCELL.

Буфер

указывает компилятору на необходимость

использования логического элемента

(макроячейка в устройствах типа МАХ).

Буфер

указывает компилятору на необходимость

использования логического элемента

(макроячейка в устройствах типа МАХ).

Этот буфер не может быть удален компилятором

Если буферов нет, то получится

Компилятор

будет автоматически вставлять эти

буфера используяAUTOMATELCELL.

Компилятор

будет автоматически вставлять эти

буфера используяAUTOMATELCELL.

6 .

Буфер выхода с открытым коллекторомOPNDRN

.

Буфер выхода с открытым коллекторомOPNDRN

OUT = OPNDRN (IN)

Буфер указывает компилятору на необходимость вывода ПЛИС с открытым коллектором. Он реализует функцию:

-

IN

OUT

0

0

1

Z

Буфер эквивалентен буферу TRI:

Сигнал с выхода буфера должен подаваться на двунаправленный вывод ПЛИС (BIDIR). Если сигнал с выхода буфера наLEПЛИС, то его необходимо подать и на выводы типаBIDIR. Он используется только в семействах микросхемMAX7000SиFLEX10K.

7 .

Буфер размещения логической ячейкиSOFT.

.

Буфер размещения логической ячейкиSOFT.

OUT = SOFT (IN)

Указывает компилятору на возможность использования LE(макроячеек). В процессе синтеза компилятор оценивает аппаратные затраты, связанные с использованиемLE(макроячеек) вместо буфера. Если эти затраты меньше чем затраты без использования буфераSOFT, то этот буфер заменяется на буферLCELL, иначе буфер удаляется.

8 .

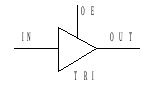

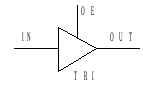

Буфер выходаZ-состоянияTRI.

.

Буфер выходаZ-состоянияTRI.

OUT = TRI (IN, OE)

Поведение буфера можно задать:

-

IN

OE

OUT

X

0

Z

0

1

0

1

1

1

Выход буфера должен соединяться сBIDIRили типаOUTPUT. При использовании выхода буфера во внутренней логике ПЛИС необходимо его связать с одним из выводов указанного типа.