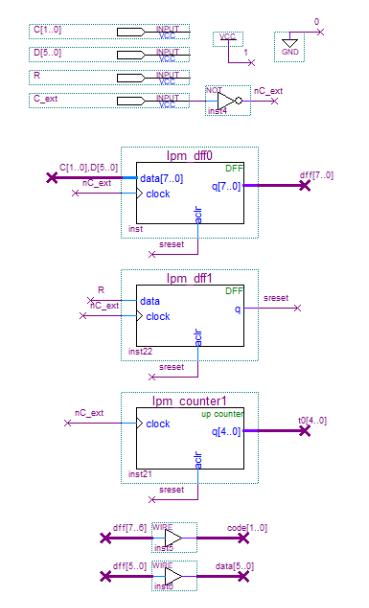

Рисунок 3.2 – Входная часть функциональной схемы

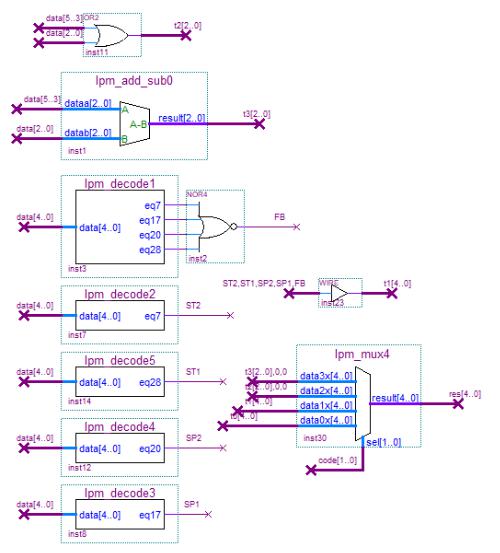

Далее на рисунке 3.3 представлен операционный блок. В операционный блок входит блок побитовой операции , блок операции разности и блок проверки Commodore GCR-кода, выполненный при помощи дешифраторов.

Выходы из блоков идут на мультиплексор, который за счет кода операции выбирает какая операция идет на выход.

11

Рисунок 3.3 – Операционный блок функциональной схемы

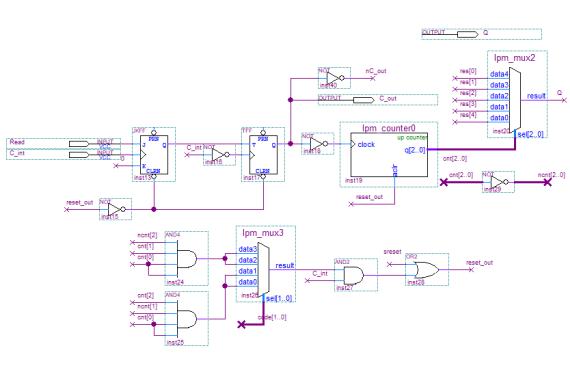

Далее на рисунке 3.4 представлена выходная часть. Так как вывод должен быть последовательным, то на мультиплексор поступают данные с мультиплексора из операционного блока. Чтение происходит через JK-

триггер, на который фиксирует сигнал «Read», который не будет обновляться,

пока не выйдут все необходимые данные. С этого триггера на T-триггер идет разрешающий сигнал, который переключается за счет внутреннего синхроимпульса. Его переключение по заднему фронту воздействует на счетчик, который считывает сигналы. Также ниже представлена конструкция,

которая отвечает за сброс триггеров и счетчика.

12

Рисунок 3.4 – Выходная часть функциональной схемы

13

4 МОДЕЛИРОВАНИЕ

Таблица истинности для плана моделирования согласно варианту №9, а именно для проверки Commodore GCR-кода, логической побитовой операции А B и арифметической операций А - B, представлена в таблице 4.1.

Таблица 4.1 – Таблица истинности плана моделирования

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|||

№ |

Код |

|

|

Данные |

|

|

R |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||

C7 |

C6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

||

|

|

||||||||||||||

1 |

0 |

1 |

X |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

2 |

0 |

1 |

X |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

3 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

- |

- |

|

0 |

0 |

1 |

4 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

- |

- |

|

1 |

1 |

1 |

5 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

- |

- |

|

1 |

0 |

1 |

6 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

- |

- |

|

0 |

1 |

1 |

7 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

|

1 |

1 |

1 |

8 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

0 |

|

9 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

|

0 |

0 |

1 |

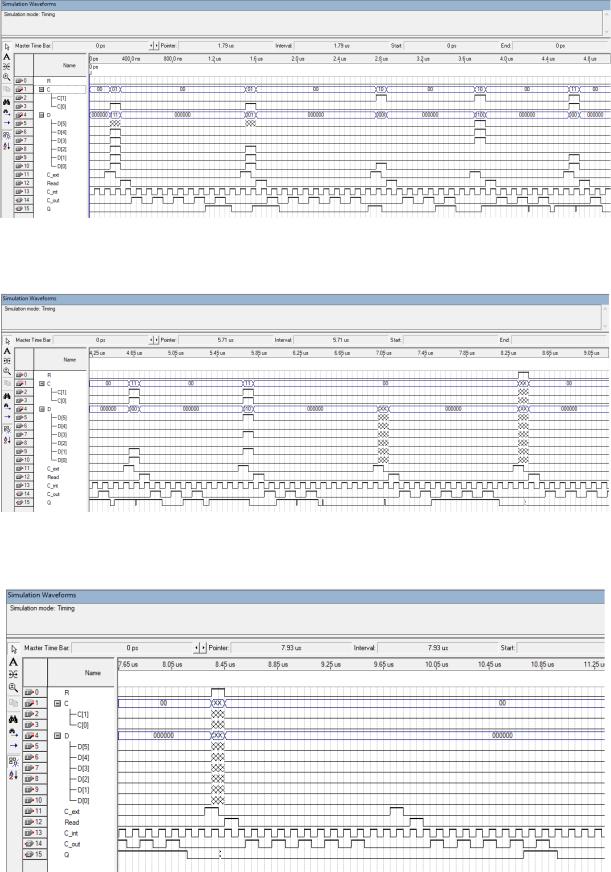

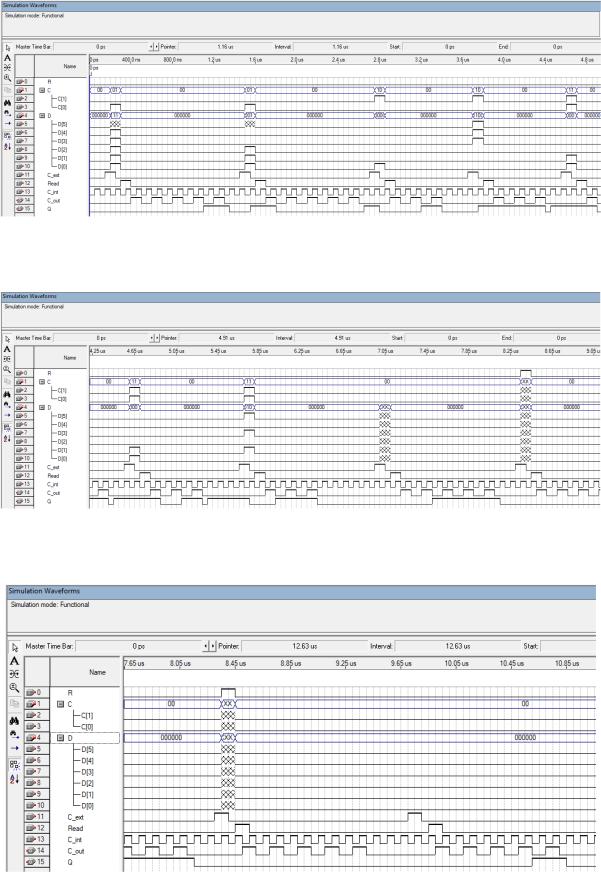

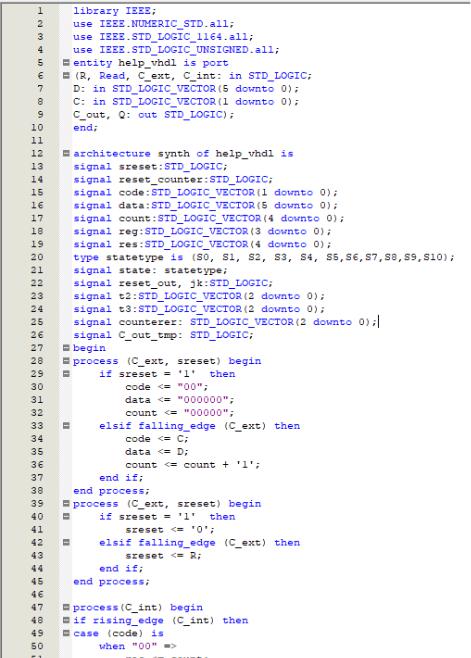

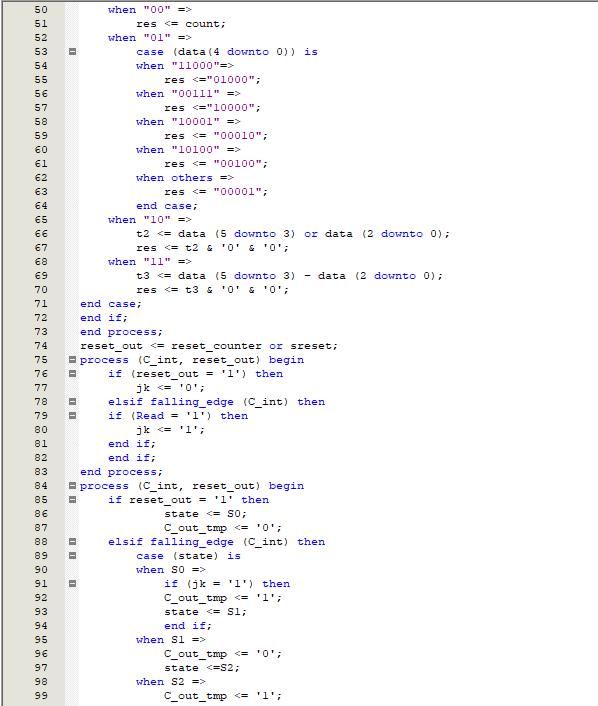

На рисунках 4.1 – 4.3 представлены результаты моделирования в режиме «Timing». На рисунках 4.4 – 4.6 представлены результаты моделирования в режиме «Functional».

На промежутке 0 - 1.4 нс представлена работа первого сигнала.

На промежутке 1.4 - 2.65 нс представлена работа второго сигнала.

На промежутке 2.65 - 3.6 нс представлена работа третьего сигнала.

На промежутке 3.6 - 4.45 нс представлена работа четвертого сигнала.

На промежутке 4.5 - 5.35 нс представлена работа пятого сигнала.

На промежутке 5.4 – 6.45 нс представлена работа шестого сигнала.

На промежутке 6.9 – 8.25 нс представлена работа седьмого сигнала.

На промежутке 8.25 – 9.6 нс представлена работа восьмого сигнала.

На промежутке 9.6 – 11.0 нс представлена работа девятого сигнала.

14

Рисунок 4.1 – Первая часть моделирования функциональной схемы в режиме

«Timing»

Рисунок 4.2 – Вторая часть моделирования функциональной схемы в режиме

«Timing»

Рисунок 4.3 – Третья часть моделирования функциональной схемы в режиме

«Timing» 15

Рисунок 4.4 – Первая часть моделирования функциональной схемы в режиме

«Functional»

Рисунок 4.5 – Вторая часть моделирования функциональной схемы в режиме

«Functional»

Рисунок 4.6 – Третья часть моделирования функциональной схемы в режиме

«Functional» 16

Чтение входных значений D и кода операции C происходит задним фронтом импульса C_ext. После подачи активного сигнала «Read» = 1

происходит выдача значений старшими разрядами вперед в строку Q

тактируемую импульсом C_out, который зависит от количество выдаваемых значений. После подачи сигнала R, происходит синхронный сброс. Все операции также сопровождаются тактирующим импульсом C_int.

При операции 01 – происходит проверка Commodore GCR-кода.

При операции 10 – выполняется логическая побитовая операция А B.

При операции 11 – выполняется арифметическая операция А - B.

При операции 00 – выводится количество выполненных операций.

Результаты моделирования совпадают с таблицей плана моделирования,

что говорит о том, что все выполнено верно. Так как моделирование в режиме

«Timing» приближено к реальности и отображает задержки переключения, то результат немного искажается от идеального в режиме «Functional».

17

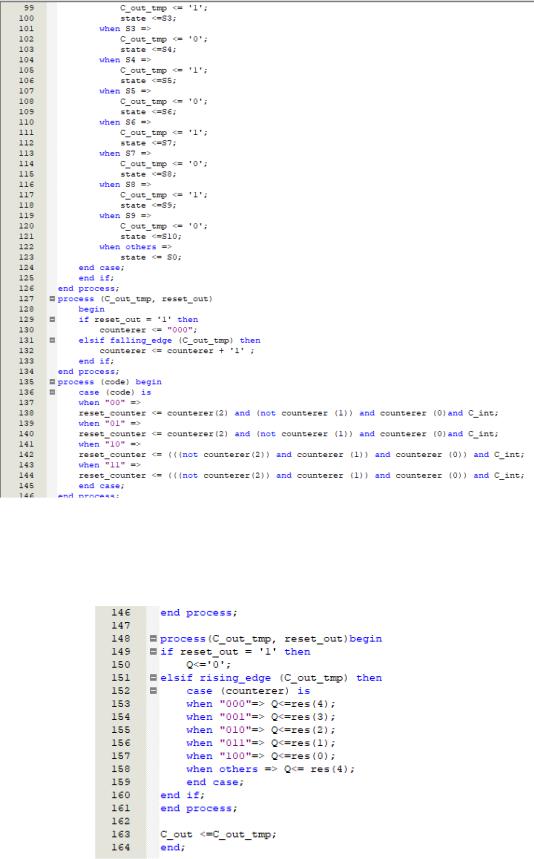

5 ОПИСАНИЕ ФУНКЦИОНАЛЬНОЙ СХЕМЫ НА HDL

Далее был составлен код описания схемы на HDL согласно варианту №9,

а именно на языке описания аппаратуры VHDL, представленный на рисунках

5.1 – 5.4.

Рисунок 5.1 – Первая часть описания функциональной схемы на языке описания аппаратуры VHDL

18

Рисунок 5.2 – Вторая часть описания функциональной схемы на языке описания аппаратуры VHDL

19

Рисунок 5.3 – Третья часть описания функциональной схемы на языке описания аппаратуры VHDL

Рисунок 5.4 – Четвертая часть описания функциональной схемы на языке описания аппаратуры VHDL

20