На строчках 6 - 9 описаны входы и выходы. На строчках 13 – 26 описаны используемые сигналы функциональной схемы.

5.1 Описание входной части

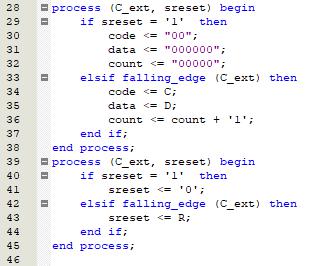

На рисунке 5.5 представлена входная часть функциональной схемы описанной на VHDL.

Рисунок 5.5 – Входная часть Входная часть записывает данные, поступающие по синхроимпульсу

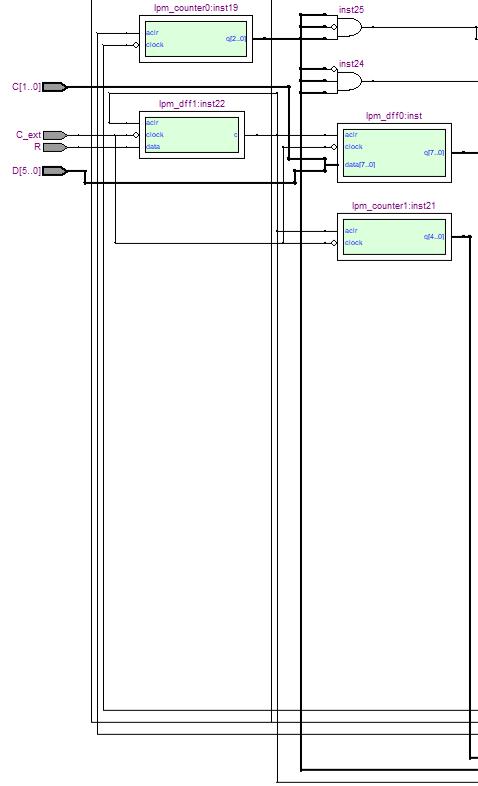

C_ext, а также считает количество операций на строчках 28 – 38. А также организует создание синхронного сигнала сброса на строчках 39 – 45. На рисунке 5.6 представлена схема из RTL Viewer для входной части устройства.

21

Рисунок 5.6 – Схема из RTL Viewer для входной части

22

5.2 Описание операционного блока

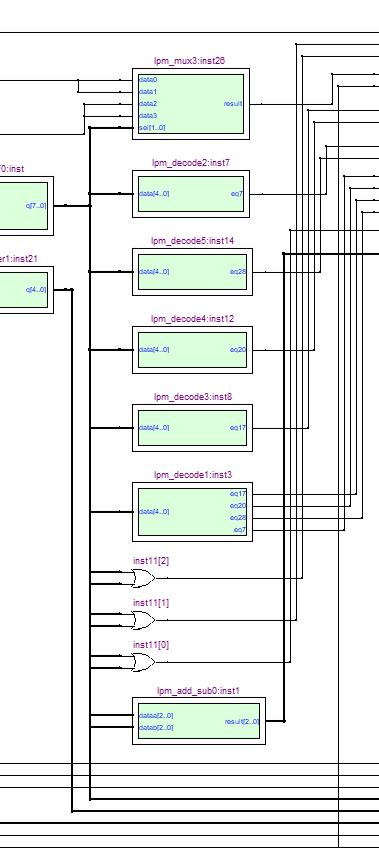

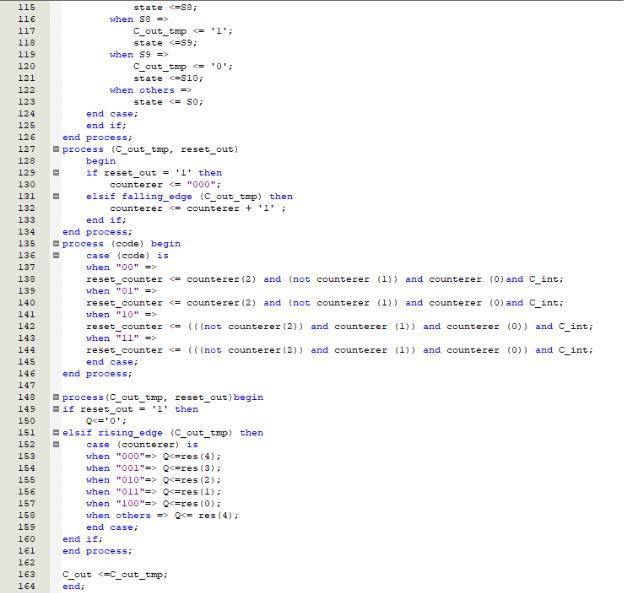

На рисунке 5.7 представлен операционный блок функциональной схемы описанной на VHDL.

Рисунок 5.7 – Операционный блок

В операционный блок идут значения из входного блока. При помощи кода операции выбирается операция. В зависимости от кода операции происходит либо вычисление логической функции А В, либо арифметическая разность, либо операция проверки Commodore GCR-кода. На рисунке 5.8

представлена схема из RTL Viewer для операционного блока.

23

Рисунок 5.8 – Схема из RTL Viewer для операционного блока

24

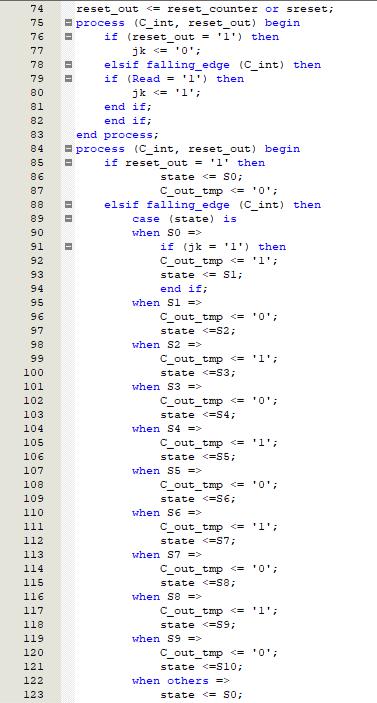

5.3 Описание выходной части

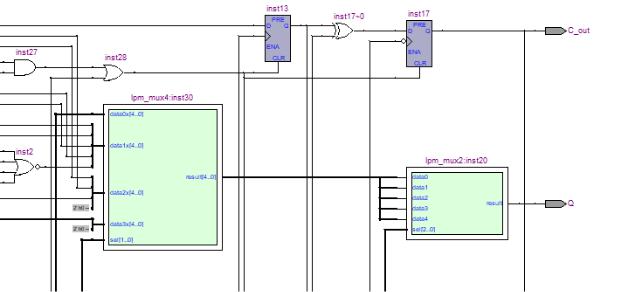

На рисунках 5.9 – 5.10 представлена выходная часть функциональной схемы описанной на VHDL.

Рисунок 5.9 – Первая часть выходного блока

25

Рисунок 5.10 – Вторая часть выходного блока

Выходной блок считывает сигнал чтения «Read» и выдает данные последовательным кодом, старшими разрядам вперёд. Выходной блок выдает разное количество сигналов в зависимости от кода. На рисунке 5.11

представлена схема из RTL Viewer для выходной части устройства.

26

Рисунок 5.11 – Схема из RTL Viewer для выходной части

27

6 МОДЕЛИРОВАНИЕ ФУНКЦИОНАЛЬНОЙ СХЕМЫ, ОПИСАННОЙ

НА HDL

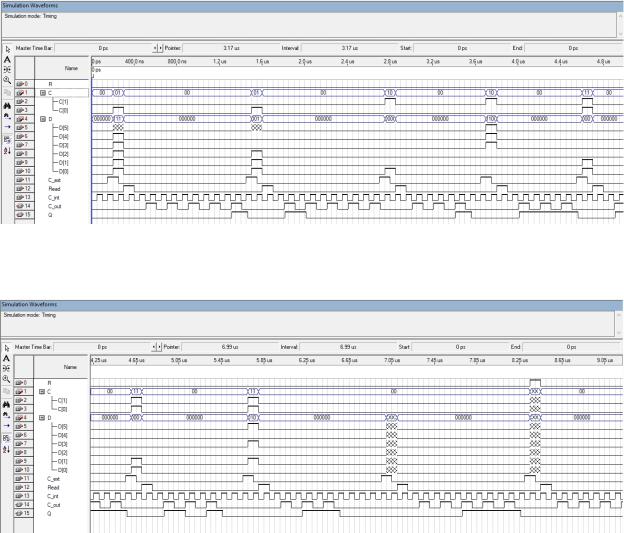

Было произведено моделирование устройства, описанного при помощи

VHDL в режиме «Timing», представленное на рисунках 6.1 – 6.3.

Рисунок 6.1 – Первая часть моделирования функциональной схемы в режиме

«Timing»

Рисунок 6.2 – Вторая часть моделирования функциональной схемы в режиме

«Timing»

28

Рисунок 6.3 – Третья часть моделирования функциональной схемы в режиме

«Timing»

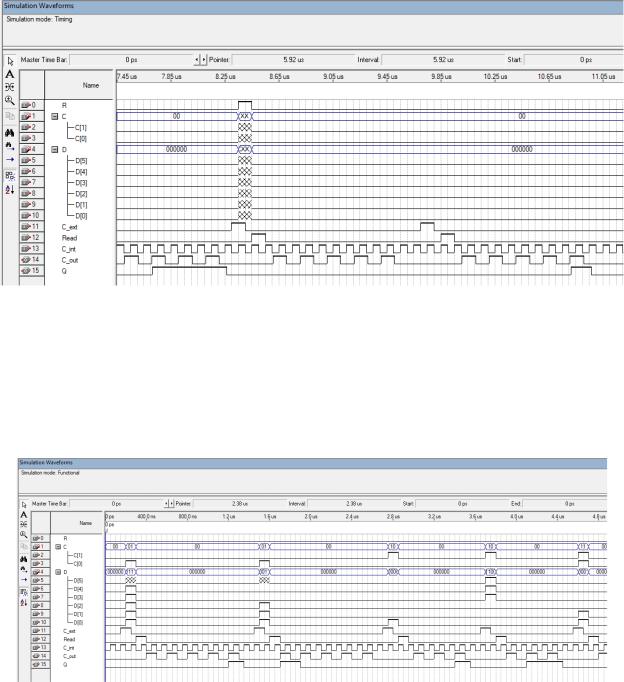

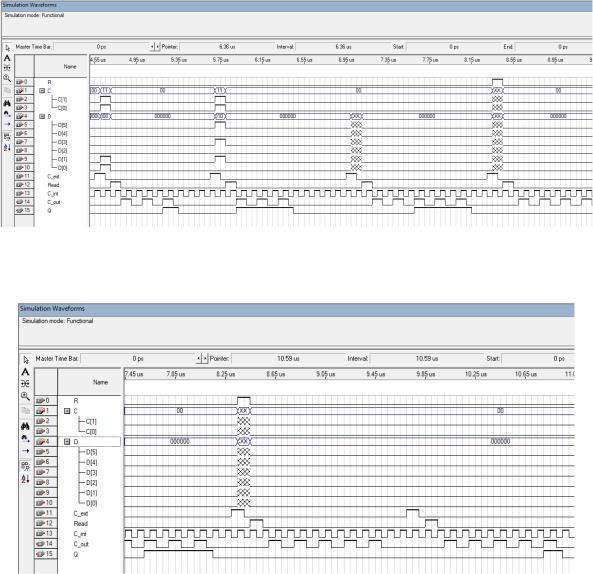

Далее было произведено моделирование устройства, описанного при помощи VHDL в режиме «Timing», представленное на рисунках 6.4 – 6.6.

Рисунок 6.4 – Первая часть моделирования функциональной схемы в режиме

«Functional»

29

Рисунок 6.5 – Вторая часть моделирования функциональной схемы в режиме

«Functional»

Рисунок 6.6 – Третья часть моделирования функциональной схемы в режиме

«Functional»

Результат совпал с предыдущим моделированием, а также с планом моделирования, что говорит о правильном выполнении работы.

30