4 Семестр / Доп лаба 1 / ЭИС2 доп1лаб вер2

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

ШИФРАТОТЫ И ДЕШИФРАТОРЫ

Отчет по дополнительной лабораторной работе №1

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

10.06.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

10.06.2023

Томск 2023

|

Оглавление |

|

Введение................................................................................................................... |

4 |

|

1 ШИФРАТОР 10-4................................................................................................. |

5 |

|

1.1 |

Таблица истинности....................................................................................... |

5 |

1.2 |

Формулы ......................................................................................................... |

5 |

1.3 |

Функциональная схема.................................................................................. |

6 |

1.4 |

Моделирование функциональной схемы..................................................... |

7 |

1.5 |

Описание функциональной схемы на HDL................................................. |

8 |

1.6 |

Схема из RTL Viewer для кода HDL.......................................................... |

10 |

1.7 |

Моделирование устройства, описанного кодом HDL.............................. |

11 |

2 ДЕШИФРАТОР 3-6............................................................................................ |

12 |

|

2.1 |

Таблица истинности..................................................................................... |

12 |

2.2 |

Формулы ....................................................................................................... |

12 |

2.3 |

Функциональная схема................................................................................ |

13 |

2.4 |

Моделирование функциональной схемы................................................... |

13 |

2.5 |

Описание функциональной схемы на HDL............................................... |

14 |

2.6 |

Схема из RTL Viewer для кода HDL.......................................................... |

15 |

2.7 |

Моделирование устройства, описанного кодом HDL.............................. |

16 |

3 ПРИОРИТЕТНЫЙ ШИФРАТОР 4-2 ............................................................... |

18 |

|

3.1 |

Таблица истинности..................................................................................... |

18 |

3.2 |

Формулы ....................................................................................................... |

18 |

3.3 |

Функциональная схема................................................................................ |

18 |

3.4 |

Моделирование функциональной схемы................................................... |

19 |

3.5 |

Описание функциональной схемы на HDL............................................... |

21 |

3.6 |

Схема из RTL Viewer для кода HDL.......................................................... |

22 |

3.7 |

Моделирование устройства, описанного кодом HDL.............................. |

22 |

3.8 |

Таблица истинности масштабируемого устройства................................. |

23 |

3.9 |

Функциональная схема масштабируемого устройства............................ |

23 |

3.10 Моделирование масштабируемого устройства ...................................... |

24 |

|

|

2 |

|

3.11 |

Описание функциональной схемы на HDL масштабируемого |

|

устройства ........................................................................................................... |

25 |

|

3.12 |

Схема из RTL Viewer для кода HDL масштабируемого устройства .... |

27 |

3.13 |

Моделирование масштабируемого устройства, описанного кодом HDL |

|

.............................................................................................................................. |

|

27 |

Заключение ............................................................................................................ |

29 |

|

3

Введение

Цель работы: научиться создавать шифраторы и дешифраторы на

разных базисах и решить задачу увеличения их размерности.

Постановка задачи:

1.составить таблицы истинности для схем согласно варианту №9, а именно для шифратора с количеством входов = 10, для дешифратора с количеством выходов = 6, для приоритетного шифратора с количеством входов = 4. Написать формулы СКНФ/СДНФ для всех выходов используя заданный вариантом базис, а именно для шифратора базис ИЛИ-НЕ, для дешифратора базис И-НЕ, для приоритетного шифратора базис И,ИЛИ,НЕ.

2.собрать необходимые схемы на холстах .bdf для составленных формул согласно варианту №9. Для приоритетного шифратора собрать схему, предполагающую наращивание до количества входов = 8 используя символ приоритетного шифратора с количеством входов = 4.

3.промоделировать работу схем в двух режимах. Провести анализ результатов моделирования разных режимов. Сверить результаты моделирования с составленными таблицами истинности.

5. повторить пункты 2-3, только для описания устройств вместо схем на холстах .bdf используя заданный вариантом язык описания HDL, а именно

VHDL.

6. написать выводы о проделанной работе.

4

1ШИФРАТОР 10-4

1.1Таблица истинности

Таблица истинности для шифратора согласно варианту №9, а именно для шифратора с количеством входов = 10, представлена в таблице 1.1. Таблица 1.1 – Таблица истинности для шифратора

|

|

|

|

Входы |

|

|

|

|

|

|

|

Выходы |

|

|||

E |

|

|

|

|

x |

|

|

|

|

|

|

|

a |

|

G |

|

|

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

3 |

2 |

|

1 |

0 |

|

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1.2 Формулы

Далее были составлены формулы СКНФ/СДНФ для выходов и входов. На базисе ИЛИ-НЕ были составлены следующие формулы для входов:

z0 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ ,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z1 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z2 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z3 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z4 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

5

z5 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E̅ x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z6 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z7 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z8 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ,

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

z9 = ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

(E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0).

Далее были составлены следующие формулы для выходов:

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ , a3 = ( 9 8)

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

̅̅̅ ̅̅̅ ̅̅̅ , a2 = ( 7 6 5 4)

|

̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅ |

||||

|

̅ |

̅̅̅ |

̅̅̅ |

̅ |

|

a1 = ( 7 6 |

3 |

2), |

|||

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

||||

a0 = |

̅̅̅ |

̅̅̅ |

|

̅̅̅ |

̅̅̅ |

( 9 |

7 |

5 3 |

1). |

||

G = z9 z8 z7 z6 z5 z4 z3 z2 z1 z0.

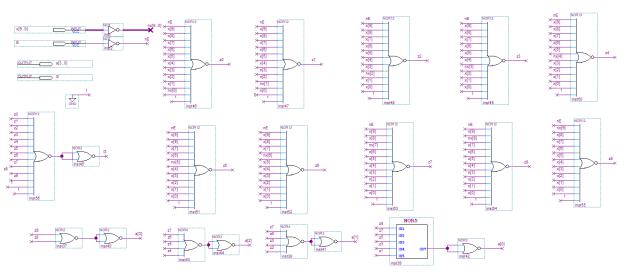

1.3 Функциональная схема

Фунциональная схема для шифратора 10-4 на базисе ИЛИ-НЕ,

представлена на рисунке 1.1

Рисунок 1.1 – Функциональная схема шифратора 10-4

6

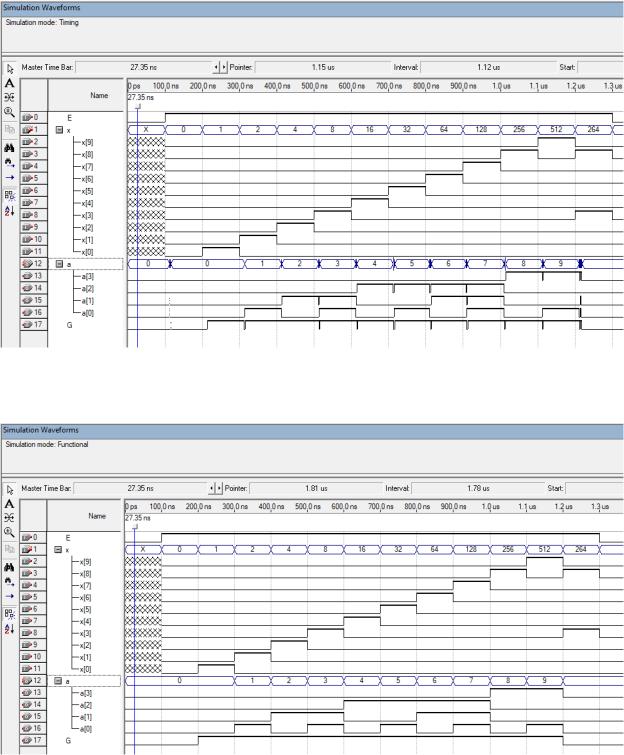

1.4 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 1.2 – 1.3 соответственно.

Рисунок 1.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 1.3 – Моделирование функциональной схемы в режиме «Functional»

7

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

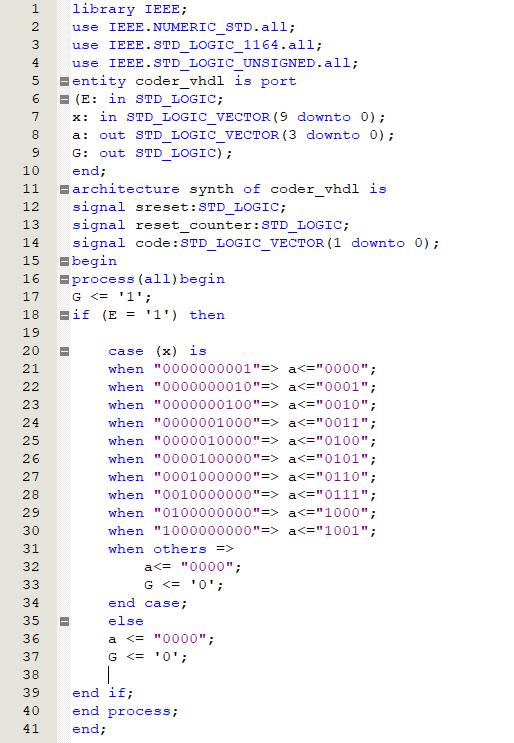

1.5 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры VHDL, представленный на рисунке

1.4.

8

Рисунок 1.4 – Описание функциональной схемы на языке описания аппаратуры VHDL

Входы и выходы описаны в строчках 6 – 9. В строчках 12 – 14

описываются используемые сигналы. В строчках 16 – 40 описывается

шифратор 10-4, путем проверки входных значений и при конкретных

9

значениях на входе происходит выдача определенных значений на выход.

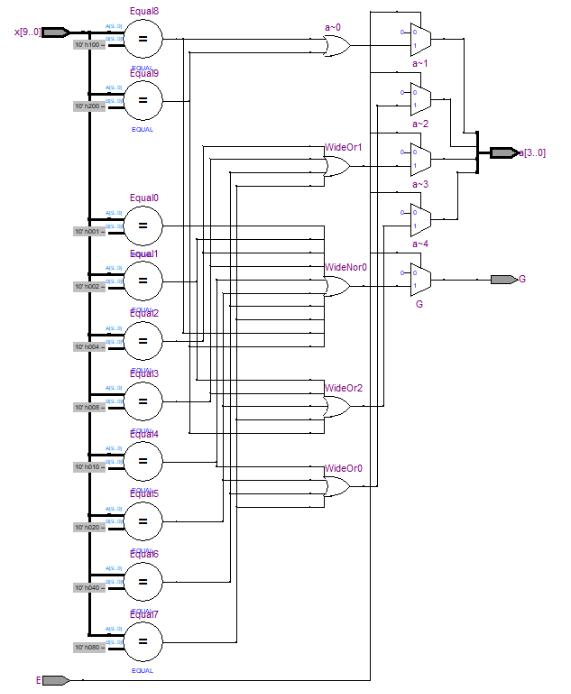

1.6 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.5.

Рисунок 1.5 – Сформированная схема при помощи RTL Viewer

10