4 Семестр / Доп лаба 2 / ЭИС2 доп2лаб

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТЕПЛЕКСОРЫ

Отчет по дополнительной лабораторной работе №2

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

10.06.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

10.06.2023

Томск 2023

|

Оглавление |

|

Введение................................................................................................................... |

4 |

|

1 МУЛЬТИПЛЕКСОР 4-1 ...................................................................................... |

5 |

|

1.1 |

Таблица истинности....................................................................................... |

5 |

1.2 |

Формула .......................................................................................................... |

5 |

1.3 |

Функциональная схема.................................................................................. |

5 |

1.4 |

Моделирование функциональной схемы..................................................... |

6 |

1.5 |

Описание функциональных схем на HDL ................................................... |

7 |

1.6 |

Схема из RTL Viewer для кода HDL............................................................ |

8 |

1.7 |

Моделирование устройства, описанного кодом HDL................................ |

8 |

1.8 |

Таблица истинности масштабируемого устройства................................... |

9 |

1.9 |

Функциональная схема масштабируемого устройства.............................. |

9 |

1.10 Моделирование масштабируемого устройства ...................................... |

10 |

|

1.11 Описание функциональной схемы на HDL масштабируемого |

|

|

устройства ........................................................................................................... |

11 |

|

1.12 Схема из RTL Viewer для кода HDL масштабируемого устройства .... |

12 |

|

1.13 Моделирование масштабируемого устройства, описанного кодом HDL |

||

.............................................................................................................................. |

|

13 |

2 ДЕМУЛЬТИПЛЕКСОР 1-8 ............................................................................... |

14 |

|

2.1 |

Таблица истинности..................................................................................... |

14 |

2.2 |

Формулы ....................................................................................................... |

14 |

2.3 |

Функциональная схема................................................................................ |

15 |

2.4 |

Моделирование функциональной схемы................................................... |

15 |

2.5 |

Описание функциональных схем на HDL ................................................. |

16 |

2.6 |

Схема из RTL Viewer для кода HDL.......................................................... |

17 |

2.7 |

Моделирование устройства, описанного кодом HDL.............................. |

17 |

2.8 |

Таблица истинности масштабируемого устройства................................. |

18 |

2.9 |

Функциональная схема масштабируемого устройства............................ |

19 |

2.10 Моделирование масштабируемого устройства ...................................... |

19 |

|

2.11 Описание функциональной схемы на HDL масштабируемого |

|

|

устройства ........................................................................................................... |

20 |

|

|

2 |

|

2.12 Схема из RTL Viewer для кода HDL масштабируемого устройства .... |

21 |

|

2.13 Моделирование масштабируемого устройства, описанного кодом HDL |

||

.............................................................................................................................. |

|

22 |

3 РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ МУЛЬТИПЛЕКСОРА .............. |

23 |

|

3.1 Таблица истинности..................................................................................... |

23 |

|

3.2 |

Функциональная схема................................................................................ |

23 |

3.3 |

Моделирование функциональной схемы................................................... |

24 |

4 РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ ДЕМУЛЬТИПЛЕКСОРА ......... |

26 |

|

4.1 Таблица истинности..................................................................................... |

26 |

|

4.2 |

Функциональная схема................................................................................ |

26 |

4.3 |

Моделирование функциональной схемы................................................... |

27 |

Заключение ............................................................................................................ |

28 |

|

3

Введение

Цель работы: научиться создавать мультиплексоры и мультиплексоры на разных базисах, а также реализовывать функцию на мультиплексоре и дешифраторе.

Постановка задачи:

1.составить таблицы истинности для схем согласно варианту №9, а именно для мультиплексора 4-1 и наращенной его версии до 8-1, а также для демультиплексора 1-8 и его наращенной версии до 2-16. Написать формулы для всех выходов в виде СКНФ или СДНФ. Привести формулы к базису согласно варианту №9, а именно для мультиплексора в базис ИЛИ-НЕ, для демультиплексора в базис И-НЕ.

2.собрать схемы на холстах .bdf, согласно полученным формулам.

Также собрать схемы для блоков большей размерности используя полученные блоки ранее. Создать две схемы, которые реализуют функцию по формуле из

варианта №9 лабораторной работы №1, а именно F9 = x ̅̅̅̅̅̅̅̅̅ w.

y z

Промоделировать работу схем в двух режимах. Сделать предположение почему возникает разница в результатах моделирования разных режимов, а также сверить результаты моделирования с составленными таблицами истинности.

3. повторить пункт 2 используя HDL согласно варианту №9, а именно на

System Verilog.

6. написать выводы о проделанной работе.

4

1МУЛЬТИПЛЕКСОР 4-1

1.1Таблица истинности

Таблица истинности для мультиплексора согласно варианту №9, а

именно для мультиплексора 4-1 представлена в таблице 1.1.

Таблица 1.1 –Таблица истинности мультиплексора 4-1

|

|

|

Входы |

|

|

|

Выход |

|

|

|

|

|

|

|

|

E |

x3 |

x2 |

x1 |

x0 |

a1 |

a0 |

F |

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

b0 |

0 |

0 |

b0 |

|

|

|

|

|

|

|

|

1 |

x |

x |

b1 |

x |

0 |

1 |

b1 |

|

|

|

|

|

|

|

|

1 |

x |

b2 |

x |

x |

1 |

0 |

b2 |

|

|

|

|

|

|

|

|

1 |

b3 |

x |

x |

x |

1 |

1 |

b3 |

|

|

|

|

|

|

|

|

1.2 Формула

Далее с помощью таблицы истинности была составлена формула для

выхода F в базисе ИЛИ-НЕ:

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

̅̅̅ ̅̅̅̅̅̅̅̅ ̅̅̅ ̅̅ ̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅ ̅̅̅̅ ̅̅ ̅

( 0 a1 a0) ( 1 a1 0) ( 2 1 a0) 3 1 0)

1.3 Функциональная схема

Функциональная схема для мультиплексора 4-1 представлена на рисунке

1.1.

5

Рисунок 1.1 – Функциональная схема

1.4 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 1.2 – 1.3 соответственно.

Рисунок 1.2 – Моделирование функциональной схемы в режиме «Timing»

6

Рисунок 1.3 – Моделирование функциональной схемы в режиме «Functional»

Из-за того, что в режиме работе «Timing» учитывается задержка на элементах, происходят выходы за границы интервала. Результат моделирования совпал с таблицей истинности.

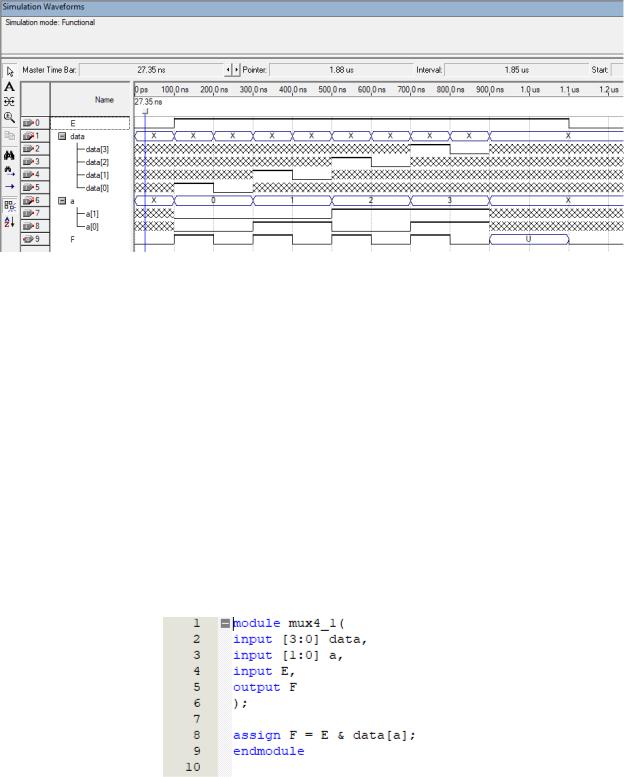

1.5 Описание функциональных схем на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 1.4.

Рисунок 1.4 – Код на языке описания аппаратуры SystemVerilog

Входы и выходы описаны в строчках 2 – 5. В строчке 8 описывается мультиплексор.

7

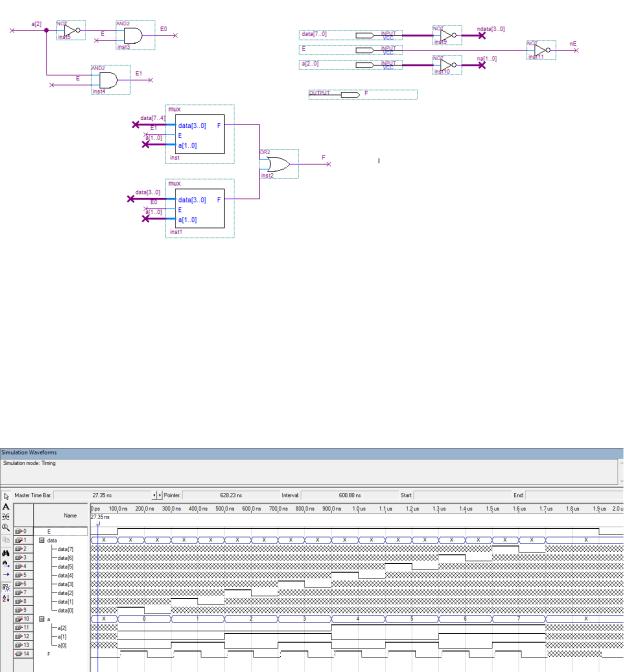

1.6 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 1.5.

Рисунок 1.5 – Сформированная схема при помощи RTL Viewer

1.7 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 1.6.

Рисунок 1.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

8

Результат совпал с предыдущим моделированием, а также с таблицей

истинности.

1.8 Таблица истинности масштабируемого устройства

Таблица истинности для масштабируемого мультиплексора согласно варианту №9, а именно для масштабируемого мультиплексора 8-1,

представлена в таблице 1.2.

Таблица 1.2 – Таблица истинности для масштабируемого мультиплексора

|

|

|

|

|

Входы |

|

|

|

|

|

Выход |

|

E |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

a2 |

a1 |

a0 |

F |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

1 |

x |

x |

x |

x |

x |

x |

x |

b0 |

0 |

0 |

0 |

b0 |

1 |

x |

x |

x |

x |

x |

x |

b1 |

x |

0 |

0 |

1 |

b1 |

1 |

x |

x |

x |

x |

x |

b2 |

x |

x |

0 |

1 |

0 |

b2 |

1 |

x |

x |

x |

x |

b3 |

x |

x |

x |

0 |

1 |

1 |

b3 |

1 |

x |

x |

x |

b4 |

x |

x |

x |

x |

1 |

0 |

0 |

b4 |

1 |

x |

x |

b5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

b5 |

1 |

x |

b6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

b6 |

1 |

b7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

b7 |

1.9 Функциональная схема масштабируемого устройства

Фунциональная схема для масштабируемого мультиплексора 8-1,

представлена на рисунке 1.7.

9

Рисунок 1.7 – Функциональная схема мультиплексора 8-1

1.10 Моделирование масштабируемого устройства

Далее было проведено моделирование построенной схемы в режимах

«Timing» и «Functional», представленное на рисунках 1.8 – 1.9 соответственно.

Рисунок 1.8 – Моделирование функциональной схемы в режиме «Timing»

10