Лекции_15_счётчики

.pdf

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

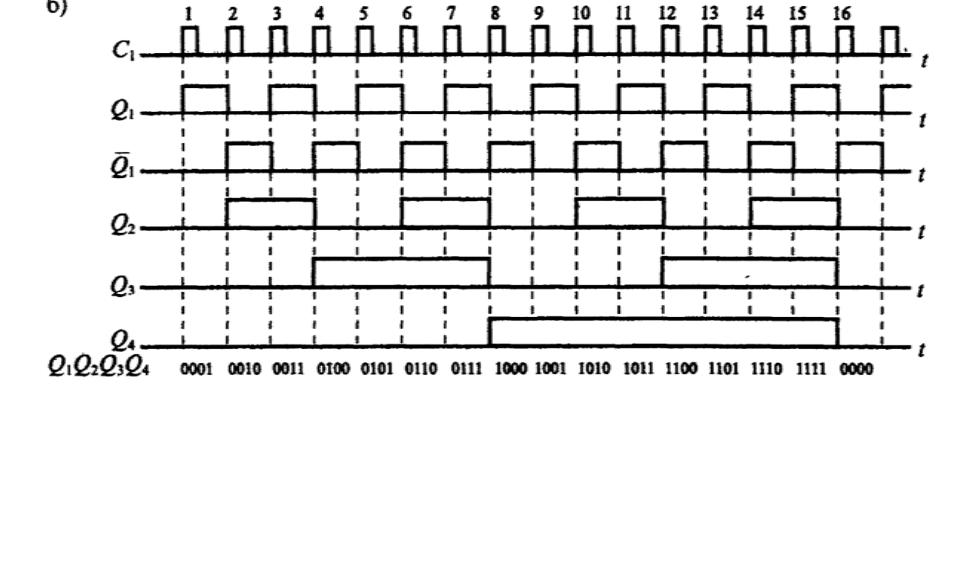

При поступлении счетных импульсов на вход C

1

триггеры счетчика будут изменять свои состояния, описываемые последовательно возрастающими двоичными числами.

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Таблица состояний выходов четырехразрядного асинхронного двоичного счетчика

|

n |

Q4 |

Q3 |

Q2 |

Q1 |

n |

Q4 |

Q3 |

Q2 |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

9 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

10 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

12 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

13 |

1 |

1 |

0 |

1 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

14 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

15 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

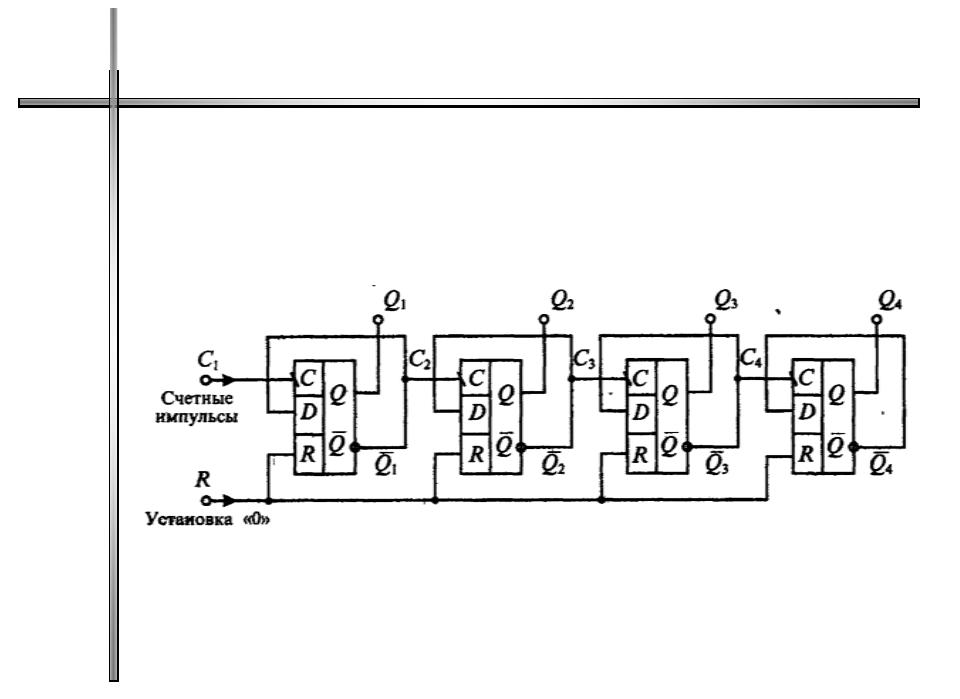

При построении асинхронного вычитающего

счетчика достаточно заменить инверсные выходы Q D- триггеров на прямые выходы Q.

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Схема асинхронного суммирующего счетчика на D-триггерах

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

В этом случае при поступлении импульса сброса R на всех выходах счетчика установятся единичные уровни, а при поступлении счетных импульсов на вход C1 триггеры счетчика будут изменять свои состояния, описываемые последовательно убывающими двоичными числами.

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Для построения асинхронного реверсивного

счетчика, можно с помощью логической схемы обеспечить подачу сигналов с инверсного выхода Q при суммировании или с прямого выхода Q при вычитании от предыдущего, триггера на счетный вход последующего.

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

Эта схема включается между выходом одного

разряда счетчика и входом другого и в зависимости от управляющих сигналов сложение (U) или вычитание (D), на вход последующего разряда поступает сигнал переноса Р или сигнал займа Z.

Райков Д.В., кафедра экспериментальной физики

Райков Д.В., кафедра экспериментальной физики

В асинхронном счетчике с приходом каждого последующего импульса на вход C1 переключаются сразу несколько триггеров. Переключение этих триггеров происходит с некоторой задержкой относительно друг друга, это приводит к задержке установления выходного кода.