AVR / at-avr

.pdf

ÊÒÖ-ÌÊ

ADSC будет сохранять состояние 1 в течение всего цикла преобр азования и сбрасывается по завершении преобразования. При выполнен ии пустого преобразования, предшествующего активируемому, бит ADSC остается установле нным до завершения активируемого преобразования. Запись 0 в этот бит эффекта не оказывает.

• Bit 5 - ADFR: ADC Free Run Select - Установка циклического режима работы ADC

При установленном в состояние 1 бите ADFR ADC будет работать в ци клическом режиме. В этом режиме ADC производит выборки и обращения к ре гистрам непрерывно (одно за другим). Очистка бита приводит к прекращению цикл ического режима.

• Bit 4 -ADIF: ADC Interrupt Flag - Флаг прерывания ADC

Данный бит устанавливается в состояние 1 по завершению пр еобразования и обновления регистров данных. Прерывание по завершению преобразования ADC выполняется если в состояние 1 установлены бит ADIE и I-бит рег истра SREG. Бит ADIF сбрасывается аппаратно при выполнении подпрограммы обр аботки соответствующего вектора прерывания. Кроме того, бит ADIF может быть очищен зап исью во флаг логической 1. Этого необходимо остерегаться при чтении-мо дификации-записи ADCSR, поскольку может быть запрещено отложенное прерывание. Эт о применимо и в случаях использования команд SBI и CBI.

• Bit 3 - ADIE: ADC Interrupt Enable - Разрешение прерывания ADC

При установленных в состояние 1 бите ADIE и I-бите регистра SREG ак тивируется прерывание по завершению преобразования ADC.

• Bits 2..0 - ADPS2..ADPS0: ADC Prescaler Select Bits - Выбор коэффициента предварительного деления

Данные биты определяют коэффициент деления частоты XTAL для получения необходимой тактовой частоты ADC.

Таблица 26. Выбор коэффициента предварительного деления

ADPS2 |

ADPS1 |

ADPS0 |

Коэффициент деления |

0 |

0 |

0 |

Без деления |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

4 |

0 |

1 |

1 |

8 |

1 |

0 |

0 |

16 |

1 |

0 |

1 |

32 |

1 |

1 |

0 |

64 |

1 |

1 |

1 |

128 |

РЕГИСТРЫ ДАННЫХ ADC - ADCL и ADCH - (ADC Data Register)

Áèò |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

$05 ($25) |

- |

- |

- |

- |

- |

- |

ADC9 |

ADC8 |

ADCH |

$04 ($24) |

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADC1 |

ADC0 |

ADCL |

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Чтение/Запись |

R |

R |

R |

R |

R |

R |

R |

R |

|

|

R |

R |

R |

R |

R |

R |

R |

R |

|

Начальное значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

По завершении цикла преобразования результат преобразо вания размещается в этих двух регистрах. Важно, чтобы в циклическом режиме сч итывались оба регистра и чтобы регистр ADCL считывался перед считыванием ADCH.

127

ATMEL |

ÊÒÖ-ÌÊ |

Сканирование аналоговых каналов

Поскольку смена аналоговых каналов происходит после зав ершения цикла преобразования в циклическом режиме смена каналов (скани рование каналов) может происходить без прерывания преобразователя. Обычно для в ыполнения смены канала выполняется прерывание по завершению преобразования. Од нако пользователю необходимо принять к сведению следующее соображение: пре рывание активируется сразу по готовности результата к считыванию. В циклическо м режиме следующее преобразование начинается через один тактовый цикл ADC пос ле активации прерывания. Если содержимое ADMUX будет изменено в течение эт ого одного тактового цикла, то новые установки будут задействованы при начале нового преобразования. Если же изменение состояния ADMUX произойдет позднее этого т актового цикла, то при активированном преобразовании будут использоваться предшествовавшие установки.

Технология подавления шума ADC

Цифровые схемы самого микроконтроллера ATmega603/103 и внешние цифровые схемы генерируют электромагнитное излучение, к оторое может влиять на точность измерения аналоговых сигналов. Если точность пр еобразования является определяющей, то можно использовать следующие приемы:

1.Аналоговая часть ATmega603/103 и все аналоговые компоненты устройства должны иметь на печатной плате отдельную аналоговую землю. Эта а налоговая земля должна иметь соединение с цифровой землей в одной точке печатной платы.

2.Проводники аналоговых сигналов необходимо делать как можно короче, стремиться проводить их поверх аналоговой земли и, по возможности, ка к можно дальше от дорожек высокоскоростных цифровых сигналов.

3.Вывод AVCC микроконтроллеров ATmega603/103 должен подключаться к напряжению питания VCC через RC цепочку, как показано на Рис. 47.

4.Для подавления шума CPU можно использовать функцию подавления шума ADC

5.Åñëè какие-то выводы PORTF используются в качестве цифровых входов, то важно, чтобы в процессе преобразования на этих выводах не происх одили переключения.

Характеристики ADC по постоянному току

Температура окружающей среды TA= от -40°C до 85°C

Oбознач. |

Параметр |

Условия |

Min |

|

Typ |

Max |

Ед. измерения |

|

Разрешение |

|

|

|

10 |

|

Áèòû |

|

Интегральная нелинейность |

VREF > 2V |

|

|

0,2 |

0,5 |

LSB |

|

Дифференциальная нелинейность |

VREF > 2V |

|

|

0,2 |

0,5 |

LSB |

|

Ошибка нуля (смещение) |

|

|

|

1 |

|

LSB |

|

Время преобразования |

|

70 |

|

|

280 |

ìêñ |

|

Тактовая частота |

|

50 |

|

|

200 |

êÃö |

AV |

Аналоговое напряжение питания |

|

V |

-0,3(1) |

|

V +0,3(2) |

|

CC |

|

|

CC |

|

|

CC |

|

VREF |

Напряжение сравнения |

|

AGND |

|

AVCC |

|

|

RREF |

Входное сопротивление |

|

6 |

|

10 |

13 |

êÎì |

|

входа сравнения |

|

|

|

|

|

|

RAIN |

Входное сопротивление |

|

|

|

100 |

|

ÌÎì |

|

аналогового входа |

|

|

|

|

|

|

Примечания: 1. Минимальное при AVCC=2,7B 2. Максимальное при AVCC=6,0B

128

ÊÒÖ-ÌÊ

(AD0)PA0 51 |

|

|||

|

Vcc |

|

|

|

|

|

52 |

|

|

|

GND 53 |

|

||

(ADC7)PF7 54 |

|

|||

(ADC6)PF6 55 |

|

|||

(ADC5)PF5 |

56 |

ATmega103L |

||

(ADC4)PF4 57 |

||||

|

||||

(ADC3)PF3 58 |

|

|||

(ADC2)PF2 59 |

|

|||

(ADC1)PF1 60 |

|

|||

(ADC0)PF0 61 |

|

|||

100R |

AREF 62 |

|

||

|

AGND 63 |

|

||

|

AVCC 64 |

|

||

10 íÔ |

|

|

1 |

|

Аналоговая земля |

|

PEN |

||

|

|

|

||

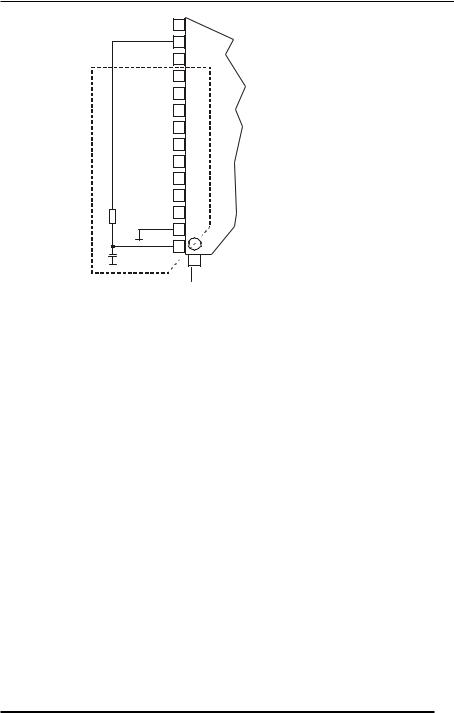

Рис. 47. Подключение напряжения питания ADC

Порты I/O

Ïîðò A

Порт A является 8-разрядным двунаправленным I/O портом и осна щен встроенными нагрузочными резисторами.

Взаимодействие с портом A осуществляется тремя расположе нными в пространстве I/O памяти данных регистрами: регистром данны х - PORTA, $1B($3B), регистром направления данных - DDRA, $1A($3A) и регистром адресов в ыводов входа - PINA, $19($39). Регистр адресов выводов входа порта A обеспечивает в озможность только чтения, регистры данных и направления данных порта A обеспечивают возможность и чтения и записи. Все выводы порта A оснащены и ндивидуально подключаемыми встроенными нагрузочными резисторами.

Выходные буферы выводов порта A обеспечивают втекающий то к до 40 мА, что достаточно для прямого управления LED дисплеями. Если вывод ы с PA0 по PA7 используются в качестве входов и внешним сигналом удержи ваются на низком уровне, то вытекающий ток обеспечивается подключением внутренн их нагрузочных резисторов. Выводы порта A могут выполнять, дополнительную к основной функции, функцию обеспечения взаимодействия с внешней дополнительной SRAM д анных - они могут быть сконфигурированы как младшие разряды шины адреса/да нных внешней SRAM данных.

Дополнительная функция включается установкой бита SRE (раз решение внешней SRAM) в регистре управления MCU (MCUCR), при этом установки регистра направления данных игнорируются.

129

ATMEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ÊÒÖ-ÌÊ |

РЕГИСТР ДАННЫХ ПОРТА A - PORTA - (PORT A Data Register) |

|

||||||||||||||

Áèò |

7 |

|

|

6 |

|

5 |

|

|

4 |

3 |

2 |

1 |

|

0 |

|

$1B ($3B) |

PORTA7 |

PORTA6 |

PORTA5 |

PORTA4 |

PORTA3 |

PORTA2 |

PORTA1 |

PORTA0 |

PORTA |

||||||

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

||||||

Начальное значение |

0 |

|

|

0 |

|

0 |

|

|

0 |

0 |

0 |

0 |

|

0 |

|

РЕГИСТР НАПРАВЛЕНИЯ ДАННЫХ ПОРТА A - |

|

|

|

|

|

||||||||||

DDRA - (PORT A Data Direction Register) |

|

|

|

|

|

|

|||||||||

Áèò |

7 |

|

|

6 |

|

5 |

|

|

4 |

3 |

2 |

1 |

|

0 |

|

$1A ($3A) |

DDA7 |

|

|

DDA6 |

|

DDA5 |

|

|

DDA4 |

DDA3 |

DDA2 |

DDA1 |

|

DDA0 |

DDRA |

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

||||||

Начальное значение |

0 |

|

|

0 |

|

0 |

|

|

0 |

0 |

0 |

0 |

|

0 |

|

РЕГИСТР ВЫВОДОВ ВХОДА ПОРТА A - |

|

|

|

|

|

|

|||||||||

PINA - (PORT A Input Pins Address) |

|

|

|

|

|

|

|

||||||||

Áèò |

7 |

|

|

6 |

|

5 |

|

|

4 |

3 |

2 |

1 |

|

0 |

|

$19 ($39) |

PINA7 |

|

PINA6 |

PINA5 |

|

PINA4 |

PINA3 |

PINA2 |

PINA1 |

PINA0 |

PINA |

||||

Чтение/Запись |

R |

R |

R |

R |

R |

R |

R |

R |

|

||||||

Начальное значение |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

|

||||||

PINA - адрес выводов входа порта A не является регистром в полн ом смысле этого слова, и эти адреса обеспечивают считывание физичес кого состояния каждого вывода порта. При считывании PORTA считывается состояние фик саторов данных порта A , а при считывании PINA считываются непосредственно логичес кие состояния выводов.

РАБОТА ПОРТА A В КАЧЕСТВЕ ЦИФРОВОГО I/O ОБЩЕГО НАЗНАЧЕНИЯ

Все 8 битов порта A при их использовании в качестве цифровог о I/O работают одинаково.

Таблица 27. Воздействие битов DDAn на характер работы выводов порта A

DDAn |

PORTAn |

I/O |

Нагрузочный резистор |

Описание |

0 |

0 |

Âõîä |

Не подключен |

Третье состояние (Hi-Z) |

0 |

1 |

Âõîä |

Подключен |

При низком уровне PAn обеспечивают |

|

|

|

|

вытекающий ток. |

|

|

|

|

|

1 |

0 |

Выход |

Не подключен |

Низкий уровень, двухтактный выход |

1 |

1 |

Выход |

Не подключен |

Высокий уровень, двухтактный выход |

Примечание: PAn - выводы I/O общего назначения, n=7, 6, ... 1, 0 - номера выво дов порта A.

Биты DDAn регистра DDRA определяют направление работы соответс твующего вывода. При установленном в состояние 1 бите DDAn вывод PAn конфи гурируется как вывод выхода. При очищенном бите DDAn (сброшенном в 0) вывод PAn ко нфигурируется как вывод входа.

Если бит PORTAn установлен в состояние 1, когда соответствующий вывод сконфигурирован как вход, то нагрузочный MOS резистор актив ируется (подключается). Для отключения нагрузочного резистора бит PORTAn необходимо очистить или же необходимо сконфигурировать вывод как выход.

130

ÊÒÖ-ÌÊ |

|

|

|

|

|

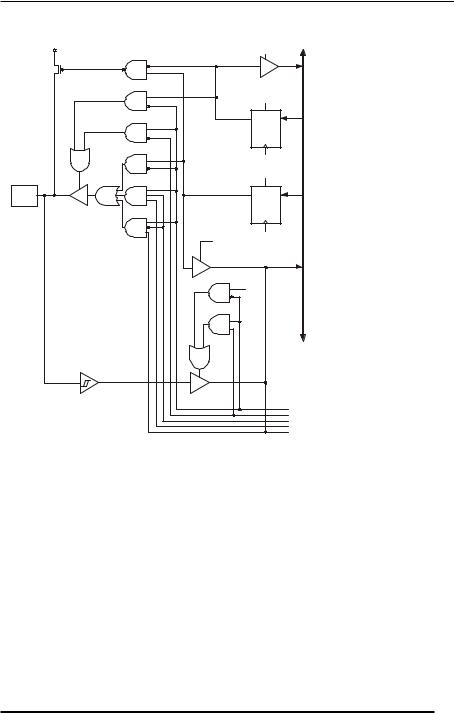

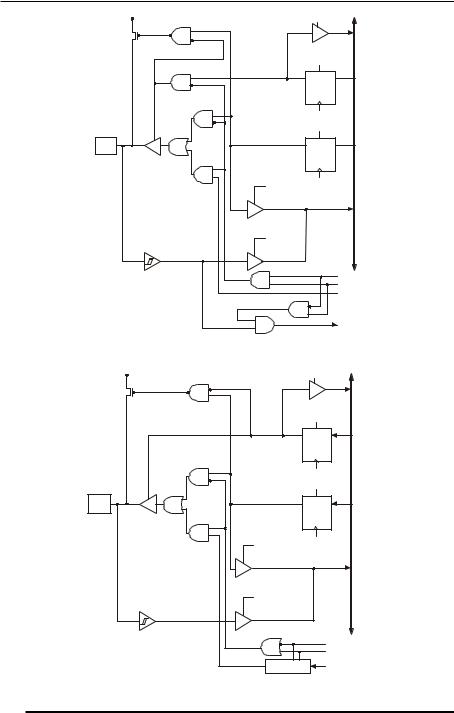

СХЕМОТЕХНИКА ПОРТА A |

|

|

|

|

|

Каждый из выводов порта синхронизирован, однако на рисунк е защелка |

|||||

синхронизации не показана. |

|

RD |

|

|

|

|

|

|

|

|

|

Нагрузочный |

|

|

|

|

|

MOS |

|

|

|

|

|

резистор |

|

|

|

|

|

|

Сброс |

|

|

||

|

Q |

R |

D |

|

|

|

DDAn |

|

|

|

|

|

|

C |

|

|

|

|

|

WD |

|

|

|

|

Сброс |

данных |

|

||

Вывод |

Q |

R |

D |

|

|

PAn |

PORT An |

Øèíà |

|

||

|

|

||||

|

|

C |

|

|

|

|

|

|

|

|

|

|

RL |

WP |

|

|

|

|

|

|

|

|

|

An Dn W R SRE |

|

|

|

|

|

|

RP |

|

|

|

|

|

|

|

|

WP: |

Запись PORTA |

|

|

|

|

WD: |

Запись DDRA |

|

|

|

|

RL: |

Чтение фиксатора PORTA |

|

|

|

|

RP: |

Чтение состояния вывода PORTA |

|

|

|

|

RD: |

Чтение DDRA |

|

|

|

|

SRE: |

Разрешение внешней SRAM |

|

|

|

|

A: |

Адрес |

|

|

|

|

D: |

Данные |

|

|

|

SRE |

W: |

Запись |

|

|

|

R: |

Чтение |

|

|

|

|

R |

||

|

|

|

W |

n: |

0-7 |

|

|

|

Dn |

||

|

|

|

An |

|

|

Рис. 48 Схема организации вывода порта A (выводы PA0 - PA7) |

|||||

Ïîðò B

Порт B является 8-разрядным двунаправленным I/O портом и осна щен встроенными нагрузочными резисторами.

Взаимодействие с портом B осуществляется тремя расположе нными в пространстве I/O памяти данных регистрами: регистром данных - PORTB, $18($38), регист ром направления данных - DDRB, $17($37) и регистром адресов выводов вхо да - PINB, $16($36). Регистр адресов выводов входа порта B обеспечивает воз можность только чтения, регистры данных и направления данных порта B обесп ечивают возможность и чтения и записи. Все выводы порта B оснащены индивидуально подключаемыми встроенными нагрузочными резисторами.

Выходные буферы выводов порта B обеспечивают втекающий то к до 40 мА, что достаточно для прямого управления LED дисплеями. Если вывод ы с PB0 по PB7 используются в качестве входов и внешним сигналом удержи ваются на низком уровне, то вытекающий ток обеспечивается подключением внутренн их нагрузочных резисторов. Выводы порта B могут выполнять, дополнительно к основной ф ункции, функции, представленные в Таблице 29.

131

ATMEL ÊÒÖ-ÌÊ

|

Таблица 28. Дополнительные функции выводов порта B |

|||

|

|

|

|

|

Вывод порта |

Дополнительная функция |

|||

PB0 |

|

Вход выбора ведомого - |

|

(SPI Slave Select input) |

|

SS |

|||

PB1 |

|

Тактовый сигнал последовательной SPI шины - SCK (SPI Bus Serial Clock) |

||

PB2 |

|

Установка Ведущий выход/Ведомый вход SPI шины - |

||

|

|

MOSI (SPI Bus Master Output/Slave Input) |

||

PB3 |

|

Установка Ведущий вход/Ведомый выход SPI шины - |

||

|

|

MISO (SPI Bus Master Input/Slave Output) |

||

PB4 |

|

Сравнение выхода и PWM выход таймера/счетчика0 - |

||

|

|

OC0A/PWM0A (Output Compare and PWM Output for Timer/Counter0) |

||

PB5 |

|

Сравнение выхода и PWM выход A таймера/счетчика1 - |

||

|

|

OC1A/PWM1A (Output Compare and PWM Output A for Timer/Counter1) |

||

PB6 |

|

Сравнение выхода и PWM выход B таймера/счетчика1 - |

||

|

|

OC1B/PWM1B (Output Compare and PWM Output B for Timer/Counter1) |

||

PB7 |

|

Сравнение выхода и PWM выход таймера/счетчика2 - |

||

|

|

OC2/PWM2 (Output Compare and PWM Output for Timer/Counter2 |

||

Включение выводов для выполнения дополнительных функци й производится посредством регистров DDRB и PORTB.

РЕГИСТР ДАННЫХ ПОРТА B - PORTB - (PORT B Data Register)

Áèò |

7 |

|

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

|

$18 ($38) |

PORTB7 |

PORTB6 |

PORTB5 |

PORTB4 |

PORTB3 |

PORTB2 |

PORTB1 |

PORTB0 |

PORTB |

|||||||||

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

|||||||||

Начальное значение |

0 |

|

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

|

РЕГИСТР НАПРАВЛЕНИЯ ДАННЫХ ПОРТА B - |

|

|

|

|

|

|

|

|||||||||||

DDRB - (PORT B Data Direction Register) |

|

|

|

|

|

|

|

|

|

|||||||||

Áèò |

7 |

|

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

|

$17 ($37) |

DDB7 |

|

DDB6 |

|

DDB5 |

|

DDB4 |

|

DDB3 |

|

DDB2 |

|

DDB1 |

|

DDB0 |

|

DDRB |

|

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

|||||||||

Начальное значение |

0 |

|

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

|

РЕГИСТР ВЫВОДОВ ВХОДА ПОРТА B - |

|

|

|

|

|

|

|

|

|

|||||||||

PINB - (PORT B Input Pins Address) |

|

|

|

|

|

|

|

|

|

|

|

|||||||

Áèò |

7 |

|

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

|

$16 ($36) |

PINB7 |

|

|

PINB6 |

|

PINB5 |

|

PINB4 |

|

PINB3 |

|

PINB2 |

|

PINB1 |

|

PINB0 |

|

PINB |

Чтение/Запись |

R |

R |

R |

R |

R |

R |

R |

R |

|

|||||||||

Начальное значение |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

Hi-Z |

|

|||||||||

PINB - адрес выводов входа порта B не является регистром в полн ом смысле этого слова, эти адреса обеспечивают считывание физическ ого состояния каждого вывода порта. При считывании PORTB считывается состояние фиксаторов данных порта B , а при считывании PINB считываются непосредственно логически е состояния выводов.

РАБОТА ПОРТА B В КАЧЕСТВЕ ЦИФРОВОГО I/O ОБЩЕГО НАЗНАЧЕНИЯ

Все 8 битов порта B при их использовании в качестве цифровог о I/O работают одинаково.

132

ÊÒÖ-ÌÊ

Таблица 29 Воздействие битов DDBn на характер работы выводов порта B

DDBn |

PORTBn |

I/O |

Нагрузочный резистор |

Описание |

0 |

0 |

Âõîä |

Не подключен |

Третье состояние (Hi-Z) |

0 |

1 |

Âõîä |

Подключен |

При низком уровне PBn обеспечивают |

|

|

|

|

вытекающий ток. |

1 |

0 |

Выход |

Не подключен |

Низкий уровень, двухтактный выход |

1 |

1 |

Выход |

Не подключен |

Высокий уровень, двухтактный выход |

Примечание: PBn - выводы I/O общего назначения, n=7, 6, ... 1, 0 - номера выво дов порта B.

Биты DDBn регистра DDRB определяют направление работы соответс твующего вывода. При установленном в состояние 1 бите DDBn вывод PBn конфи гурируется как вывод выхода. При очищенном бите DDBn (сброшенном в 0) вывод PBn ко нфигурируется как вывод входа.

Если бит PORTBn установлен в состояние 1, когда соответствующий вывод сконфигурирован как вход, то нагрузочный MOS резистор актив ируется (подключается). Для отключения нагрузочного резистора бит PORTBn необходимо очистить или же необходимо сконфигурировать вывод как выход.

ДОПОЛНИТЕЛЬНЫЕ ФУНКЦИИ ВЫВОДОВ ПОРТА B

Дополнительные функции выводов порта B следующие:

• OC2/PWM2, Áèò 7

Вывод сравнения выхода таймера/счетчика2 (OC2) или PWM выход тай мера/счетчика2, находящегося в PWM режиме. Для выполнения этих функций вывод должен быть сконфигурирован как выход.

• OC1B/PWM1B, Áèò 6

Вывод сравнения выхода B таймера/счетчика1 (OC1B) или PWM выход B т аймера/ счетчика1, находящегося в PWM режиме. Для выполнения этих фун кций вывод должен быть сконфигурирован как выход.

• OC1A/PWM1A, Áèò 5

Вывод сравнения выхода A таймера/счетчика1 (OC1A) или PWM выход A т аймера/ счетчика1, находящегося в PWM режиме. Для выполнения этих фун кций вывод должен быть сконфигурирован как выход.

• OC0/PWM0, Áèò 4

Вывод сравнения выхода таймера/счетчика0 (OC0) или PWM выход тай мера/счетчика0, находящегося в PWM режиме. Для выполнения этих функций вывод должен быть сконфигурирован как выход.

• MISO - PORTB, Áèò3

Определяет вывод SPI канала как вход данных в режиме ведущег о или как выход данных в режиме ведомого. При разрешении SPI как ведущего, эт от вывод конфигурируется как вход, независимо от установки бита DDB3.

При разрешении SPI как ведомого направление данных на этом в ыводе управляется битом DDB3 и, если вывод определен как вход, подключение нагру зочного резистора управляется битом PORTB3. Подробности см. в описании SPI порта.

• MOSI - PORTB, Áèò 2

Вывод SPI канала, определяемый в ведущем режиме SPI как вход да нных и как выход данных в ведомом режиме. При SPI разрешенном как ведомый это т бит конфигурируется как вход, независимо от состояния бита DDB2. При разрешении SPI к ак ведущего направление данных на этом выводе управляется битом DDB2 и, е сли вывод определен

133

ATMEL |

ÊÒÖ-ÌÊ |

как вход, подключение нагрузочного резистора управляетс я битом PORTB2. Подробности см. в описании SPI порта.

• SCK - PORTB, Áèò 1

Выход тактового сигнала в ведущем режиме SPI канала, вход та ктового сигнала в ведомом режиме SPI канала. При SPI разрешенном как ведомый этот бит кон фигурируется как вход, независимо от состояния бита DDB1. При разрешении SPI как в едущего направление данных на этом выводе управляется битом DDB1 и, е сли вывод определен как вход, подключение нагрузочного резистора управляетс я битом PORTB1. Подробности см. в описании SPI порта.

• SS - PORTB, Áèò 0

Вход выбора порта как ведомого. При SPI разрешенном как ведо мый этот бит конфигурируется как вход, независимо от состояния бита DDB0. Как ведомый SPI активируется когда на этот вход подан низкий уровень. При SPI разрешенном в качестве ведущего, направление данных на этом выводе управляется с остоянием бита DDB0. Если вывод определен как вход, подключение нагрузочного р езистора управляется битом PORTB0. Подробности см. в описании SPI порта.

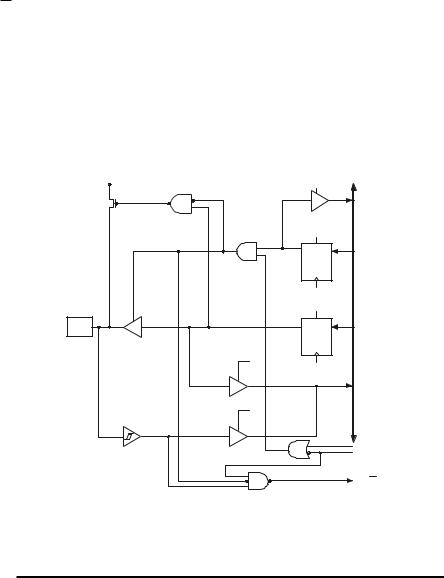

СХЕМОТЕХНИКА ПОРТА B

Каждый из выводов порта синхронизирован, однако на рисунк е защелка синхронизации не показана.

|

|

|

RD |

|

|

|

Нагрузочный |

|

|

|

|

|

MOS |

|

|

|

|

|

резистор |

|

|

|

|

|

|

Сброс |

|

||

|

|

Q |

R |

D |

|

|

|

DDB0 |

|

|

|

|

|

|

C |

|

|

|

|

|

WD |

|

данных |

|

PB0 |

Q |

R |

D |

|

|

|

Сброс |

|

||

|

|

PORTB0 |

Øèíà |

||

|

|

|

C |

|

|

|

|

RL |

WP |

|

|

|

|

|

|

|

|

|

|

RP |

|

|

|

|

|

|

|

|

MSTR |

WP: Запись PORTB |

|

|

|

SPE |

|

|

|

|

|

||

WD: Запись DDRB |

|

|

|

SPI SS |

|

RL: |

Чтение фиксатора PORTB |

|

|

|

|

|

|

|

|

||

RP: |

Чтение состояния вывода PORTB |

|

|

|

|

RD: |

Чтение DDRB |

|

|

|

|

MSTR:Разрешение ведущего режима SPI |

|

|

|

|

|

SPE: Разрешение SPI

Рис. 49 Схема организации вывода порта B (вывод PB0)

134

ÊÒÖ-ÌÊ

RD

Нагрузочный MOS резистор

Сброс

Вывод

PÂ1

Q R D

DDB1

C

WD

Сброс

Q R D

PORTB1

C

WP

RL

RP

Шина данных

WP: Запись PORTB

WD: Запись DDRB

RL: Чтение фиксатора PORTB

RP: Чтение состояния вывода PORTB RD: Чтение DDRB

MSTR:Разрешение ведущего режима SPI SPE: Разрешение SPI

MSTR

SPE

Выход тактового сигнала SPI

Вход тактового сигнала SPI

Рис. 50 Схема организации вывода порта B (вывод PB1)

|

Нагрузочный |

|

RD |

|

|

|

|

|

|

|

|

|

MOS |

|

|

|

|

|

резистор |

|

|

|

|

|

|

Сброс |

|

||

|

|

Q |

R |

D |

|

|

|

DDB2 |

|

|

|

|

|

|

C |

|

|

|

|

WD |

|

данных |

|

|

Вывод |

Q |

R |

D |

|

|

|

Сброс |

|

||

|

PÂ2 |

PORTB2 |

Øèíà |

||

|

|

||||

|

|

|

C |

|

|

|

|

RL |

WP |

|

|

|

|

|

|

|

|

|

|

RP |

|

|

|

WP: |

Запись PORTB |

|

|

|

MSTR |

WD: |

Запись DDRB |

|

|

|

SPE |

|

|

|

Выход SPI в |

||

RL: |

Чтение фиксатора PORTB |

|

|

|

|

|

|

|

ведущем режиме |

||

RP: |

Чтение состояния вывода PORTB |

|

|

|

|

|

|

|

|

||

RD: |

Чтение DDRB |

|

|

|

|

MSTR: Разрешение ведущего режима SPI |

|

|

|

Âõîä SPI â |

|

|

|

|

|

|

|

SPE: |

Разрешение SPI |

|

|

|

ведомом режиме |

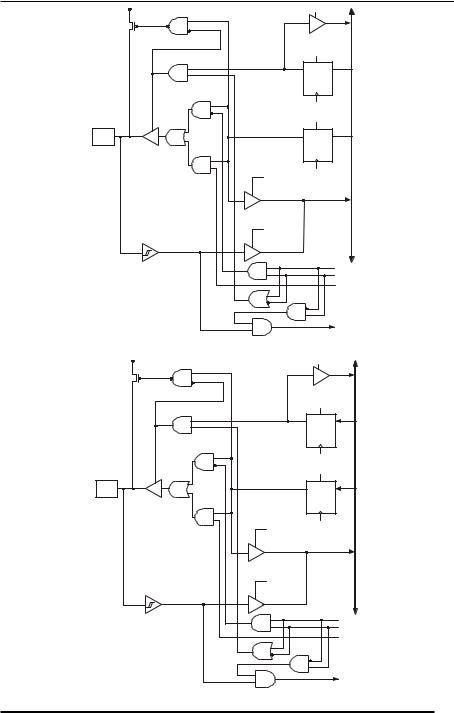

Рис. 51 Схема организации вывода порта B (вывод PB2)

135

ATMEL |

ÊÒÖ-ÌÊ |

|

RD |

Нагрузочный MOS резистор

Сброс

Вывод

PÂ3

Q R D

DDB3

C

WD

Сброс

Q R D

PORTB3

C

WP

RL

RP

Шина данных

WP: |

Запись PORTB |

WD: |

Запись DDRB |

RL: |

Чтение фиксатора PORTB |

RP: |

Чтение состояния вывода PORTB |

RD: |

Чтение DDRB |

MSTR: Разрешение ведущего режима SPI |

|

SPE: |

Разрешение SPI |

MSTR

SPE

Вход SPI в ведомом режиме

Выход SPI в ведущем режиме

|

Рис. 52 Схема организации вывода порта B (вывод PB3) |

|

|||

|

Нагрузочный |

|

RD |

|

|

|

|

|

|

|

|

|

MOS |

|

|

|

|

|

резистор |

|

|

|

|

|

|

Сброс |

|

||

|

|

Q |

R |

D |

|

|

|

DDB4 |

|

|

|

|

|

|

C |

|

|

|

|

|

WD |

|

данных |

|

Вывод |

Q |

R |

D |

|

|

|

Сброс |

|

||

|

PÂ4 |

PORTB4 |

Øèíà |

||

|

|

||||

|

|

|

C |

|

|

|

|

RL |

WP |

|

|

|

|

|

|

|

|

|

|

RP |

|

|

|

WP: |

Запись PORTB |

|

|

COM01 |

|

WD: |

Запись DDRB |

|

|

COM01 |

|

RL: |

Чтение фиксатора PORTB |

Выбор режима |

|

Совпадение |

|

RP: |

Чтение состояния вывода PORTB |

выхода |

|

при сравнении 0 |

|

|

|

|

|

||

RD: |

Чтение DDRB |

|

|

|

|

|

Рис. 53 Схема организации вывода порта B (вывод PB4) |

|

|||

136