AVR / at-avr

.pdf

ÊÒÖ-ÌÊ

4 тактовых цикла. В течение этих 4 циклов состояние счетчика команд (2 байта) извлекается из стека и указатель стека инкрементируется на 2. Когда AVR выходит из прерывания, он всегда возвращается в основную программу и выполняет еще одну команду, прежде, чем начать обслуживание какого либо отло женного прерывания.

Отметим, что регистр статуса SREG не обрабатывается аппаратн ыми средствами AVR, ни для прерываний, ни для подпрограмм.

При обработке подпрограмм прерываний, требующих сохране ния в SREG, запись должна выполняться программными средствами пользовател я. Для прерываний, запускаемых статическими событиями (например совпадени е содержимого регистра сравнения 1A с состоянием таймера/счетчика1) флаг прерывани я устанавливается в момент наступления события. Если флаг очищен, но условия в озникновения прерывания продолжают существовать, флаг не будет устанавливаться до тех пор, пока это событие не наступит вновь.

Режимы энергосбережения (Sleep Modes)

Для перевода в любой из трех режимов энергосбережения бит SE в регистре MCUCR должен быть установлен в состояние1. Биты SM1 и SM0 регистра MCUCR определяют какой из режимов Idle, Power Down или Power Save будет запущен ком андой SLEEP.

При возникновении разрешенного прерывания во время нахо ждения MCU в режиме энергосбережения, MCU активируется, выполняет подпр ограмму обработки прерывания и продолжает работу до следующей команды SLEEP. Ес ли во время режима энергосбережения происходит сброс, MCU активируется и начи нает работу по вектору сброса. Содержимое регистрового файла, SRAM и памяти I/O в проце ссе активации не изменяется. В Таблице 4 представлен выбор режима энерго сбережения.

Отметим, что если для возврата из режима энергосбережения Power Down или Power Save, используется запуск прерывания по уровню, то низкий уровень должен удерживаться несколько дольше, чем время задержки сброса t TOUT, иначе микроконтроллер не активируется.

РЕЖИМ Idle

Если биты SM1/SM0 находятся в состоянии 00 команда SLEEP переводит MCU в режим Idle, останавливая CPU но оставляя активными таймеры/сч етчики, сторожевой таймер и систему прерываний. Это обеспечивает активацию M CU внешними прерываниями и такими внутренними прерываниями, как пере полнение таймера и завершение приема UART. Если активация по аналоговому компар атору не требуется, то аналоговый компаратор может быть отключен установкой бита ACD в регистре управления и статуса аналогового компаратора ACSR. Это позво лит дополнительно снизить потребление в Idle режиме. При активации MCU из Idle режима CPU начинает выполнять программу незамедлительно.

РЕЖИМ Power Down

При установке битов SM1/SM0 в состояние 10 команда SLEEP переводит MCU в режим Power Down. В этом режиме останавливается внешний генерат ор. Пользователь может разрешить работу сторожевого таймер а. Если сторожевой таймер разрешен, то активация MCU произойдет по завершении установ ленного в сторожевом таймере периода времени. Если внешний источник тактового сигнала подключен к выводу XTAL1, то активация MCU из режима Power Down может происходить бе з

8 7

ATMEL |

ÊÒÖ-ÌÊ |

задержки, обычно необходимой для стабилизации XTAL генерато ра. Режим такой активации разрешается программированием перемычек SUT0/SUT1 в Flash памяти. См. раздел Режим параллельного программирования.

РЕЖИМ Power Save

При установке битов SM1/SM0 в состояние 11 команда SLEEP переводит MCU в режим Power Save. Этот режим, за одним исключением, аналогичен ре жиму Power Down. Если таймер/счетчик0 тактируется асинхронно, т.е. бит AS0 в р егистре ASSR установлен, таймер/счетчик0 будет работать в режиме Power Save.

MCU будет активироваться прерываниями по переполнению или совпадению выхода таймера/счетчика0.

Таймеры/счетчики

Микроконтроллеры ATmega603/103 оснащены тремя таймерами/счетчика ми общего назначения - двумя 8-разрядными и одним 16-разрядным. Т аймер/счетчик0, в дополнение к обычному режиму, может тактироваться асинхр онно от внешнего генератора. Этот генератор оптимизирован под использова ние кварцевого кристалла на частоту 32768 кГц, что позволяет использовать таймер/счетч ик0 как часы реального времени (Real Time Clock - RTC).

Таймер/счетчик0 оснащен своим собственным предварительн ым делителем. Таймеры/счетчики 1 и 2 используют выходы ступеней деления о бщего 10-разрядного предварительного делителя. Эти два таймера/счетчика можн о использовать как таймеры с встроенной временной базой или как счетчики, переключае мые по состоянию на внешнем выводе.

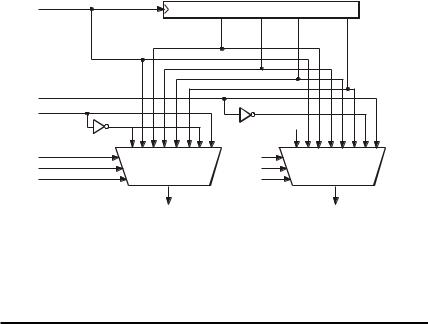

Предварительные делители таймеров/счетчиков |

||||

CK |

10-разрядный предварительный делитель |

|||

|

CK/8 |

CK/64 |

CK/256 |

CK/1024 |

EXT1 |

|

|

|

|

EXT2 |

|

|

|

|

|

0 |

|

0 |

|

|

|

|

|

|

CS20 |

|

CS10 |

|

|

CS21 |

|

CS11 |

|

|

CS22 |

|

CS12 |

|

|

|

Тактовый сигнал таймера/счетчика2 |

Тактовый сигнал таймера/счетчика1 |

||

Рис. 30 Предварительный делитель таймера/счетчика1 и таймера/счетчика2 |

||||

Предварительный делитель таймеров/счетчиков 1и 2 содержит четыре ступени |

||||

деления: CK/8, CK/64, CK/256 и CK/1024, где CK входной тактовый сигнал. Кроме тог о, |

||||

в качестве источников тактовых сигналов могут быть испол ьзованы сигналы от внешних |

||||

источников, тактовый сигнал CK и нулевой тактовый сигнал (stop ). |

|

|||

8 8

ÊÒÖ-ÌÊ

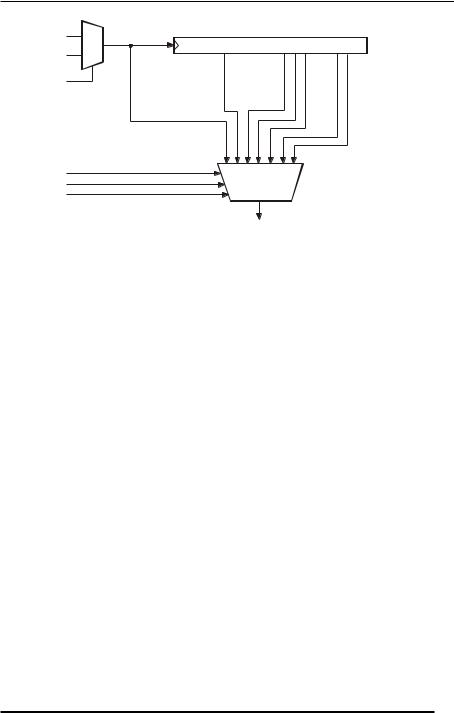

CK |

TCK0 |

10-разрядный предварительный делитель |

||

|

|

|||

TCK1 |

|

TCK0/8 |

TCK0/32 TCK0/64 TCK0/128 |

TCK0/256 TCK0/1024 |

AS0 |

|

|||

|

|

|

|

|

CS00

CS01

CS02

Тактовый сигнал таймера/счетчика 0

Рис. 31 Предварительный делитель таймера/счетчика0

Тактовый сигнал таймера/счетчика0 обозначен TCK0. Этот такто вый сигнал по умолчанию подключен к основному тактовому сигналу систе мы CK. При установке бита AS0 в регистре ASSR таймер/счетчик0 будет асинхронно такти роваться сигналом с вывода TOSC1, что позволяет использовать таймер/счетчик0 в ка честве часов реального времени (RTC). Генератор оптимизирован под использование кв арцевого кристалла с частотой 32768 кГц, подсоединяемого между выводами TOSC1 и TOSC2.

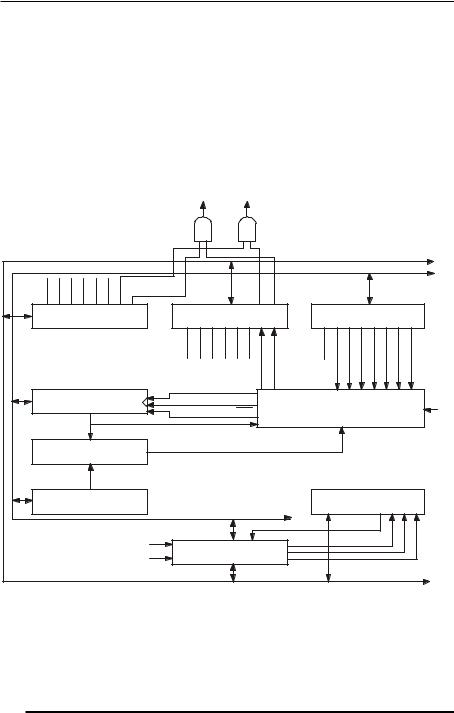

8-разрядные таймеры/счетчики T/C0 и T/C2

8-разрядный таймер/счетчик0 получает тактовый сигнал или н епосредственно от TCK0 или после прохождения его через предварительный дели тель.

8-разрядный таймер/счетчик2 получает тактовый сигнал непо средственно от CK, после прохождения его через предварительный делитель и ли от внешнего вывода. Оба таймера/счетчика могут быть остановлены, как это пока зано в описании регистров управления таймерами/счетчиками TCCR0 и TCCR2.

В регистре флагов прерывания таймеров/счетчиков TIFR хранят ся различные флаги состояния регистров (переполнения, совпадения при сравнении и захвата события). Установки управляющих сигналов хранятся в регистрах упр авления таймерами/ счетчиками TCCR0 и TCCR2. Установка разрешения/запрещения прерыв аний производится в регистре масок прерываний таймеров/счетч иков TIMSK.

При тактировании таймера/счетчика2 внешним тактовым сигн алом этот сигнал синхронизируется с тактовой частотой CPU. Для обеспечения п равильной синхронизации внешнего сигнала необходимо, чтобы минимальное время меж ду двумя входящими тактовыми циклами было не менее одного цикла внутреннего тактового сигнала CPU. Внешний тактовый сигнал синхронизируется нарастающим ф ронтом внутреннего тактового сигнала CPU.

Точность и разрешение 8-разрядных таймеров/счетчиков раст ет с уменьшением коэффициента предварительного деления. Аналогичным обр азом высокий коэффициент предварительного деления удобно использовать при реали зации функций с низким быстродействием или точной синхронизации редко происхо дящих действий.

8 9

ATMEL |

|

|

|

|

|

ÊÒÖ-ÌÊ |

Оба таймера/счетчика поддерживают две функции сравнения выхода, используя регистры |

||||||

сравнения выхода OCR0 и OCR2 как источники данных, сравниваемых с содержимым |

||||||

таймеров/счетчиков. В функции сравнения выхода входит и о пция очистки счетчика |

||||||

при совпадении и формирование, при совпадении, сигнала на выводах сравнения выхода |

||||||

- PB4(OC0/PWM0) è PB7(OC2/PWM2). |

|

|

|

|

||

Таймеры/счетчики 0 и 2 можно использовать как 8-разрядные ши ротно- |

||||||

импульсные модуляторы (PWM). В этом режиме таймер/счетчик, со вместно с регистром |

||||||

совпадения выхода работают как автономный ШИМ с центрированными импульсами |

||||||

и без ложных выбросов. Подробнее эта функция описана в раз делеТаймеры/счетчики |

||||||

0 и 2 в ШИМ режиме. |

|

|

|

|

|

|

|

Прерывание по |

Прерывание по |

|

|

||

переполнению T/C0 |

совпадению T/C0 |

|

|

|||

8-разрядная шина данных |

|

|

|

|

|

|

8-разрядная асинхронная шина данных |

|

|

|

таймера/счетчика 0 |

|

|

OCIE2 TOIE2 TICIE1 OCIE1B OCIE1A TOIE1 OCIE0 TOIE0 |

|

|

OCF0 |

TOV0 |

|

|

Регистр масок прерываний |

Регистр флагов |

|

Регистр управления |

|||

ïî T/C0 (TIMSK) |

прерываний по T/C0 (TIFR) |

T/C0 (TÑCR0) |

|

|||

|

OCF2 |

TOV2 ICF1 OCF2B |

OCF2A TOV1 OCF0 |

TOV0 |

PWM0 COM01 COM00 CTC0 CS02 CS01 |

CS00 |

7 |

0 |

Очистка T/C |

|

|

|

|

|

|

|

|

|

||

Таймер/счетчик0 (TCNT0) |

|

Тактовый сигнал T/C |

ЛОГИКА УПРАВЛЕНИЯ |

TCK0 |

||

|

Направл. счета (Up/Down) |

|||||

|

|

|

||||

7 |

0 |

|

|

|

|

|

8-разрядный компаратор |

|

|

|

|

|

|

7 |

0 |

|

|

|

|

|

Регистр сравнения |

|

|

|

|

Регистр асинхронного |

|

выхода (OCR0) |

|

|

|

|

состояния (ASSR) |

|

CK |

Блок синхронизации |

AS0 TC0UB OCR0UB |

ICR0UB |

|||

|

|

|||||

TCK0 |

|

|

||||

|

|

|

|

|

||

Рис. 32 Блок-схема таймера/счетчика0 |

|

|

|

|||

9 0 |

|

|

|

|

|

|

ÊÒÖ-ÌÊ |

|

|

|

|

|

|

|

|

|

|

|

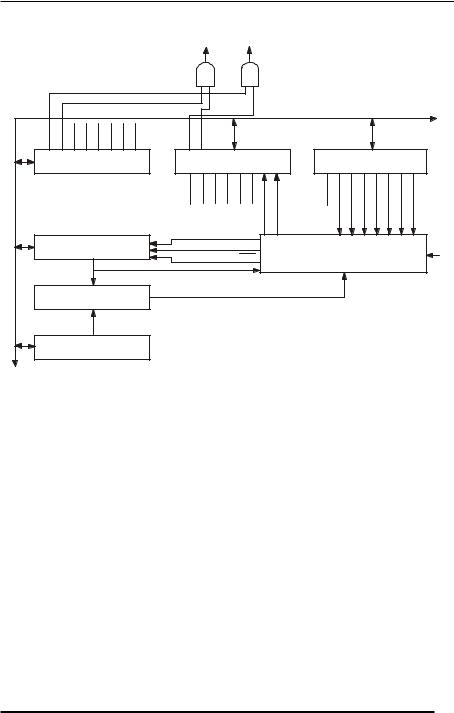

Прерывание по |

Прерывание по |

|

|

||||

|

переполнению T/C2 |

совпадению T/C2 |

|

|

|||||

данных |

OCIE2 TOIE2 TICIE1 OCIE1B OCIE1A TOIE1 OCIE0 TOIE0 |

OCF2 |

TOV2 |

|

|

|

Регистр управления |

||

-разрядная шина |

Регистр масок прерываний |

Регистр флагов |

|

||||||

ïî T/C0 (TIMSK) |

прерываний по T/C0 (TIFR) |

|

T/C2 (TOCR2) |

|

|||||

|

|

TOV2 ICF1 |

OCF2B |

OCF2A TOV1 OCF0 |

|

PWM2 |

COM21 COM20 CTC2 CS22 CS21 |

CS20 |

|

7 |

0 |

Очистка T/C |

|

||||||

|

OCF2 |

TOV0 |

|||||||

8 |

Таймер/счетчик2 (TCNT2) |

|

Тактовый сигнал T/C |

|

ЛОГИКА УПРАВЛЕНИЯ |

|

|||

|

|

|

CK |

||||||

|

|

Направл. счета (Up/Down) |

|

||||||

|

7 |

0 |

|

|

|

|

|

|

|

|

8-разрядный компаратор |

|

|

|

|

|

|

|

|

|

7 |

0 |

|

|

|

|

|

|

|

|

Регистр сравнения |

|

|

|

|

|

|

|

|

|

выхода (OCR2) |

|

|

|

|

|

|

|

|

|

Рис. 33 Блок-схема таймера/счетчика2 |

|

|

|

|

||||

|

РЕГИСТР УПРАВЛЕНИЯ ТАЙМЕРОМ/СЧЕТЧИКОМ0 - |

|

|

||||||

|

TCCR0 - (The Timer/Counter0 Control Register) |

|

|

|

|||||

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

$33 ($53) |

- |

PWM0 |

COM01 |

COM00 |

CTC0 |

CS02 |

CS01 |

|

CS00 |

TCCR0 |

|

Чтение/Запись |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

R/W |

|

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

РЕГИСТР УПРАВЛЕНИЯ ТАЙМЕРОМ/СЧЕТЧИКОМ2 - |

|

|

|

|

|

||||||

TCCR2 - (The Timer/Counter2 Control Register) |

|

|

|

|

|

|

|||||

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

$25 ($45) |

- |

PWM2 |

COM21 |

COM20 |

CTC2 |

CS22 |

CS21 |

|

CS20 |

|

TCCR2 |

Чтение/Запись |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

R/W |

|

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

9 1

ATMEL ÊÒÖ-ÌÊ

• Bit 7 - Res: Reserved Bit - Зарезервированный бит

Данный бит в микроконтроллерах ATmega603/103 зарезервирован и при считывании всегда покажет состояние 0.

•Bit 6 - PWM0 / PWM2: Pulse Width Modulator Enable - Разрешение широтно-

импульсного модулятора

Установленный в состояние 1 бит разрешает режим ШИМ для та ймеров/счетчиков 0 или 2. Режим подробно описан в разделе Таймеры/счетчики 0 и 2 в ШИМ режиме.

•Bits 5,4 - COM01, COM00 / COM21, COM20: Compare Output Mode, bits 1 and 0 -

Режим сравнения выхода, биты 1 и 0

Управляющие биты COMn1 и COMn0 устанавливают состояние выходных выводов PB4(OC0/PWM0) или PB7(OC2/PWM2). после совпадения в таймере/счетчике 2. Поскольку это альтернативная функция выводов порта I/O, то с оответствующий бит направления вывода должен быть установлен в состояние 1. У правляющая конфигурация показана в таблице 10.

Таблица 10. Выбор режима сравнения

COMn1 |

COMn0 |

Описание |

0 |

0 |

Таймер/счетчикn отсоединен от выходного вывода OCn/PWMn |

0 |

1 |

Переключение выходной линии OCn/PWMn. |

1 |

0 |

Очистка выходной линии OCn/PWMn (установка в состояние 0). |

1 |

1 |

Установка выходной линии OCn/PWMn (установка в состояние 1). |

Примечания: n = 0 или 2.

В ШИМ режиме функции этих битов отличаются. Подробное опи сание приведено в таблице 13. При изменении битов COMn1/COMn0 прерывание по сравнени ю выхода должно быть запрещено очисткой его бита разрешени я прерывания в регистре TIMSK. В противном случае при изменении состояния бита может п роизойти прерывание.

•Bit 3 - CTC0 / CTC2: Clear Timer/Counter on Compare match - Очистить таймер/ счетчик при совпадении

При установленном в состояние 1 бите CTC0 или CTC2 таймер/счетчик сбрасывается в состояние $00 в течение одного тактового цикла CPU после наст упления совпадения. Если бит управления сброшен, то таймер продолжает считать и не используется в процедуре сравнения. Поскольку факт совпадение детектир уется в тактовом цикле CPU следующем за совпадением, то эта функция будет вести себ я несколько по другому, если коэффициент предварительного деления будет больше 1. Если используется коэффициент предварительного деления равный 1 и в регистр сравнения A установлено содержимое C, то таймер будет продолжать счет так как это де лается при установленном CTC0/2.

... | C-1 | C | C+1 | 0 | 1 | ...

Если установлен коэффициент деления 8, таймер будет счита ть аналогично следующей последовательности:

... | C-1, C-1, C-1, C-1, C-1, C-1, C-1, C-1 | C, C, C, C, C, C, C, C | C+1, 0, 0, 0, 0, 0, 0, 0, 0 | 1, 1, 1,

...

В ШИМ режиме состояние этого бита значения не имеет.

•Bits 2,1,0 - CS02, CS01, CS00 / CS22, CS21, CS20: Clock Select bits 2,1 and 0 - Áèòû

выбора тактовой частоты

Биты 2,1 и 0 выбора тактовой частоты таймера/счетчика2 подклю чают выход определенной ступени предварительного делителя.

9 2

ÊÒÖ-ÌÊ

Таблица 11. Выбор коэффициента деления предварительного делителя таймера/счетчика0

CS02 |

CS01 |

CS00 |

Описание |

0 |

0 |

0 |

Таймер/счетчик0 остановлен. |

0 |

0 |

1 |

TCK0 |

0 |

1 |

0 |

TCK0 / 8 |

|

|

|

|

0 |

1 |

1 |

TCK0 / 32 |

1 |

0 |

0 |

TCK0 / 64 |

1 |

0 |

1 |

TCK0 / 128 |

1 |

1 |

0 |

TCK0 / 256 |

1 |

1 |

1 |

TCK0 / 1024 |

Таблица 12. Выбор коэффициента деления предварительного делителя таймера/счетчика2

CS22 |

CS21 |

CS20 |

Описание |

|

|

|

|

0 |

0 |

0 |

Таймер/счетчик0 остановлен. |

|

|

|

|

0 |

0 |

1 |

CK |

0 |

1 |

0 |

CK / 8 |

0 |

1 |

1 |

CK / 6 4 |

1 |

0 |

0 |

CK / 256 |

1 |

0 |

1 |

CK / 1024 |

1 |

1 |

0 |

Внешний вывод PD7(T2), падающий фронт |

1 |

1 |

1 |

Внешний вывод PD7(T2), нарастающий фронт |

|

|

|

|

Условие Stop обеспечивает реализацию функции разрешения/за прещения таймера.

Режим деления CK реализуется непосредственным делением та ктовой частоты CK. Если для тактирования таймера/счетчика 2 используется вн ешний источник, то переключения на выводе PD7/(T2) будут воздействовать на счетч ик, даже если этот вывод сконфигурирован как выход.

ТАЙМЕР/СЧЕТЧИК0 - TCNT0 - (Timer/Counter0)

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

||||

$32 ($42) |

MSB |

|

|

|

|

|

|

|

|

|

|

LSB |

TCNT0 |

Чтение/Запись |

R/W |

|

R/W |

R/W |

R/W |

|

R/W |

|

R/W |

|

R/W |

R/W |

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

||||

ТАЙМЕР/СЧЕТЧИК2 - TCNT2 - (Timer/Counter2) |

|

|

|

|

|

|

|||||||

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

||||

$24 ($44) |

MSB |

|

|

|

|

|

|

|

|

|

|

LSB |

TCNT2 |

Чтение/Запись |

R/W |

|

R/W |

R/W |

R/W |

|

R/W |

|

R/W |

|

R/W |

R/W |

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

||||

Содержимое этих 8-разрядных регистров является состояние м таймеров/ счетчиков. Оба таймера/счетчика реализованы как счетчики по нарастанию или реверсивные (в ШИМ режиме) счетчики с возможностью чтения /записи. Если в таймер/ счетчик записано некоторое значение и выбран источник та ктового сигнала, то он продолжит счет с записанного значения с тактовой частото й счетчика.

9 3

ATMEL |

|

|

|

|

|

|

|

|

|

ÊÒÖ-ÌÊ |

РЕГИСТР САВНЕНИЯ ВЫХОДА ТАЙМЕРА/СЧЕТЧИКА0 - |

|

|

||||||||

OCR0 - (Timer/Counter0 Output Compare Register) |

|

|

|

|||||||

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

|

1 |

0 |

|

$31 ($51) |

MSB |

|

|

|

|

|

|

|

LSB |

OCR0 |

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

|

РЕГИСТР СРАВНЕНИЯ ВЫХОДА ТАЙМЕРА/СЧЕТЧИКА2 - |

|

|

|

|||||||

OCR2 - (Timer/Counter2 Output Compare Register) |

|

|

|

|||||||

Áèòû |

7 |

6 |

5 |

4 |

3 |

2 |

|

1 |

0 |

|

$23 ($43) |

MSB |

|

|

|

|

|

|

|

LSB |

OCR2 |

Чтение/Запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

|

Начальное состояние |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

|

Регистры сравнения выходов являются 8-разрядными регистр ами с возможностью чтения/записи. Выполнение процедуры сравнения определяе тся регистрами TCCR0 и TCCR2. Совпадение при сравнении произойдет только тогда, когд а таймер/счетчик досчитает до значения содержимого OCR. Программная запись о дного и того же значения в таймер/счетчик и в регистр сравнения выхода не приведет к формированию совпадения при сравнении.

Совпадение при сравнении приведет к установке флага прер ывания по совпадению в течение тактового цикла CPU следующего за совп адением. Необходимо принимать меры предосторожности при работе таймера/счет чика0 в асинхронном режиме, т.е. устанавливать в состояние 1 бит AC0 в регистре ASSR. Пр и записи в регистр OCR0 значение, пересылается в регистр по TCK0 такту, след ующему за операцией записи.

ТАЙМЕРЫ/СЧЕТЧИКИ 0 и 2 в ШИМ РЕЖИМЕ -

Timer/Counter 0 and 2 in PWM mode

При установленном ШИМ режиме таймер/счетчик и регистр сра внения выхода (OCR0 или OCR2) формируют 8-разрядный, без ложных выбросов и с прав ильной фазой ШИМ сигнал с выходом через PB4(OC0/PWM0) или PB7(OC2/PWM2) выводы. Таймер/ счетчик работает как реверсивный счетчик, считающий от $00 д о $FF, после чего он считает в обратную сторону до нуля и только после этого на чинает новый цикл. Когда состояние счетчика совпадает с содержимым регистра срав нения выхода выводы PB4(OC0/PWM0) или PB7(OC2/PWM2) устанавливаются или очищаются, в соответств ии с установленными, в регистрах управления таймерами/счетч иками TCCR0 и TCCR2, битами COM01/COM00 или COM21/COM20. См. таблицу 13.

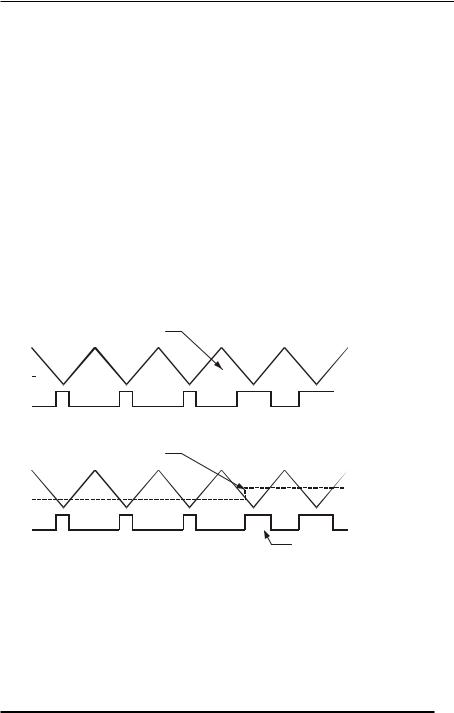

ÂШИМ режиме при записи содержимое регистра сравнения вых ода пересылается на временное хранение. Содержимое фиксируе тся при достижении таймером/счетчиком состояния $FF. Такой прием предохраняет от появления ШИМ импульсов увеличенной ширины (ложных выбросов) в случае н есинхронной записи OCR0 или OCR2. Пример см. на рис.34.

Âпромежуток времени между операциями записи и фиксации с читывание из OCR0 или OCR2 приведет к считыванию из места временного хранени я. Это означает, что чаще всего при чтении значения уставки считывание буд ет производиться из OCR0/

2.При состоянии регистра OCR $00 или $FF выход ШИМ будет удерживат ься

9 4

ÊÒÖ-ÌÊ

Таблица 13. Выбор режима сравнения в ШИМ режиме

COMn1 |

COMn0 |

Эффект, оказываемый на вывод Compare/PWM |

|

|

|

0 |

0 |

Не подсоединен |

0 |

1 |

Не подсоединен |

1 |

0 |

Очистка при совпадении, счет по нарастанию. Установка при совпадении, |

|

|

счет по убыванию (неинвертирующий ШИМ). |

1 |

1 |

Очистка при совпадении, счет по убыванию. Установка при совпадении, счет |

|

|

по нарастанию (инвертирующий ШИМ). |

Примечания: n = 0 или 2

íà низком или высоком уровне, в зависимости от установок COM21/COM20 или COM11/COM10. См. таблицу 14.

В ШИМ режиме флаг переполнения таймера (TOV0 или TOV2) устанавли вается при смене направления счета при $00. Прерывания по переполне нию таймеров 0 и 2 работают так же, как и в нормальном режиме таймеров/счетчи ков, т.е. они срабатывают когда TOV0 или TOV2 установлены, и разрешены прерывания по переп олнению таймера

èглобальному прерыванию. Это относится также к флагам ср авнения выхода таймеров

èпрерываниям.

Частота ШИМ будет соответствовать тактовой частоте тайм ера деленной на

510.

Изменение уставки сравнения

Текущее состояние таймера/счетчика

Установленное

Установленное

значение сравнения

значение сравнения

Выход ШИМ

Выход ШИМ

Синхронизированная фиксация уставки в OCR

Изменение уставки сравнения

|

|

|

|

|

|

|

|

Текущее состояние |

|

|

|

|

|

|

|

таймера/счетчика |

|

|

|

|

|

|

|

|

Установленное |

|

|

|

|

|

|

|

|

|

значение сравнения |

|

|

|

|

|

|

|

Выход ШИМ |

|

|

|

|

|

|

|

|

||

|

|

Несинхронная фиксация уставки в OCR |

Ложный выброс |

|||||

|

|

|

|

|||||

|

Рис. 34 Эффект несинхронной фиксации OCR |

|

|

|||||

|

Таблица 14. Состояния ШИМ выходов при OCRn = $00 или $FF |

|||||||

|

|

|

|

|

|

|

|

|

COMn1 |

|

COMn0 |

OCRn |

Выход PWMn |

|

|

||

1 |

|

0 |

$00 |

L - низкий уровень |

|

|

||

1 |

|

0 |

$FF |

H - высокий уровень |

|

|

||

1 |

|

1 |

$00 |

H - высокий уровень |

|

|

||

|

|

|

|

|

|

|

|

|

1 |

|

1 |

$FF |

L - низкий уровень |

|

|

||

Примечания: n = 0 или 2

9 5

ATMEL |

ÊÒÖ-ÌÊ |

АСИНХРОННАЯ РАБОТА ТАЙМЕРА/СЧЕТЧИКА0

При синхронной работе таймера/счетчика0 все операции и та ктирование идентичны работе таймера/счетчика2. Однако асинхронная ра бота имеет некоторые особенности.

• Это важно! При переключении между асинхронным и синхронны м тактированием таймера/счетчика0 регистры таймера TCNT0, OCR0 и TCCR0 могут быть повреждены. Безопасное переключение выполняется сл едующей последовательностью действий:

1.Запрещаются прерывания OCIE0 и TOIE0 таймера0.

2.Соответствующей установкой ASO выбирается источник тактового сигнала.

3.В TCNT0, OCR0 и TCCR0 записываются новые значения.

4.Если выполняется переключение в асинхронный режим: ожидать TCN0UB, OCR0UB и TCR0UB.

5.Разрешить прерывания, если это необходимо.

•Генератор оптимизирован под использование часового кристалла с частотой 32,768 кГц. Внешний тактовый сигнал, подаваемый на этот вывод, п роходит через тот же самый усилитель с полосой пропускания 256 кГц. Таким образом , внешний тактовый сигнал должен быть в диапазоне от 0 Гц до 256 кГц. Частота внешнего тактового сигнала, подаваемого на вывод TOSC1, не должна превышать одной четвертой от тактовой частоты CPU. Отметим, что тактовая частота CPU может б ыть ниже частоты XTAL, если разрешено деление частоты XTAL.

•При записи в один из регистров TCNT0, OCR0 или TCCR0 записываемая величина пересылается в регистр временного хранения и фи ксируется после двух положительных фронтов TOSC1. Пользователь не должен записыва ть новое значение прежде, чем содержимое регистра временного хранения не бу дет передано по назначению. Каждый из указанных регистров имеет свой собс твенный регистр временного хранения, это означает, к примеру, что запись в T CNT0 не исказится при записи в OCR0. Для того, чтобы убедиться в выполнении пересылк и в регистр назначения используется регистр статуса асинхронного режима (Asynchronous Statu s Register - ASSR).

•При вводе режима Sleep после записи в регистры TCNT0, OCR0 or TCCR0 пользователь должен ожидать пока записываемый регистр н е будет обновлен, если таймер/счетчик0 используется для активации прибора. В ино м случае MCU перейдет

âрежим Sleep прежде, чем изменения окажут какой либо эффект. Э то особенно важно если для активации прибора используется прерывание по ср авнению выхода0; сравнение выхода запрещается во время записи в OCR0 или TCNT0. Если цикл зап иси не завершен (т.е. пользователь введет режим Sleep прежде, чем бит OCR0UB будет сб рошен в 0) прибор никогда не получит совпадения при сравнении и MCU не будет активирован. Если таймер/счетчик0 используется для активации прибора и з режима Power Save и если пользователь намеревается возобновить режим Power Save, то необходимо предпринимать меры предосторожности - для сброса логики п рерывания необходим один цикл TOSC1. Если время между активацией и восстановление м режима Power Save меньше одного цикла TOSC1 прерывание не произойдет и прибор не будет активирован. Если пользователь сомневается в том, что про межуток времени перед восстановлением режима Power Save достаточен, необходимо исполь зовать следующий алгоритм:

1.Записать значение в TCCR0, TCNT0 или OCR0.

2.Подождать пока соответствующий флаг занятого обновления в регистре

9 6