- •2.3. Устройства ввода вывода

- •ГЛАВА 3. АРИФМЕТИЧЕСКИЕ ОСНОВЫ ЭВМ

- •3.1 Системы счисления и понятие кода

- •3.2. Арифметические основы ЭВМ

- •3.2.1 Форма представление чисел с фиксированной запятой

- •ГЛАВА 4. ЛОГИЧЕСКИЕ ОСНОВЫ ЭВМ

- •4.1. Логические основы построения и работы компьютеров

- •4.2. Электронные технологии логических элементов ЭВМ

- •ГЛАВА 5. ПРОГРАММНАЯ МОДЕЛЬ МИКРОПРОЦЕССОРА

- •ГЛАВА 6. СТРУКТУРА ПРОЦЕССОРОВ IA-32

- •ГЛАВА 7. АРХИТЕКТУРА ПРОЦЕССОРОВ AMD

ГЛАВА 6. СТРУКТУРА ПРОЦЕССОРОВ IA-32

Главным устройством любой ЭВМ является центральный процессор. Ранее (см. главу 5) было отмечено, что каждый процессор характеризуется набором команд, которые он в состоянии выполнить. Например, процессор Pentium фирмы Intel не может обработать программы (и соответственно команды), написанные для процессора SPARC фирмы Sun, а SPARC не может выполнить программы, написанные для Pentium.

Укрупненную структурную схему типичного процессора можно представить в виде трех основных блоков: управляющего блока УБ, операционного блока (ОБ) и интерфейсного блока (ИБ). Управляющий блок выполняет функции выборки, декодирования и вычисления адресов операндов, а так же генерирует последовательности микрокоманд, реализующих команды процессора. Он содержит устройство управления, прерывания, синхронизации. Операционный блок служит для обработки данных. Он объединяет арифметико-логическое устройство АЛУ, регистры общего назначения (РОН) и специальные регистры. АЛУ выполняет арифметические (сложение, вычитание и т.п.) и логические (логическое И, ИЛИ и т.п.) операции. Регистры являются своего рода памятью ОБ, предназначенной для хранения промежуточных результатов и некоторых команд управления, информацию о состоянии процессора. Информация из них считываются и записываются очень быстро, поскольку они находятся внутри процессора. Регистров может быть от несколько десятков до нескольких сотен штук в зависимости от типа процессора. Большим количеством регистров характеризуются RISC - процессоры, а небольшим – CISC - процессоры. ИБ позволяет подключить память и периферийные устройства к процессору, а также, выполняет функции канала прямого доступа к памяти. Интерфейс процессора содержит информационные шины данных (ШД), адресов (ША) и управления (ШУ). Надо заметить, что такое распределение аппаратных блоков процессора между функциональными частями весьма условно и приводится для примера.

Процессор выполняет каждую команду за несколько шагов:

вызывает следующую команду из памяти и переносит ее в регистр команд;

меняет положение счетчика команд, который теперь должен указывать на следующую команду;

определяет тип вызванной команды;

если команда использует данные из памяти, определяет место нахождение

данных;

переносит данные в регистр процессора;

выполняет команду;

переходит к 1 шагу, что бы начать выполнение следующей команды.

Эта последовательность шагов (выборка – декодирование – исполнение) является основой работы для всех процессоров.

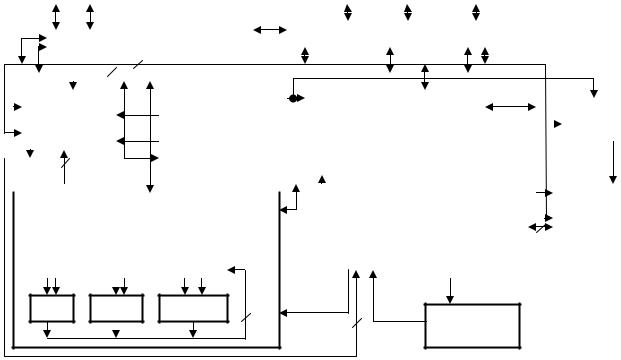

Упрощенная структурная схема типичного процессора изображена на следующем рисунке.

Базовую структуру процессоров (П) IA-32 можно рассмотреть на примере Intel-386 (рис. 6.1). В структуре Intel-386 можно выделить шесть основных блоков, работающих параллельно: блок интерфейса с магистралью, блок предварительной выборки команд, блок декодирования команд, исполнительный блок, блок управления сегментами и блок страничной трансляции.

Блок интерфейса с магистралью содержит драйвер адреса, схемы управления размером адреса и конвейером, мультиплексор, приемопередатчики и др. Этот блок обеспечивает интерфейс между процессором и его окружением. Он принимает внутренние запросы для выборки команд от блока предварительной выборки команд и для обмена данными с исполнительным блоком и устанавливает приоритет этих запросов. Одновременно он генерирует или обрабатывает сигналы для исполнения текущего цикла магистрали. К ним относятся сигналы адреса, данных и управления для обращения к внешней памяти и устройствам ввода-вывода. При помощи схемы арбитра запросов блок управляет интерфейсом с внешними задатчиками магистрали и сопроцессорами.

86

Для того чтобы заранее получать команды или данные перед их фактическим использованием, существует функция опережающего просмотра программы, которую в Intel386 выполняет блок предвыборки команд. Когда блок интерфейса с магистралью не занимает цикла магистрали для исполнения команды, блок предвыборки команд использует его для последовательной выборки из памяти байтов команд. Эти команды хранятся в 16-байтовой очереди команд в ожидании обработки блоком декодирования команд.

В процессоре Intel-486 (рис. 6.2) этот блок был дополнен схемой управления паритетом (выравниванием) и схемой управления пакетами. На основе последней был реализован специальный режим работы магистрали – режим пакетирования. В этом режиме при передаче 4 слов на магистрали выставляется только адрес первого, что позволяет существенно сократить время обмена данными с оперативной памятью или внешним КЭШем.

Новая микроархитектура процессоров Pentium, см. рис. 6.3, и более поздних базируется на идее суперскалярной обработки. Под суперскалярностью подразумевается наличие более одного конвейера для обработки команд (в отличие от скалярной – одноконвейерной архитектуры).

Конвейеризация позволяет нескольким внутренним блокам МП работать одновременно, см. табл. 6.1, совмещая дешифрование команды, операции АЛУ, вычисление эффективного адреса и циклы шины нескольких команд. В состав МП 80286 входило 4 конвейерных устройства:

BU (Bus Unit) – шинный блок (считывание из памяти и портов ввода/вывода);

IU (Instruction Unit) – командный блок (дешифрация команд);

EU (Executive Unit) – исполнительный блок (выполнение команд);

AU (Address Unit) – адресный блок (вычисляет все адреса, формирует физический адрес).

87

Шина исполнительного адреса |

32 |

Блок сегментации |

Блок разбивки на страницы |

Управление шиной |

|||

|

|

|

Трехвходовый |

32 |

Сумматор |

|

Арбитр |

Шина исполнительного адреса32 |

сумматор |

|

|

|

|||

|

|

|

запросов |

||||

|

|

|

|

Шина |

|

|

|

|

|

|

Регистры |

Кэш |

|

|

|

|

Блок |

|

линейного |

|

|

||

|

|

дескрипторов |

адреса |

страниц |

|

|

|

АЛУ |

проверки |

|

|

|

|

Шинафизического адреса |

|

защиты |

|

ПЛМ границ и |

|

ПЛМ |

Драйвер |

||

|

|

|

|||||

|

|

|

атрибутов |

|

управления |

|

|

|

|

|

|

|

адреса |

||

|

|

|

|

|

и атрибутов |

|

|

Циклический |

|

|

|

|

|

|

|

|

|

|

|

|

|

Управления |

|

сдвигатель, |

|

|

|

Внутренняя |

шина |

|

|

|

|

|

|

Размером |

|||

сумматор |

|

|

Шина |

|

|

|

шины, |

Умножитель/ |

|

|

смещения |

|

|

|

конвейером |

|

|

|

|

|

|

|

|

Делитель |

Декодирование |

Декодер команд |

Устройство |

|

Мульти- |

||

Набор |

и упорядочение |

|

предварительной |

|

плексор, |

||

|

|

Предварительное |

выборки |

|

приемопере |

||

регистров |

Управляющее |

декодирование |

16-байтная |

|

датчики |

||

|

ПЗУ |

команд |

|

|

|||

|

|

|

|

|

очередь кодов |

|

32 |

|

Управление |

Очередь декодированных команд |

Предварительная выборка команд |

||||

Специализированная шина АЛУ

Рис. 6.1. Структурная схема процессора 80386

88

32 |

64 битная внутренняя шина |

|

Шина данных |

|

|||

|

|

|

|

|

|||

|

32 |

Шина линейного адреса |

|

|

|

|

|

|

|

|

|

|

|

Адрес |

|

Параллельный |

Устройство |

Устройство |

|

Кэш память |

32 |

Драйверы |

|

|

|

||||||

сдвигатель |

сегментации |

страничного |

|

(8 к) |

|

адреса |

|

База |

|

преобразования |

|

|

32 |

|

|

|

|

|

|

Буферы |

|

||

Регистры |

Регистры |

|

|

|

|

|

|

|

|

|

|

записи |

|

||

32 |

дескрипторов |

Ассоциативный |

|

|

|

|

|

|

|

|

32 |

|

|

||

|

|

буфер |

|

|

Приемо- |

Данные |

|

|

Контроль |

|

|

|

|||

|

|

|

|

|

передатчики |

||

АЛУ |

предела и |

|

|

|

|

|

|

|

|

|

|

данных |

|

||

|

атрибутов |

|

|

|

|

|

|

Микрокоманда |

Шина смещения |

|

|

|

Управление |

Управление |

|

32 |

|

128 |

|

|

|||

|

|

|

|

шиной |

|

||

|

|

|

|

|

|

|

|

Устройство с |

Устройство |

|

|

Устройство |

|

Управление |

|

плавающей |

управления |

|

|

предвыборки |

|

|

|

|

|

|

пакетами |

|

|||

точкой |

|

|

|

команд |

|

|

|

|

Дешифратор |

|

|

|

|

||

|

|

|

|

|

Управление |

|

|

|

|

команд |

|

|

|

|

|

|

|

|

|

Очередь кода |

|

размером |

|

|

|

|

|

|

|

|

|

|

Управляющее |

Дешифрованная |

24 |

(32 байта) |

|

Управление |

|

Регистры |

|

|

|

||||

|

|

|

|

||||

ПЗУ |

команда |

|

|

|

Кэш памятью |

|

|

|

|

Микрокоманды |

|

Управление |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

паритетом |

|

|

Рис. 6.2. Структурная схема процессора 80486 |

|

|

||||

89

Идея конвейеризации была развита в следующих моделях этого семейства. В МП Intel-486 реализован пятиступенчатый конвейер для обработки команд:

PF (Prefetch) – предвыборка команд;

D1 (Instruction Decode) – декодирование команды;

D2 (Address Generate) – формирование адреса;

EX (Execute) – выполнение команды в АЛУ и доступ к кэш-памяти;

WB (Write Back) – обратная запись.

Таблица 6.1

Конвейеризация команд в МП 80286

|

|

|

Циклы шины |

|

|

|

|

Выборка B |

N+1 |

N+2 |

|

|

|

|

команды U |

|

|

|

|

|

|

N-1 |

Дешифр. I |

N+1 |

N+2 |

|

|

Микрооперации |

|

команды U |

|

|

|

|

|

N-2 |

N-1 |

Формиров. адреса |

N+1 |

N+2 |

|

|

|

|

A |

|

|

|

|

|

|

операнда U |

|

|

|

|

|

|

|

|

|

|

|

|

N-2 |

N-1 |

Выборка B |

|

N+2 |

|

|

|

|

операнда U |

|

|

|

|

|

|

|

|

|

|

|

|

N-2 |

N-1 |

Выполне-ние E |

N+1 |

|

|

|

|

|

ко-манды U |

|

|

|

|

|

|

|

|

|

|

|

|

N-2 |

N-1 |

Запись В результата |

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

В МП Pentium команды распределяются по двум независимым исполнительным конвейерам (U и V). Конвейер U может выполнять любые команды семейства IA-32, включая целочисленные команды и команды с плавающей точкой. Конвейер V предназначен для выполнения простых целочисленных команд и некоторых команд с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, причем при выдаче устройством управления в одном такте пары команд более сложная команда поступает в конвейер U, а менее сложная – в конвейер V, см. табл. 6.2. Однако, такая попарная обработка команд (спаривание) возможна только для ограниченного подмножества целочисленных команд. Команды вещественной арифметики не могут запускаться в паре с целочисленными командами. Одновременная выдача двух команд возможна только при отсутствии зависимостей по регистрам.

Таблица 6.2

Конвейеризация команд в МП Pentium

Этапы конвейеров

|

|

|

|

Циклы шины |

|

|

|

|

PF |

К1 |

К3 |

К5 |

К7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

К2 |

К4 |

К6 |

К8 |

|

|

|

|

|

D1 |

|

К1 |

К3 |

К5 |

К7 |

|

|

|

|

К2 |

К4 |

К6 |

К8 |

|

|

|

|

D2 |

|

|

К1 |

К3 |

К5 |

К7 |

|

|

|

|

К2 |

К4 |

К6 |

К8 |

|

|

|

EX |

|

|

|

К1 |

К3 |

К5 |

К7 |

|

|

|

|

К2 |

К4 |

К6 |

К8 |

|

|

WB |

|

|

|

|

К1 |

К3 |

К5 |

К7 |

|

|

|

|

К2 |

К4 |

К6 |

К8 |

|

Процессор Pentium включает все особенности процессора Intel-486 и имеет ряд новых существенных черт, таких как:

суперскалярная архитектура, включающая два конвейера и позволяющая за один такт процессора выполнить более одной команды;

предсказание ветвлений в программе, что реализуется специальными логическими схемами, которые определяют точку передачи управления в программе и обеспечивают предварительную подготовку к выполнению определенных фрагментов программы;

конвейерное устройство для обработки данных с плавающей точкой (FPU);

90

раздельные кэш-памяти команд и данных емкостью 8 Кбайт каждая;

поддержка протокола обратной записи MESI (Modified/Exclusive/Shared/Invalid) для кэш-памяти данных;

64-разрядная ШД и 32-разрядная ША;

конвейеризация машинного цикла;

контроль на четность адреса и данных;

внутренний контроль на четность;

режим управления системой (System Management Mode).

Процессор Pentium включает полный набор команд процессора Intel-486 и содержит ряд новых команд, обеспечивающих расширение его функциональных возможностей.

Для предсказания ветвлений в программе процессор Pentium содержит два буфера предвыборки команд, один из которых обеспечивает предвыборку команд на линейном участке, а другой служит для предвыборки команд в соответствии с алгоритмом функционирования буфера целевого ветвления BTB (Branch Target Buffer). Это почти всегда позволяет осуществить предвыборку необходимой для выполнения команды.

Каждая кэш-память является двухканальной множественно-ассоциативной и имеет специальный буфер ассоциативной трансляции TLB (Translation Lookaside Buffer) для преобразования линейных адресов в физические. Кэш-память данных обеспечивает режим обратной (Writeback) или сквозной (Writethrough) записи строка за строкой и поддерживает протокол MESI.

Устройство управления памятью в процессоре Pentium поддерживает страницы до 4 Мбайт. Процессор Pentium Pro совместим со всеми приложениями, созданными для семейства IA-32.

Архитектура Pentium Pro в основном оптимизирована для работы с интенсивным использованием 32разрядных регистров (ШД – 64-разрядная).

Внутри корпуса микросхемы находятся два кристалла: процессор и кэш-память второго уровня емкостью 256 Кбайт.

ВPentium Pro применено динамическое исполнение программы. Этот термин определил 3

способа обработки данных:

глубокое предсказание ветвлений (с вероятностью > 90% можно предсказать 10=15 ближайших переходов);

анализ потока данных (на 20-30 шагов вперед посмотреть программу и определить зависимость команд по данным или ресурсам);

опережающее исполнение команд (ЦП P6 может выполнять команды в порядке, отличном от их следования в программе).

Многие алгоритмы работы с мультимедийными данными допускают простейшие элементы распараллеливания, когда одна операция может выполняться параллельно над несколькими числами. Такой подход называется SIMD – single-instruction multiple-data (одна инструкция - множество данных). Впервые эта технология была реализована в поколении P55 (микропроцессор Pentium MMX).

MMX (Multi-Media eXtension) – это SIMD-расширение для потоковой обработки целочисленных данных, реализованное на основе блока FPU (с использованием регистров FPU). Набор инструкций MMX оперирует 64-битными регистрами MM0-MM7, являющимися псевдонимами для младшей 64-битной части регистров FPU R0-R7), так что одновременное выполнение команд MMX и вещественной арифметики невозможно. Инструкции MMX оперируют 64-битными типами данных: упакованные байты (8 х 8 бит); упакованные слова (4 х 16 бит); упакованные двойные слова (2 х 32 бит); четверное слово (1 х 64 бит).

Таким образом, одна инструкция MMX может выполнить арифметическую или логическую операцию над "пакетами" целых чисел, упакованных в регистрах MMX. Например, инструкция PADDSB складывает 8 байт одного "пакета" с соответствующими восьмью байтами другого пакета, фактически выполняя сложение восьми пар чисел одной инструкцией.

Первый процессор P6 (Pentium Pro) был разработан до выхода Pentium MMX, поэтому в нем отсутствует эта возможность, однако в последующих моделях P6 данная технология закрепилась.

Впроцессоре Pentium II соединены лучшие свойства процессоров Intel: производительность процессора Pentium Pro и возможности технологии MMX. Это сочетание обеспечивает существенное увеличение производительности процессоров Pentium II по сравнению с предыдущими процессорами IA-32-архитектуры. Процессор содержит раздельные внутренние блоки кэш-памяти команд и данных по 16 Кбайт и 512 Кбайт общей неблокирующей кэш-памяти второго уровня.

91

Впервые реализована высокопроизводительная архитектура двойной независимой шины (системная шина и шина кэш), обеспечивающая повышение пропускной способности и производительности, а также масштабируемость при использовании будущих технологий.

Развитием идеи SIMD для вещественных чисел стала технология SSE (Streamed SIMD Extensions), впервые представленная в процессорах Pentium III. Блок SSE дополняет технологию MMX восемью 128-битными регистрами XMM0-XMM7 и 32-битным регистром управления и состояния MXCSR. Регистры XMM0-XMM7 независимы, т.е., в отличие от регистров MM0-MM7, не отображаются ни на какие другие регистры процессора. Инструкции SSE оперируют 128-битным типом данных – "упакованные одинарной точности" (4 х 32 бит), содержащим 4 вещественных числа в формате IEEE-754 single precision. Инструкции SSE могут выполнять операции над "пакетами" вещественных чисел, т. е. одна инструкция выполняет операцию над пакетом из четырех пар вещественных чисел.

В МП Pentium 4 была представлена технология SSE2, дополняющая SSE новыми типами данных и новыми инструкциями. Инструкции SSE2 также оперируют 128-битными регистрами XMM0-XMM7, но при этом добавлены пять новых типов данных: упакованные двойной точности (2 х 64 бит IEEE-754 double precision); упакованные байты (16 х 8 бит); упакованные слова (8 х 16 бит); упакованные двойные слова (4 х 32 бит); упакованные четверные слова (2 х 64 бит).

92

Управляющие Данные |

|

|

32 - я шина адресов |

|

|

|

|

|

|

Управляющие сигналы |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 - я шина данных |

|

|

|

|

|

|||||||||||||||

сигналы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

Управление |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Шина |

|

|

|

|

|

DP |

|

|

|

|

|

|

|

|

|

|

|

|

APIC |

64 |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Регистры для целых чисел |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

TBL |

|

|

|

|

|

|

|

|

|

|

|

Выдача |

|

|

|

Страничка |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

АЛУ (конвейер U) |

|

|

|

|

|

адресов |

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер |

||

|

|

|

Кэш данных |

|

|

|

|

|

|

|

|

|

|

конвейером U |

|

|

|

|

|

|

|

|

|

|

|

разветвления |

||||||||

|

|

|

|

|

|

|

АЛУ (конвейер V) |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Выдача |

|

|

|

|

Счетчик команд |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Сдвигающий регистр |

|

|

|

|

|

адресов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

конвейером V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буфер |

|

|

|

TBL |

|

|||

|

|

Математический сопроцессор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

предварительной |

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

выборки |

|

|

|

Кэш команд |

||||

|

|

|

|

|

|

Устройство управления |

|

|

|

|

|

|

|

Устройство |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Дешифратор |

256 |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

управления |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

Регистры |

|

|

|

|

|

|

|

|

|

|

|

команд |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Add |

Divide |

Multiply |

|

Управление |

|

|

80 |

|

|

|

|

32 |

ROM |

|

|

|

|

Рис. 6.3. Структурная схема процессора Pentium

93

Повышение производительности IA-32 достигалось не только путем оптимизации конвейера команд и добавления исполнительных блоков, но и, например, внедрением кэш-памяти в ядро процессора. В семействе IA-32 встроенный кэш L1 размером 8 Кбайт впервые был реализован в процессорах Intel-486. В процессорах Pentium размер кэша был удвоен. Первые представители P6 (Pentium Pro) содержали также кэш L2 размером 256 или 512 Кбайт. Однако такое решение в то время оказалось слишком дорогим и невыгодным, поэтому в Pentium II была представлена технология Dual Independent Bus (DIB) – двойная независимая шина. Процессор выполнялся в виде картриджа с печатным краевым разъемом, на который выведена системная шина. На картридже размером 14х6,2х1,6см устанавливались микросхема ядра процессора (CPU Core), несколько микросхем, реализующих вторичный кэш, и вспомогательные дискретные элементы (резисторы и конденсаторы). Удаление вторичного кэша из кристалла процессора позволило использовать для кэш-памяти и памяти тегов микросхемы сторонних производителей, специализирующихся на выпуске сверхбыстродействующей памяти. Объем вторичного кэша определялся емкостью и числом установленных микросхем памяти. Для доступа к кэшу и для доступа к внешней памяти использовались раздельные шины. Такое же архитектурное решение использовалось в первых моделях Pentium III. Начиная с 1999 года (Pentium III Coppermine), кэш L2 вновь был возвращен внутрь кристаллов процессоров.

Процессор Pentium 4 является 32-разрядным представителем семейства IA-32, по микроархитектуре принадлежащим к новому, седьмому (по классификации Intel) поколению. С программной точки зрения он представляет собой процессор IA-32 с очередным расширением системы команд – SSE2. По набору программно-доступных регистров Pentium 4 повторяет процессор Pentium III. С внешней, аппаратной точки зрения – это процессор с системной шиной нового типа, в которой кроме повышения тактовой частоты применены ставшие уже привычными принципы двойной (2х) и четырехкратной (4х) синхронизации, а также предпринят ряд мер по обеспечению работоспособности на ранее немыслимых частотах. Микроархитектура процессора, получившая название NetBurst, см. рис. 6.4, разработана с учетом высоких частот как ядра (>1,4 ГГц), так и системной шины (400 МГц). Название микроархитектуры указывает на сетевую направленность процессора: его мощь необходима для ресурсоемких мультимедийных Интернет-приложений.

Системная шина

Шинный

интерфейс

Кэш L2 |

Кэш L1 |

Выборка/ |

Кэш |

Исполнение |

Удаление |

исполненных |

|||

Декодирование |

трассы |

|

команд |

Предсказание |

|

|

|

ветвлений |

|

|

|

Рис. 6.4. Микроархитектура NetBurst

Процессор Pentium 4 является однокристальным. Кроме собственно вычислительного ядра, он содержит кэш-память двух уровней. Вторичный кэш, общий для инструкций и данных, имеет размер 256 Кбайт и разрядность шины 256 бита (32 байта), как и в последних процессорах Pentium III. Шина вторичного кэша работает на частоте ядра, что обеспечивает ее пропускную способность 32х1,4 = 44,8 Гбайт/с на частоте 1,4 ГГц. Вторичный кэш имеет ЕСС-контроль, позволяющий обнаруживать и исправлять ошибки. Первичный кэш данных имеет такую же высокую пропускную способность (44,8 Гбайт/с), но его объем сократился вдвое (8 Кбайт против 16 в Pentium III). Первичный кэш

94

инструкций в привычном понимании отсутствует, его заменил кэш трассы (trace cache). В нем хранятся последовательности микроопераций, в которые декодированы инструкции. Здесь могут помещаться до 12К микроинструкций.

Интерфейс системной шины процессора рассчитан только на однопроцессорные конфигурации, отсутствует также возможность избыточного функционального контроля (FRC). Интерфейс во многом напоминает шину Р6, протокол также ориентирован на одновременное выполнение нескольких транзакций. В процессоре Pentium 4 частота шины 400 МГц с "четырехкратной накачкой" (quad pumped) – тактовая частота системной шины составляет 100 МГц, но частота передачи адресов и данных выше. Новая информация по линиям с общей синхронизацией может передаваться на каждом такте с частотой 100 МГц. Для 2 и 4-кратной передачи используется синхронизация от источника данных. По шине адреса информация передается в режиме 2-кратной передачи, стробами являются два сигнала ADSTB0# и ADSTB1#. По спаду этих стробов передается адрес, а по фронту – информация о типе транзакции. Таким образом, в каждом такте шины (за 10 нс) передается и адрес, и тип транзакции (у Р6 на это требовалось 2 такта, что занимало 15-30 нс). По шине данных информация передается с четырехкратной частотой, для чего используются пары стробирующих сигналов DSTBp[0:3]# и DSTBn[0:3]# с периодом 5 нс (частота 200 МГц). Стробы сдвинуты относительно друг друга на 2,5 нс (половину своего маленького такта), синхронизация по их спадам и дает учетверенную частоту передачи.

Разрядность шины данных, как и в предыдущих двух поколениях процессоров, составляет 64 бита (8 байт), что в режиме 4-кратной передачи дает максимальную пропускную способность 100х4х8=3,2 Гбайт/с. У процессоров Pentium III шина обеспечивала 133х8=1,06 Гбайт/с. Шина адреса имеет разрядность 36 бит, и это позволяет адресовать те же 64 Гбайт памяти, из которых кэшируются только первые 4 Гбайт.

Исполнительные устройства МП (АЛУ) работают на удвоенной частоте, что дает возможность выполнять большинство целочисленных инструкций за половину такта. По сравнению с предыдущими поколениями IA-32, Pentium 4 содержит самый длинный конвейер команд, состоящий из 20 этапов и названный гиперконвейером.

На протяжении всего развития процессоров семейства Intel Pentium 4 основным средством повышения производительности было наращивание тактовой частоты. Собственно, сама архитектура NetBurst, положенная в основу процессоров Intel Pentium 4, была изначально рассчитана на масштабирование по частоте. Своеобразие этой микроархитектуры заключалось в беспрецедентно длинном конвейере, что и позволяло наращивать тактовые частоты. Но с ростом тактовой частоты соответствующим образом росла и потребляемая мощность процессоров и, как следствие, тепловыделение. И даже переход с 130 – нанометрового технологического процесса производства процессоров на 90-нанометровый не смог в полной мере решить всех проблем. Казалось бы, развитие архитектуры NetBurst зашло в тупик, наткнувшись на проблему тепловыделения. Переход на 65нанометровый техпроцесс, конечно, позволит создать некий технологический запас по наращиванию тактовой частоты, однако очевидно, что камнем преткновения опять станет тепловыделение процессора и невозможность его охлаждения. В результате тактовую частоту, скорее всего, удастся повысить, возможно – даже до 5 ГГц, но ради прироста производительности всего на 20-30% тратить миллиарды долларов на разработку нового техпроцесса производства нецелесообразно [20].

Разумеется, говорить о том, что наращивание тактовой частоты – это единственный путь увеличения производительности процессоров с архитектурой NetBurst, было бы не вполне корректно. С каждой новой версией процессорного ядра, то есть с переходом на новый техпроцесс производства, небольшие изменения претерпевала и микроархитектура ядра. Так, длина конвейера постепенно увеличивалась за счет добавления передаточных степеней Drive, что способствовало возможности дальнейшего увеличения тактовой частоты; увеличивался размер кэша L2; совершенствовались отдельные блоки процессора. Кроме того, в свое время архитектура NetBurst была дополнена технологией Hyper-Threading (Hyper-threading (HT) – гиперпоточность). Эта технология увеличивает производительность процессора при определённых рабочих нагрузках путём предоставления «полезной работы» (useful work) исполнительным устройствам (execution units), которые иначе будут бездействовать, например, в случаях кэш-промаха.

Технология HT является чем-то средним между многопоточной обработкой, реализованной в мультипроцессорных системах, и параллелизмом на уровне инструкций, реализованном в однопроцессорных системах. С точки зрения операционной системы и запущенного приложения в системе существует два процессора, что дает возможность распределять загрузку между ними.

95

Посредством реализованного в технологии HT принципа параллельности можно обрабатывать инструкции в параллельном режиме (все инструкции разделяются на два параллельных потока).

В конструктивном плане процессор с поддержкой технологии HT состоит из двух логических процессоров, каждый из которых имеет свои регистры и контроллер прерываний (Architecture State, AS). Таким образом, две параллельно исполняемые задачи работают со своими собственными независимыми регистрами и прерываниями, но при этом используют одни и те же ресурсы процессора для выполнения своих задач. После активизации каждый из логических процессоров может самостоятельно и независимо от другого процессора выполнять свою задачу, обрабатывать прерывания либо блокироваться. Таким образом, от реальной двухпроцессорной конфигурации новая технология отличается только тем, что оба логических процессора используют одни и те же исполняющие ресурсы, одну и ту же разделяемую между двумя потоками кэш-память и одну и ту же системную шину. Идея технологии HT тесно связана с микроархитектурой NetBurst процессора Pentium 4 и является в каком-то смысле ее логическим продолжением. Микроархитектура Intel NetBurst позволяет получить максимальный выигрыш производительности при выполнении одиночного потока инструкций, то есть при выполнении одной задачи. Однако, даже в случае специальной оптимизации программы, не все исполнительные модули процессора оказываются задействованными на протяжении каждого тактового цикла. В среднем, при выполнении кода, типичного для набора команд IA-32, реально используется только 35% исполнительных ресурсов процессора, а 65% исполнительных ресурсов процессора простаивают, что означает неэффективное использование возможностей процессора [19]. Было бы логично реализовать работу процессора таким образом, чтобы в каждом тактовом цикле максимально использовать его возможности. Именно эту идею и реализует технология HT, подключая незадействованные ресурсы процессора к выполнению параллельной задачи.

Увеличение тактовой частоты не может быть бесконечным и определяется технологией изготовления процессора. При этом рост производительности не является прямо пропорциональным росту тактовой частоты, то есть наблюдается тенденция насыщаемости, когда дальнейшее увеличение тактовой частоты становится нерентабельным. Количество инструкций, выполняемых за время одного такта, зависит от микроархитектуры процессора: от количества исполнительных блоков, от длины конвейера и эффективности его заполнения, от блока предвыборки, от оптимизации программного кода к данной микроархитектуре процессора. Поэтому сравнение производительности процессоров на основании их тактовой частоты возможно только в пределах одной и той же архитектуры (при одинаковом значении количества выполняемых операций в секунду).

Невозможность эффективного масштабирования тактовой частоты процессоров привела к постепенному переходу к двухъядерной, а в дальнейшем и к многоядерной архитектуре, см. главу 9.

Переход к двухъядерной архитектуре процессоров на самом деле позволяет повысить их производительность, но с одной оговоркой. Для этого требуется использовать приложения, которые могли бы хорошо распараллеливаться, то есть были бы изначально ориентированы на многопроцессорность.

Одно из решений данной проблемы связано с реализацией концепции "параллелизма на уровне тредов (потоков)" – TLP (Thread Level Parallelism). Если программные коды не в состоянии загрузить работой все или даже большинство функциональных устройств, то можно разрешить процессору выполнять более чем одну задачу (тред, или поток), чтобы дополнительные потоки загрузили простаивающие устройства. Здесь нетрудно усмотреть аналогию с многозадачной операционной системой: чтобы процессор не простаивал, когда задача оказывается в состоянии ожидания (например, завершения ввода-вывода), операционная система переключает процессор на выполнение другой задачи. Более того, некоторые механизмы диспетчеризации в операционной системе (например, квантование) имеют аналоги в многопотоковой архитектуре (MTA – MultiThreading Architecture). Очевидно, архитектура, поддерживающая параллелизм на уровне потоков (TLP), должна гарантировать, что треды не будут использовать одновременно одни и те же ресурсы, для чего требуются дополнительные аппаратные средства (например, дублирование регистровых файлов). При использовании базового типа параллелизма на уровне потоков в микропроцессоре необходимо иметь не менее двух аппаратных расширений для потоков. Это регистры общего назначения, счетчик команд, слово состояния процесса и т. п. В любой момент времени работает только один поток (тред). Он выполняется до возникновения определенной ситуации (например, выполнения команды загрузки регистра при отсутствии данных в кэш-памяти). В этом случае процессор переключается на выполнение другого потока. Поскольку при непопадании в кэш-память операции с памятью могут потребовать до сотни тактов процессора, его простои по

96

причине ожидания данных могли бы быть весьма значительными. Современные процессоры, имеющие возможности спекулятивного внеочередного выполнения команд, в подобной ситуации могут продолжить выполнение других команд, но на практике число независимых команд быстро исчерпывается и процессор останавливается. Архитектура с одновременным выполнением тредов – SMT (Simultaneous Multi-Threading) допускает одновременное выполнение нескольких потоков. В этом случае на каждом новом такте на выполнение в какое-либо исполнительное устройство может направляться команда любого потока. По сравнению с суперскалярными процессорами, поддерживающими внеочередное спекулятивное выполнение команд и использующими механизм переименования регистров, для SMT необходимы, в частности, следующие аппаратные средства:

несколько счетчиков команд (по одному на поток) с возможностью выбора любого из них на каждом такте;

средства, ассоциирующие команды с потоком, которому они принадлежат (необходимы, в частности, для работы механизмов предсказания переходов и переименования регистров);

несколько стеков адресов возврата (по одному на поток) для предсказания адресов возврата из подпрограмм;

специальная дополнительная память в процессоре (в расчете на каждый поток) для

процедуры удаления из буфера выполненных вне очереди команд.

Одна из основных особенностей SMT у многих современных процессоров – переименование регистров, когда логические (архитектурные) регистры отображаются в физические, с которыми и ведется реальная работа. Техника переименования регистров может, очевидно, применяться для того, чтобы избежать прямого дублирования файлов регистров, как аппаратной принадлежности потока.

В современных приложениях в любой момент времени, как правило, выполняется не одна, а несколько задач или несколько потоков, называемых также нитями. В качестве примера рассмотрим работу двух потоков. При одновременном исполнении обоих потоков процессор будет постоянно переключаться между потоками, за один такт процессора выполняются только инструкции какоголибо одного из потоков. На каждом такте процессора используются далеко не все исполнительные блоки процессора, поэтому имеется возможность частично совместить выполнение инструкций отдельных потоков на каждом такте процессора. Например, выполнение двух арифметических операций с целыми числами первого потока можно совместить с загрузкой данных из памяти второго потока и выполнить все три операции за один такт процессора. Аналогично на втором такте процессора можно совместить операцию сохранения результатов первого потока с двумя операциями второго потока и т.д. Собственно, в таком параллельном выполнении двух потоков и заключается основная идея технологии HT. Hyper-Threading – это виртуальная многопроцессорность, так как процессор на самом деле один, а операционная система видит два процессора. Классическому "одноядерному" процессору добавили еще один логический блок управления AS (Architectural State) технологии IA-32.

AS отслеживает состояние регистров (общего назначения, управляющих, прерываний – APIC, служебных), используя единственное физическое ядро (блоки предсказания ветвлений, ALU, FPU, SIMD-блоки и пр.) AS1 представляет из себя один логический процессор (LP1), AS2 - второй логический процессор (LP2). У каждого логического процессора есть свой собственный контроллер прерываний (APIC – Advanced Programmable Interrupt Controller) и набор регистров. Для корректного использования общих регистров двумя логическими процессорами существует специальная таблица

– RAT (Register Alias Table), согласно которой можно установить соответствие между регистрами общего назначения общего процессорного ядра. Таблица использования регистров RAT у каждого логического процессора своя. В результате получается схема, при которой на одном и том же ядре могут свободно выполняться два независимых потока программного кода.

У процессора с технологией Hyper-Threading предусмотрены два основных режима работы:

Single-Task (ST);

Multi-Task (MT).

В режиме ST активным является только один логический процессор, который безраздельно пользуется доступными ресурсами, другой логический процессор остановлен командой HALT. При появлении второго программного потока бездействовавший логический процессор активируется (посредством прерывания), и физический процессор переводится в режим работы с двумя потоками,

см. рис. 6.5.

При работе двух потоков поддерживаются две очереди инструкций (Next Instruction Pointers). Большая часть инструкций берется из кэш трассировки Trace Cache (TC), где они хранятся в декодированном виде, и доступ к кэш трассировки два активных логических процессора получают

97

поочередно, через такт. В то же время, когда активен только один логический процессор, он получает монопольный доступ к кэш трассировки без чередования по тактам. Аналогичным же образом происходит и доступ к памяти микропрограмм (Microcode ROM). Блоки трансляции инструкций

(ITLB - Instruction Translation Look-aside Buffer) действуют при отсутствии необходимых инструкций в кэш команд и доставляют команды, каждый для своего потока. Блок декодирования инструкций (IA-32 Instruction Decode) является разделяемым и в случае, когда требуется декодирование инструкций для обоих потоков, обслуживает их поочередно (через такт). Блоки очереди декодированных команд (Uop Queue) и блок распределения команд по исполнительным устройствам (Allocator) разделяются надвое, отводя по половине элементов для каждого логического процессора. Пять планировщиков (Schedulers) обрабатывают очереди декодированных команд, независимо от принадлежности их к какому либо потоку, и направляют команды на выполнение нужным исполнительным устройствам (Execution Units) в зависимости от готовности к выполнению команд и доступности исполнительных устройств. Кэш память всех уровней является полностью разделяемой между двумя логическими процессорами, но для обеспечения целостности данных записи в буфер данных (DTLB - Data Translation Look-aside Buffer) снабжаются дескрипторами в виде идентификатора (ID) каждого логического процессора. Начальная часть конвейера Pentium 4 отвечает за подачу микроопераций (декодированных x86 инструкций) на исполнительную часть конвейера. Именно тут, в основном, и находятся дублирующиеся блоки для каждого из двух логических процессоров. Кэш трассировки (Trace Cache) содержит уже декодированные инструкции. Большинство команд при реальной работе процессора декодировано заранее и находится в кэш трассировки. Trace Cache не дублируется для каждого из логических процессоров, а разделяется между ними. Тем не менее, у каждого логического процессора существует свой собственный блок трассировки, ссылающийся на следующую инструкцию для выполнения. Инструкции из Trace Cache выбираются по очереди и становятся в так называемую очередь выборки, также индивидуальную для обоих логических процессоров.

98

L2 Cache and Control

|

|

BTF & I-TLB (Блок |

|

2 |

|

|

|

BTF & I-TLB |

||||||

|

|

трансляции адреса команд) |

|

|

(Блок трансляции адреса команд) |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

Decoder (Дешифратор) |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

UCode ROM |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Trace Cache |

(Кеш трассировки) |

|

|||||||

(Память микропрограмм) |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

Rename/Alloc |

|

|

|

Rename/Alloc |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

uop Queues |

|

|

|

|

uop Queues |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Schedulers (Планировщики)

Execute Units (Исполнительные устройства)

Retiremen (Блок восстановления)

Re-Order Buffer |

|

Re-Order Buffer |

(Буфер восстановления порядка) |

|

(Буфер восстановления порядка) |

|

|

|

1,2

L1 D-Cache and D-TLB

Рис. 6.5. Разделение ресурсов двумя логическими процессорами

При отсутствии очередной инструкции в Trace Cache, являющемся в Pentium 4 по своей иерархии кэш памятью первого уровня для инструкций, процессор должен декодировать очередную x86 инструкцию из L2 – кэш второго уровня. Выборка инструкции осуществляется1,2 при участии блока трансляции адреса команд (Instruction Translation Lookaside BufferITLB), переводящем адрес,

хранящийся в блоке трассировки, в физический адрес. ITLB является также индивидуальным для каждого процессора, а L2-кэш разделяется между логическими процессорами. Декодер x86 инструкций в процессорах с технологией Hyper-Threading общий, поскольку его загрузка невелика – большинство декодированных инструкций уже хранится в Trace Cache. Если же оба логических процессора обращаются к декодеру одновременно, он чередует свою работу между логическими процессорами, но только после выполнения полного цикла декодирования для одного из логических CPU. Декодированные инструкции записываются в Trace Cache. К исполнительному устройству декодированные последовательности инструкций приходят в двух очередях – своя очередь для каждого из логических процессоров. В первую очередь инструкции из двух входящих очередей проходят через блоки выделения ресурсов (Allocator) и переименования регистров(Register Rename). Здесь происходит выделение необходимых ресурсов для исполнения команд. Машинные регистры и буферы делятся поровну между логическими процессорами, однако, при отказе одного из логических процессоров от использования тех или иных ресурсов, они могут быть всецело выделены только одному логическому процессору. После прохождения этой стадии команды попадают в две отсортированные очереди – для операций с памятью и для остальных операций, которые также разделены пополам – для каждого из логических процессоров.

Затем, рассортированные микрооперации приходят на стадию определения очередности выполнения (Scheduling), где выполняется сортировка порядка следования инструкций при поступлении на исполнительные устройства. Операции на блоки-планировщики приходят по мере поступления. При необходимости, планировщики переключаются с очередей одного логического процессора на очереди другого. На этом этапе, кстати, происходит окончательное смешение микроопераций, приходящих с логических процессоров, для возможности их одновременного исполнения. Поскольку машинные регистры физического процессора к этому моменту оказываются жестко привязанными к регистрам обоих логических процессоров, исполнение инструкций

99

действительно становится возможным без разбора принадлежности команд. После этапа выполнения, на котором процессор не различает логические процессоры, следует блок восстановления (Retirement), где восстанавливается изначальный порядок инструкций и их принадлежность к каждому из логических процессоров. При этом буфер восстановления порядка (Re-Order Buffer) делится пополам между логическими процессорами. Хотя кэш память первого и второго уровня является разделяемой между логическими процессорами, буфер трансляции данных (Data Translation Lookaside Buffer - DTLB), сопоставляющий адреса данных и их физические адреса, хоть и делится между процессорами, но записи в нем дополнены идентификатором процессора, которому принадлежит каждая из строк буфера. Таким образом, технология Hyper-Threading действительно позволяет загрузить исполнительные устройства процессора значительно сильнее за счет одновременного выполнения двух потоков. Однако, следует понимать, что эффект от такого приема не всегда может быть положительным. Во-первых, если выполняемые потоки похожи по типу выполняемых инструкций, выигрыша может не быть вовсе, поскольку один из потоков будет полностью занимать все ресурсы, необходимые и другому потоку. Простои же остальных исполнительных устройств процессора от этого не исчезнут. Во-вторых, возможна ситуация, когда один из потоков может попросту занять ресурсы, необходимые другому потоку, и ожидать при этом, например, поступления данных. Операционная система же при этом, пребывая в уверенности, что имеется два CPU, не будет предпринимать никаких действий, на самом же деле функционирование процессора будет попросту заблокировано.

Процессоры семейства Pentium имеют ряд архитектурных и структурных особенностей по сравнению с предыдущими моделями микропроцессоров фирмы Intel. Наиболее характерными из них являются:

гарвардская архитектура с разделением потоков команд и данных при помощи введения отдельных внутренних блоков кэш-памяти для хранения команд и данных, а также шин для их передачи;

суперскалярная архитектура, обеспечивающая одновременное выполнение нескольких команд в параллельно работающих исполнительных устройствах;

динамическое исполнение команд, реализующее изменение последовательности команд, использование расширенного регистрового файла (переименование регистров) и эффективное предсказание ветвлений;

двойная независимая шина, содержащая отдельную шину для обращения к кэш-памяти 2-го уровня (выполняется с тактовой частотой процессора) и системную шину для обращения к памяти и внешним устройствам (выполняется с тактовой частотой системной платы).

Основные характеристики процессоров семейства Pentium следующие:

32-разрядная внутренняя структура;

использование системной шины с 36 разрядами адреса и 64 разрядами данных;

раздельная внутренняя кэш-память первого уровня для команд и данных емкостью по 16

Кбайт;

поддержка общей кэш-памяти команд и данных второго уровня емкостью до 2 Мбайт;

конвейерное исполнение команд;

предсказание направления программного ветвления с высокой точностью;

ускоренное выполнение операций с плавающей точкой;

приоритетный контроль при обращении к памяти;

поддержка реализации мультипроцессорных систем;

наличие внутренних средств, обеспечивающих самотестирование, отладку и мониторинг производительности.

Вопросы для самоконтроля

1.Назовите основные блоки и их функциональное назначение в структуре IA-32.

2.Что нового появилось в архитектуре процессора Pentium III по сравнению с Pentium MMX?

3.Какие особенности имеет Net Burst-архитектура?

4.В чем состоит отличие кэш-команд ЦП Pentium IV от всех предыдущих?

100