- •Тема 3. Базовые логические элементы. Транзисторный ключ. Базовый элемент ТТЛ. Базовый элемент на КМДП структурах. Цифровые интегральные схемы.

- •1. Что такое регистры? Каково их назначение?

- •2.Чем определяется разрядность регистров?

- •3. Расскажите об устройстве регистров.

- •5. Какие триггеры используются для построения регистров.

- •6. Нарисуйте схему и опишите принцип работы последовательного регистра.

- •7. Какие функции может выполнять последовательный регистр?

- •8. Нарисуйте схему и опишите принцип работы параллельного регистра.

- •1. Что такое шифратор? Каково его назначение?

- •2. Каково назначение стробирующего входа дешифратора?

- •3. Опишите принцип работы шифратора.

- •4. Что такое дешифратор? Каково его назначение?

- •5. Опишите принцип работы дешифратора.

- •6. Что такое мультиплексор? Каково его назначение?

- •7. Опишите принцип работы мультиплексора.

- •8. Что такое демультиплексор? Каково его назначение?

- •9. Опишите принцип работы демультиплексора.

Контрольные вопросы.

1.Что такое шифратор? Каково его назначение?

2.Каково назначение стробирующего входа дешифратора?

3.Опишите принцип работы шифратора.

4.Что такое дешифратор? Каково его назначение?

5.Опишите принцип работы дешифратора.

6.Что такое мультиплексор? Каково его назначение?

7.Опишите принцип работы мультиплексора.

8.Что такое демультиплексор? Каково его назначение?

9.Опишите принцип работы демультиплексора.

34

Лабораторная работа №5 Исследование счетчиков электрических импульсов

Цель работы. Исследовать устройство и принцип действия счетчиков электрических импульсов.

Краткая теория. Счетчиком (CT – CounТer – счетчик) называют цифровое устройство осуществляющее счет поступивших на его вход импульсов. Количество импульсов, через которое повторяется исходное состояние счетчика, называют коэффициентом счета (модулем счета) Ксч. Счетчики состоят из цепочки последовательно включенных триггеров. Разрядность счетчика, а, следовательно, и число триггеров N определяются

Ксч.

По коэффициенту счета счетчики делятся на двоично-десятичные, двоичные, с произвольным постоянным модулем счёта, с переменным модулем счёта.

По направлению счета счетчики делятся на суммирующие, вычитающие и реверсивные. Счетчик называют суммирующим, если после каждого очередного импульса цифровой код на выходе счетчика увеличивается на единицу. В вычитающем счетчике после каждого импульса на входе счетчика цифровой код на выходе уменьшается на единицу. Счетчики, в которых возможно переключение с режима суммирования на режим вычитания, называются реверсивными.

По своей структуре счетчики делятся на последовательные, параллельные и параллельно-последовательные. Последовательный двоичный счетчик образован цепочкой последовательно включенных счетных триггеров. В параллельном счетчике счетные импульсы подаются одновременно на входы всех разрядов счетчика. Параллельные счетчики имеют большее быстродействие по сравнению с последовательными. Параллельно-последовательные счетчики имеют высокое быстродействие и большое значение коэффициента пересчета.

Асинхронный (последовательный) двоичный счетчик. Асинхронные двоичные счетчики строят из цепочки счетных триггеров, соединяя выход предыдущего с входом последующего. Результат счета отображается на выходах счетчика в виде параллельного двоичного кода числа сосчитанных импульсов. Коэффициент счета Ксч = 2N. Так как из 2N состояний одно приходится на нулевое состояние, то максимальное число, при котором счетчик полностью заполняется единицами, равно 2N-1.

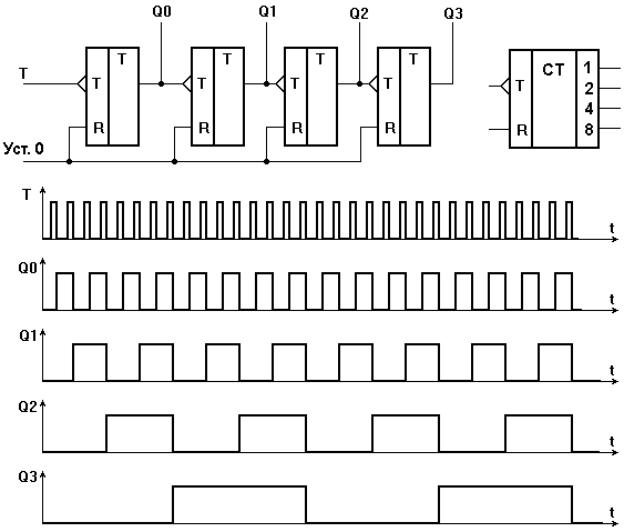

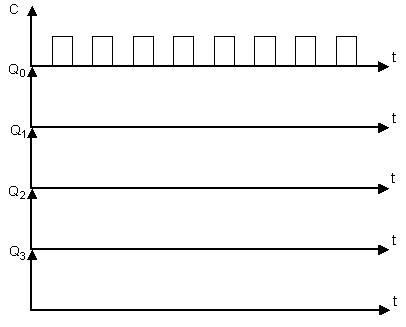

На рис. 1 изображены четырехразрядный двоичный счетчик на Т - триггерах, срабатывающих по срезу входного сигнала, и временные диаграммы, описывающих его работу. С приходом каждого следующего импульса параллельный двоичный код на выходе счетчика увеличивается на единицу. Число сосчитанных импульсов, после которых счетчик заполняется единицами, равно 15. По срезу 16-го импульса последовательно опрокидываются все триггеры, и счетчик переходит в исходное нулевое состояние. Поэтому 16-й импульс называют также и нулевым.

35

Рис. 1

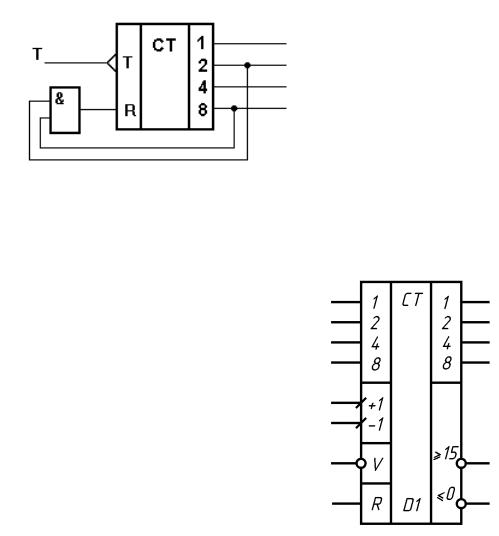

Счетчики с произвольным коэффициентом счета Ксч строятся на основе микросхем двоичных и двоично-десятичных счетчиков. Одним из способов получения произвольного значения модуля счета является использование цепи обратной связи, сбрасывающей его в нулевое состояние, как только суммирующий счетчик переходит в состояние, равное Ксч.

Для счетчика с Ксч = 10 нужны четыре триггера. Счетчик должен иметь десять устойчивых состояний (0, 1, …, 9). В том такте, когда он должен был перейти в состояние 1010 (число 10), его необходимо установить в исходное нулевое состояние (0000). Для такого счетчика можно использовать любой четырехразрядный счетчик (рис. 2) и элемент И. Выход элемента И соединяют со входом установки счетчика в 0 (вход R). А входы соединяют с выходами счетчика на которых в интересуемом состоянии появляются логические единицы. В самом начале одиннадцатого состояния на обоих входах элемента И микросхемы появляются логические 1, вырабатывающие сигнал сброса всех триггеров счетчика в нулевое состояние.

36

Рис. 2 Рассмотренный счетчик является двоичным эквивалентом счетной

декады, представляющим любую десятичную цифру ее двоичным кодом. Поэтому такой счетчик называют двоично-десятичным, а его выходной код – двоично-десятичным кодом (или кодом 8421).

Счетчик с предварительной установкой может устанавливаться в начальное состояние, равное любому числу от 0 до Ксч – 1. Эта операция осуществляется параллельной записью в счетчик кода необходимого числа. Счет (сложение или вычитание) будет начинаться уже не с нуля, а с установленного числа.

Счетчики с предварительной установкой обычно являются универсальными и могут работать в режиме сложения, вычитания, установки заданного кода,

установки (сброса) нуля, например |

микросхема |

К155ИЕ7 (рис. 3). |

Рис. 3 |

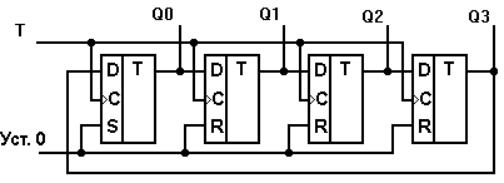

Кольцевой счетчик можно получить из регистра сдвига, если выход последнего триггера соединить с D – входом первого (рис. 4). Перед началом счета, импульсом начальной установки, в нулевой разряд счетчика (Q0) записывается логическая 1, в остальные разряды – логические 0. С началом счета каждый из приходящих счетных импульсов Т переписывает 1 в следующий триггер. Число поступивших импульсов определяется по номеру выхода, на котором имеется 1. Предпоследний (n – 1) – импульс переведет в единичное состояние последний триггер, а n – импульс переписывает единичное состояние на выход нулевого триггера, и счет начинается сначала. Коэффициент счета кольцевого счетчика равен числу триггеров (Ксч = N). Изменяя число триггеров N можно построить счетчик с произвольным коэффициентом счета.

37

Рис. 4

Главная область применения кольцевых счетчиков – распределители импульсов, создающие необходимую временную последовательность управляющих сигналов.

Выполнение работы. Работа выполняется на платах П3 и П5 с использованием технических карт III-1, V-1, V-2, V-3.

Карта III-1 предназначена для исследования последовательного четырехразрядного регистра и кольцевого четырехразрядного счетчика (см. лаб. раб. №3). Для перевода регистра в режим кольцевого счетчика записывают в него 0001, а затем соединяют внешней перемычкой штырьки Y и X (на плате П3). После этого с подачей каждого следующего тактового импульса (SB1) единица будет последовательно смещаться по разрядам счетчика.

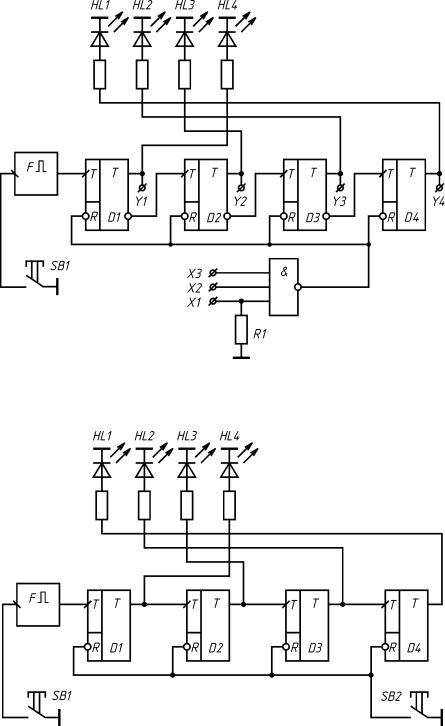

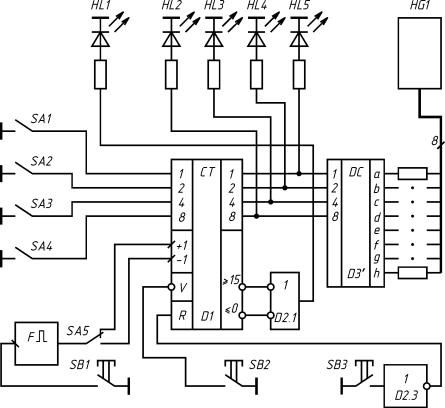

Карта V-1 (рис. 5) предназначена для исследования суммирующего счетчика с переменным коэффициентом счета, при этом тумблер SA5 должен находится в положении «1». Счетные импульсы формируются по нажатию кнопки SB1. Для изменения коэффициента счета необходимо какие либо выходы Y1 – Y4 соединить перемычками со входами X1 – X3. При любых коэффициентах счета (кроме Ксч = 16) с одним из выходов счетчика обязательно соединяется вход Х1. В противном случае коэффициент счета не изменится и будет равен 16.

Карта V-2 (рис. 6) предназначена для исследования вычитающего счетчика. Тумблер SA5 должен находится в положении «0».

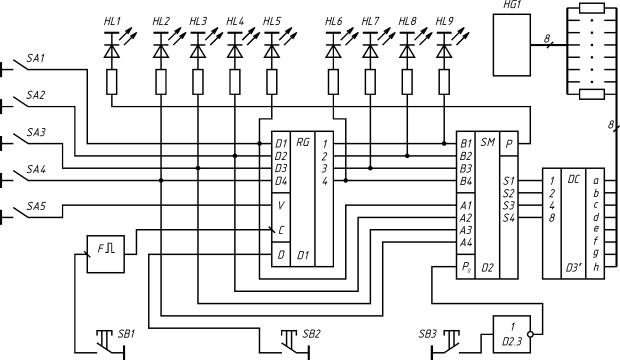

КартаV-3 (рис. 7) предназначена для исследования универсального реверсивного счетчика с предустановкой. Тумблеры SA4 – SA1 задают сигналы, которые можно записать в счетчик по нажатию кнопки SB2 (режим предустановки). Тумблер SA5 обеспечивает подачу тактовых импульсов на входы суммирования (+1) или вычитания ( - 1). Сброс счетчика производится кнопкой SB3. Информация, записанная в счетчик индицируется как в двоичном (HL2 – HL5), так и в шестнадцатеричном (HG1) кодах. Индикатор HL1, индицирует сигнал переноса в старшие разряды счетчика, как в режиме суммирования, так и в режиме вычитания.

38

Рис.5. Схема к карте V-1.

Рис.6. Схема к карте V-2.

39

Рис.7. Схема к карте V-3.

Задание.

1. Включив плату П3 (карта III-1), собрать функциональную схему кольцевого счетчика и исследовать его работу. Заполнить таблицу состояний (табл. 1) и построить экспериментальные диаграммы (рис. 8).

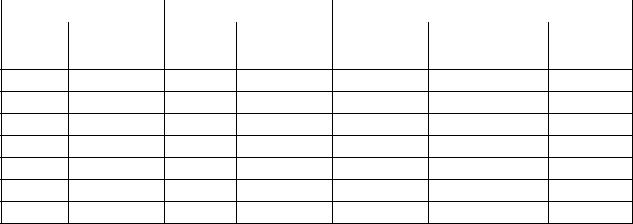

Таблица 1

№ импульса |

Q0 |

Q1 |

Q2 |

Q3 |

|

HL1 |

HL2 |

HL3 |

HL4 |

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

2 |

|

|

|

|

3 |

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

40

Рис. 8

2. Исследовать функциональную схему четырехразрядного двоичного суммирующего счетчика (плата П5, карта V-1). Первоначально подачей входных импульсов установить на выходе счетчика нулевой код. Затем, подавая одиночные импульсы и используя светодиодную индикацию, заполнить таблицу состояний счетчика в режиме прямого счета (табл. 2).

Таблица 2, 3, 4. (нарисовать 3 таблицы)

№ импульса |

Q3 |

Q2 |

Q1 |

Q0 |

|

HL1 |

HL2 |

HL3 |

HL4 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

4 |

|

|

|

|

5 |

|

|

|

|

6 |

|

|

|

|

7 |

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|

|

11 |

|

|

|

|

12 |

|

|

|

|

13 |

|

|

|

|

14 |

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

17 |

|

|

|

|

|

|

41 |

|

|

3. Изменить схему стенда (карта V-2) с целью реализации режима обратного счета. Заполнить таблицу состояний для указанного режима счетчика (табл. 3).

4. Собрать схему стенда для счетчика с коэффициентом счета, заданным преподавателем (карта V-1). Заполнить таблицу состояний счетчика (табл. 4) и нарисовать временные диаграммы сигналов на входах и выходах счетчика

(рис. 9).

Рис. 9

5. Исследовать работу счетчика на микросхеме К155ИЕ7 в режиме предварительной записи информации, а также в режимах прямого и обратного счета с переполнением или с обнулением счетчика (по заданию преподавателя).

Контрольные вопросы.

1.Что называется счетчиком?

2.Какие типы счетчиков Вам известны?

3.Опишите принцип действия кольцевых счетчиков?

4.Опишите принцип действия суммирующего счетчика.

5.Опишите принцип действия вычитающего счетчика.

6.Как задается счет чисел не равных 2N?

7.Особенности реверсивных счетчиков.

42

Лабораторная работа №6 Исследование четырехразрядного параллельного сумматора

Цель работы. Исследовать четырехразрядный параллельный сумматор.

Краткая теория. Двоичный сумматор (SM) служит для формирования арифметической суммы n-разрядных двоичных чисел А и В. Результатом сложения (при n = 4) является четырехразрядная сумма S и выход переноса Р, который можно рассматривать как пятый разряд суммы.

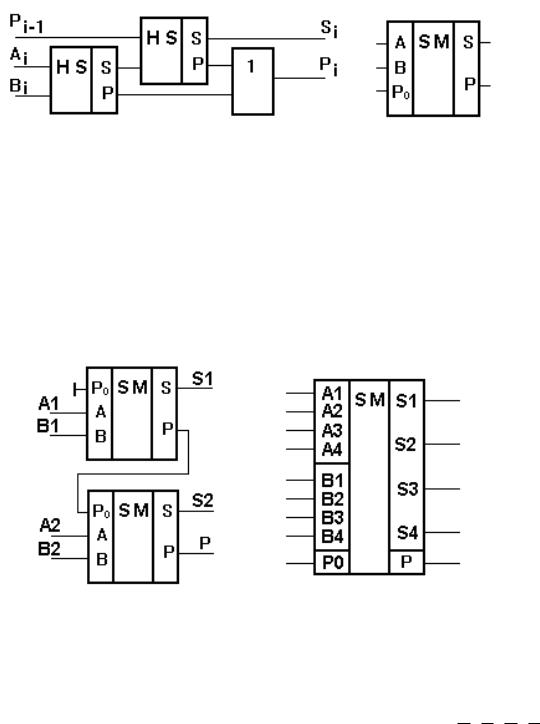

Полусумматор (HS - HalfSum - полусумма), - это устройство, производящее сложение двух одноразрядных двоичных чисел. Его можно реализовать на логических элементах по таблице истинности (рис. 1).

Входы |

Выходы |

||

|

|

|

|

Ai |

Bi |

Si |

Pi |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

Рис. 1

Полный одноразрядный сумматор суммирует три одноразрядных двоичных числа: два слагаемых Ai, Bi и перенос, поступивший из младшего разряда Pi-1. Полный одноразрядный сумматор можно построить из двух полусумматоров HS и логического элемента ИЛИ (рис. 2). Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда.

|

Входы |

|

|

Выходы |

|

Ai |

Bi |

Pi-1 |

Si |

|

Pi |

0 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

0 |

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

0 |

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

1 |

43

Рис. 2

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие собой в простейшем виде последовательное соединение одноразрядных сумматоров (рис. 3 а). В корпусе микросхемы К155ИМ3 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора (рис. 3 б). Сигнал переноса последовательно передается с выхода предыдущего разряда сумматора на вход переноса следующего разряда.

а |

б |

Рис. 3

Вычитание двух чисел обычно сводится к операции сложения. Для замены операции вычитания операцией сложения вычитаемое В (Впр=В4В3В2В1) представляется в дополнительном коде. Дополнительный

код Вдоп

образуется из обратного (инверсного) кода (

Вобр

В4В3В2В1

)

добавлением к нему единицы (Вдоп=Вобр+1).

Очевидно, для четырехразрядных чисел, записанных в этих кодах, справедливы равенства

Впр+ Вобр=1111; Впр+ Вдоп= Впр+ Вобр+1=1111+1=10000;

Впр=10000 – Вдоп=10000 – Вобр – 1.

Следовательно, операцию вычитания можно представить в виде

Апр – Впр = Апр + Вдоп – 10000.

44

Пример.

7 – 3 = 4;

Апр=0111, Впр=0011, Вобр=1100, Вдоп=1100+0001=1101,

Апр – Впр = Апр + Вдоп – 10000=0111 + 1101 – 10000=0100.

Таким образом при выполнении операции вычитания вычитаемое В преобразуется в дополнительный код. А вычитание числа 10000 производится без специальных схем, только с использованием сигнала переноса в старший (пятый) разряд.

Выполнение работы. Работа выполняется на плате П3 с использованием технологической карты III-3.

Рис. 4. Схема к карте III-3.

Карта III-3 (рис. 4) предназначена для исследования работы сумматора двух четырехразрядных двоичных чисел на микросхеме К155ИМ3 (D2). Для задания двух четырехразрядных слагаемых используются тумблеры SA4 – SA1 (слагаемое А) и регистр D1 (слагаемое В). Ввод слагаемого В в регистр может осуществляться как в параллельном (с тумблеров SA4 – SA1), так и в последовательном (с кнопки SB2) режимах. Сигнал начального переноса Р0 подается с кнопки SB3 через инвертор D2.3. Индикация слагаемых осуществляется индикаторами HL2 – HL5 и HL6 – HL9. Сигнал переноса в старший (пятый) разряд подается на индикатор HL1. Сумма в четыр ех

45

первых разрядах дешифруется в блоке индикации и высвечивается в виде шестнадцатеричного числа на семисегментном индикаторе.

Задание.

1.Собрать схему стенда для исследования работы четырехразрядного сумматора (карта III-3).

2.Провести исследование работы четырехразрядного параллельного сумматора. В процессе исследования провести сложение четырехразрядных

двоичных чисел (операндов) указанных преподавателем. Результаты суммирования проверить при переводе значений в десятичный код и занести

в таблицу 1. |

|

|

|

|

|

|

Таблица 1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А |

|

В |

|

S |

|

|

|

|

|

|

|

|

Десятич |

Двоичный |

Десятичн |

Двоичный |

Десятичный |

Двоичный |

Шестнадца |

ный |

код |

ый |

код |

код |

код |

теричный |

код |

|

код |

|

|

|

код |

3. Провести вычитание четырехразрядных операндов указанных преподавателем, используя перевод вычитаемого в дополнительный код. Результаты суммирования проверить при переводе значений в десятичный код и занести в таблицу 2.

Таблица 2.

|

А |

|

|

В |

|

|

S |

|

|

|

|

|

|

|

|

|

|

Десяти |

Двоичн |

Десяти |

Двоичн |

Обратны |

Дополнит |

Десятичн |

Шестнад |

Двоичный |

чный |

ый код |

чный |

ый код |

й код |

ельный |

ый код |

цатеричн |

код |

код |

|

код |

|

|

код |

|

ый код |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контрольные вопросы.

1.Что называется полусумматором?

2.Опишите принцип действия полусумматора.

3.Что называется полным одноразрядным сумматором?

4.Опишите принцип действия полного одноразрядного сумматора.

5.Опишите структуру и принцип действия многоразрядного сумматора.

6.Как с помощь сумматора осуществляется операция вычитания?

46

ОГЛАВЛЕНИЕ

Программа……………………………………………………………………... 3

Литература……………………………………………...................................... 3

Техническое описание лабораторного стенда………....................................... 4

Л. Р. №1 Исследование основных логических элементов и простейших |

|

комбинационных устройств…………………………………………………... |

5 |

Л. р. №2 Исследование триггеров RS, D и Т типов…………………………. |

14 |

Л. р. №3 Исследование параллельного и последовательного регистров….. |

22 |

Л. р. №4 Исследование основных комбинационных устройств: |

|

дешифратора, демультиплексора, мультиплексора и преобразователя |

|

кодов на ПЗУ…………………………………………………………………... |

27 |

Л. р. №5 Исследование счетчиков электрических импульсов……………... |

35 |

Л. р. №6 Исследование четырехразрядного параллельного сумматора…… |

43 |

47