5. Структура с коммутатором типа “кроссбар»

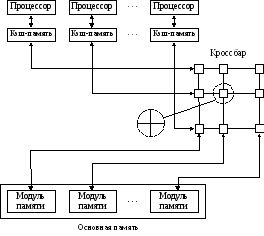

Архитектура с коммутатором типа «кроссбар» (рис. 11.6) ориентирована на модульное построение общей памяти и призвана разрешить проблему огра-ниченной пропускной способности систем с общей шиной.

Рис. 11.6. Структура SMP- системы с коммутатором типа «кроссбар»

Коммутатор обеспечивает множественность путей между процессорами и банками памяти, причем топология связей может быть как двумерной, так и трехмерной. Результатом становится более широкая полоса пропускания, что позволяет строить SMP-системы, содержащие больше процессоров, чем в случае общей шины. Типичное число процессоров в SMP-системах на базе матричного коммутатора составляет 32 или 64. Выигрыш в производительности достигается, когда разные процессоры обращаются к разным банкам памяти.

По логике кроссбара строится и взаимодействие процессоров с устройст-вами ввода/вывода.

Примером ВС с рассмотренной архитектурой является система Enterprise 10000, состоящая из 64 процессоров, связанных с памятью посредством матрич-ного коммутатора Gigaplane-XB фирмы Sun Microsystems (кроссбар 1616). В IBM RS/6000 Enterprise Server Model S70 коммутатор типа «кроссбар» обеспе-чивает работу 12 процессоров RS64. В SMP-системах ProLiant 8000 и 8500 фир-мы Compaq для объединения с памятью и между собой восьми процессоров Pentium III Xeon применена комбинация нескольких шин и кроссбара.

Концепция матричного коммутатора (кроссбара) не ограничивается сим-метричными мультипроцессорами. Аналогичная структура связей применяется для объединения узлов в ВС типа CC-NUMA и кластерных вычислительных системах.

6. Архитектура с многопортовой памятью

Многопортовая организация запоминающего устройства обеспечивает лю-бому процессору и модулю ввода-вывода прямой и непосредственный доступ к банкам основной памяти (ОП). Такой подход сложнее, чем при использова- нии шины, поскольку требует придания ЗУ основной памяти дополнительной, достаточно сложной логики. Тем не менее это позволяет поднять производи-тельность, так как каждый процессор имеет выделенный тракт к каждому мо- дулю ОП. Другое преимущество многопортовой организации – возможность на-значить отдельные модули памяти в качестве локальной памяти отдельного процессора. Эта особенность позволяет улучшить защиту данных от несанк-ционированного доступа со стороны других процессоров.

7. Архитектура с централизованным устройством управления

Централизованное устройство управления (ЦУУ) сводит вместе отдель- ные потоки данных между независимыми модулями: процессором, памятью, устройствами ввода/вывода. ЦУУ может буферизировать запросы, выполнять синхронизацию и арбитраж. Оно способно передавать между процессорами ин-формацию о состоянии и управляющие сообщения, а также предупреждать об изменении информации в кэшах. Недостаток такой организации заключается в сложности устройства управления, что становится потенциальным узким мес- том в плане производительности. В настоящее время подобная архитектура встречается редко, но она широко использовалась при создании вычислитель- ных систем на базе машин семейства IBM 370.