- •Встроенные микропроцессорные системы

- •Оглавление

- •2. Программное обеспечение встроенных систем ……….

- •Введение

- •Модуль 1

- •Аппаратные средства встроенных систем

- •1.2. Элементы архитектуры процессоров встроенных систем

- •1.2.1. Множество команд

- •1.2.3.1. Адресное пространство

- •1.2.3.2. Порядок байт

- •1. 2.3.3. Когерентность памяти

- •1. 2.3.4. Защита памяти

- •1. 2. 4. Модель прерываний

- •1.2. 5.Модель управления памятью

- •1.2.5.1. Страничная организация памяти

- •1.2.5.2. Сегментация памяти

- •1.3. Типы процессоров

- •1.4. Формы параллелизма в процессорах

- •1.4.1. Конвейеризация

- •1.4.2. Параллелизм уровня команд

- •1.5.Технологии памяти

- •1.5.1. Оперативная память

- •1.5.1. 1. Статическое озу

- •1.5.2. Постоянное запоминающее устройство (rom)

- •1.6. Иерархия памяти

- •1.6.1. Распределение или карта памяти

- •1.6.2. Блокнотная и кэш память

- •1.6.2.1. Кэш-память прямого отображения

- •1.6.2.2. Ассоциативная по множеству кэш-память

- •1.6.2.3. Обновление кэш-памяти.

- •1.6.2.4. Протокол когерентности кэширования с обратной записью

- •1.7. Магистраль микропроцессорной системы

- •1.8. Базовые устройства ввода-вывода встроенных систем

- •1.8.1. Порты ввода-вывода общего назначения

- •1.7.2. Таймер-счетчик

- •1.8.3. Импульсно-кодовая модуляция.

- •1.8.4. Многоканальный аналого-цифровой преобразователь

- •1.9. Базовые последовательные интерфейсы ввода-вывода

- •1.9.2. Последовательный интерфейс spi

- •1.9.4.1. Введение в usb

- •1.9.4.2. Интерфейс Open Host Controller для usb

- •Вопросы для самоконтроля

- •Модуль 2

- •1.10. Язык проектирования аппаратуры vhdl

- •1.10.2. Введение в vhdl

- •1.10.2.1. Программирование на vhdl для моделирования и синтеза [19]

- •1.10.2.2. Entity и architecture

- •1.10.2.3. Операторы присваивание и process [19]

- •1.10.2.4. Цикл моделирования vhdl

- •1.10.2.5. Многозначная логика и стандарт ieee 1164

- •1.11. Проектирование устройств ввода-вывода и контроллеров

- •1.12. Интегрированная среда разработки аппаратных средств

- •Вопросы для самоконтроля

- •Модуль 3

- •2. Программное обеспечение встроенных систем

- •2.1 Модель вычислений

- •2.2 Автомат с конечным числом состояний

- •2.3. Асинхронный язык проектирования sdl

- •2.4. Синхронный язык проектирования Lustre

- •2.5. Многозадачность.

- •2.5.1. Язык программирования Си

- •2.5.2. Потоки

- •2.5.2.1. Реализация потоков

- •2.5.2.2. Взаимное исключение

- •2.5.2.3. Взаимная блокировка

- •2.5.2.4. Модели непротиворечивости памяти

- •2.5.2.5. Проблемы с потоками

- •2.5.3. Процессы и передача сообщений

- •2.6. Интегрированная среда разработки прикладного программного

- •2.6.2. Комплект программ Telelogic Tau sdl Suite

- •2.6.3. Средства разработки программного обеспечения

- •2.7.1. Моделирование, эмуляция и макетирование

- •2.7.2. Формальная верификация

- •2.7.3. Оценка производительности

- •2.7.3.1. Оценка wcet

- •2.7.3.2. Исчисление реального времени

- •1 2 3 E

- •2.7.4. Модели энергии и мощности

- •2.7.5. Тепловая модель

- •Вопросы для самоконтроля

- •Заключение

- •Задания

- •1. Конвейеризация

- •2. Иерархия памяти

- •3. Базовые устройства ввода-вывода встроенных систем

- •5. Многозадачность

- •6. Валидация и оценка проекта

- •Библиографический список

- •Встроенные микропроцессорные системы

1.11. Проектирование устройств ввода-вывода и контроллеров

интерфейсов ввода-вывода по модели программно-управляемого автомата.

Поведенческий уровень является наивысшим уровнем абстракции поддерживаемым VHDL. Создание поведенческого описания устройства ведется в терминах операций, выполняемых во времени. Концепция времени является важным отличием между поведенческим описанием и низкоуровневым описанием. Примеры поведенческих форм представления могут содержать диаграммы состояний (графы переходов), временные диаграммы и алгоритмические описания.

В поведенческом описании концепция времени может быть выражена точно с помощью требуемых задержек между событиями или просто упорядочиванием выполнения операций. При создании проектов на VHDL для синтеза можно использовать поведенческие операторы, предполагая наличие регистров в устройстве. Необходимо иметь в виду, что современные средства синтеза игнорируют временные спецификации, оставляя реальные временные результаты на милость целевой технологии устройства. Синтезаторы также не способны поддерживать широкий спектр стилей описания.

Для тех, кто имеет дело с разработкой программного обеспечения, написание проектов на поведенческом уровне VHDL не будет казаться как что-нибудь новое. Разница состоит в базовой исполнительной платформе: в случае программного обеспечения все исполняет CPU; в случае VHDL исполнителем является симулятор или синтезированная аппаратура.

На поведенческом уровне описание может выполняться в виде алгоритма, потока данных или простых булевых выражений.

На алгоритмическом уровне абстракции схема описывается в терминах последовательных операторов без привязки к тактовой частоте и деталей задержек преобразований. Временной аспект выводится из порядка операций в алгоритме. Некоторые инструменты синтеза допускают на входе такое представление, однако, требуют наличие конструкции типа «тактовая частота алгоритма» для синхронизации операций.

Основными компонентами цифровых систем являются регистры. На уровне абстракции потока данных описывается перемещение данных между регистрами схемы. Поэтому этот уровень часто называют уровнем регистровых передач (RTL-registertransferlevel). Это промежуточный уровень позволяет упростить рутинную работу с комбинационной логикой (отдать ее средствам синтеза) и сконцентрироваться на более полной спецификации регистров, как наиболее важной части схемы. В RTLописании присутствует точное задание тактовой частоты. Операции планируется выполнять в специфическом тактовом периоде, но не детализируются задержки внутри периода. Глобальная тактовая частота не является обязательным элементом, но может быть предпочтительной. Дополнительной особенностью может быть коррекция синхронизации, позволяющая перепланировать операции.

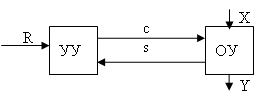

Для проектирования сложных цифровых устройств часто применяют модель программно-управляемого автомата (ПУА) [16]. ПУА состоит из устройства управления (УУ) и операционного устройства (ОУ), как показано на рис. 56.

Рис.56. Программно-управляемый автомат

Первое свойство этой модели гласит, что операционное устройство задается на уровне RTL, а устройство управления задается на алгоритмическом уровне (в частности конечным автоматом). Второе свойство утверждает, что ПУА является рекурсивной моделью. Это означает, что УУ может представлено в виде ПУА1 (ОУ1, УУ1), УУ1 в виде ПУА2 (ОУ2, УУ2) и так далее.

На ОУ определено множество микроопераций (МО), выполняющих преобразование входных сигналов X из окружающей среды в выходные сигналы Y для окружающей среды. Выполнение той или иной МО инициируется выходными сигналами c УУ, зависящими от состояния УУ, его входов R и s. Сигналы s характеризуют результаты выполнения операций в ОУ, а R – управляющие воздействия окружающей среды.

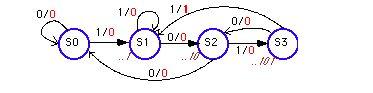

Рассмотрим пример описания для синтеза синхронного автомата Мили, реализующего детектор входной последовательности 1011 [21]. На рис. 57 представлена его диаграмма состояний, а ниже текст на VHDL.

Рис. 57. Диаграмма состояний детектора последовательности 1011,

реализующая автомат Мура

library

ieee; use

ieee.std_logic_1164.all; entity

detector1011 is

port (

CLK:

in STD_LOGIC; --синхросигнал

RST:

in

STD_LOGIC;

--сигнал инициализации

X:

in

STD_LOGIC;

--входной символ

Z:

out

STD_LOGIC

--выходной символ

);

end;

architecture

state_ machine of detector1011 is

type

Sreg0_type

is

(S1,

S2,

S3,

S4);

-- символическое кодирование состояний

автомата

signal

Sreg0:

Sreg0_type;

-- регистр состояний begin

--функция

переходов

автомата

Sreg0_machine: process (CLK)

begin

if

rising_edge(CLK)

then

-- синхронизация по фронту

тактового сигнала

if

RST='1'

then

-- синхронный сброс в

начальное состояние

Sreg0

<= S1;

else

case Sreg0 is

when

S1

=>

if

X='1'

then

--условие перехода из состояния

S1

в S2

Sreg0

<= S2;

end

if;

when S2 =>

if

X='1' then

Sreg0

<= S2;

else

Sreg0

<= S3;

end

if;

when S3 =>

if

X='1' then

Sreg0

<= S4;

else

Sreg0

<= S1;

end

if;

when S4 =>

if

X='0' then

Sreg0

<= S3;

else

Sreg0

<= S2;

end

if;

when

others =>

null;

end case;

end if;

end if; end

process;

Z_assignment:

--функция

выходов

автомата Z

<= '1' when (Sreg0 = S4 and X='1') else '0';

end

state_

machine;

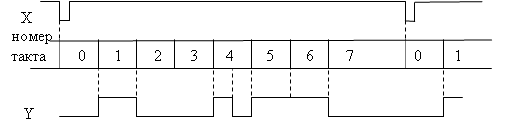

Разработка описание на VHDL ОУ базируется на задании временной диаграммы устройства. Пусть необходимо разработать синхронное устройство, на выходе Y которого формируется последовательность из трех импульсов в ответ на входной импульс X, как показано на рис.58 (выходные импульсы сопоставлены с тактами работы устройства).

Р

Рис.9.2

ис. 58. Пример задания на разработку

ОУ

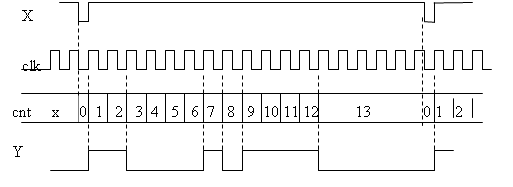

Возможны различные варианты реализации архитектуры. Рассмотрим первый вариант, основанный на организации механизма нумерации тактов. Для этого потребуется двоичный счетчик. В синхронных устройсвах изменение состояния элемента памяти может происходить либо только по фронту синхросигнала, либо только по его срезу. Потому изменения таких сигналов может происходить через минимальное время равное длительности периода тактового интервала. Для формирования полутактовых интервалов необходимо увеличить вдвое частоту тактового сигнала. На рис.59 приведена временная диаграмма работа устройства (ниже текст на VHDL). Сигнал cnt представляет четырехразрядный двоичный счетчик, изменяющий свое состояние по фронту синхросигнала clk. Длительность clk составляет половину длительности исходного такта.

Рис.59. Временная диаграмма первого варианта описания

library

ieee;

use ieee.std_logic_1164.all;

use ieee.

std_logic_unsigned.all;

entity example is

port(clk: in std_logic;

X:

in std_logic;

Y: out

std_logic

);

end; architecture

RTL1 of example is signal

cnt: std_logic_vector(3 downto 0); begin

operation1:

process

(clk)

--операция нумерации тактов от 0 до

13

begin

if

X=’0’

then

-- условие асинхронной

инициализации

cnt<=”0000”;

elsif

rising_edge(clk)

then

-- условие синхронной работы

if

cnt /=13 then

cnt<= cnt +1;

end if;

end if; end

process;

operation2:

process (clk) --формирование

Y

begin

if X=’0’ then

Y <=’0’;

elsif rising_edge(clk)

then

if (cnt=0) or (cnt=1) or

(cnt=6)

or (cnt=8) or

(cnt=9) or (cnt=10) or (cnt=11) then

Y <= ’1’;

else

Y <= ’0’;

end if;

end if; end

process; end

RTL1;

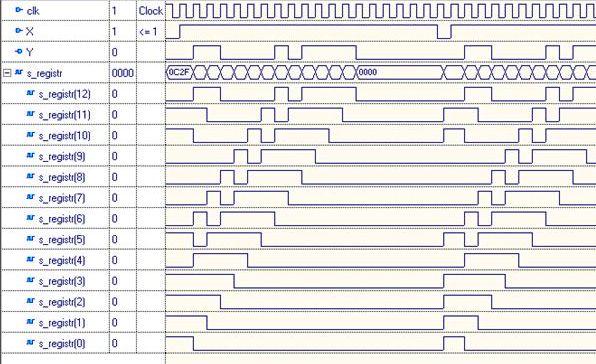

Второй вариант реализации архитектуры основан на сдвиговом регистре s_registr, выполняющем роль одноразрядной памяти магазинного типа. Эта память по сигналу Х запоминает по тактам временную диаграмму для сигнала Y, подключенного к старшему разряду s_registrt(11) (это реализует параллельный оператор присвоения Y <= s_registrt(11);), далее выполняется сдвиг s_registrt в сторону старших разрядов по фронту clk. На рис.60 приведена временная диаграмма работы этого варианта описания устройства, а ниже текст на VHDL.

Рис.60. Временная диаграмма второго варианта описания

architecture RTL2 of

example is signal

s_registr: std_logic_vector(11 downto 0); begin

Y <= s_registr(11);

shift: process (clk)

begin

if X =’0’ then

s_registr<=”110000101111”;

elsif rising_edge(clk)

then

s_registr (11

downto 1)<= s_registr(10 downto 0);

s_registr(0)<=’0’;

end if; end

process;

end

RTL2;

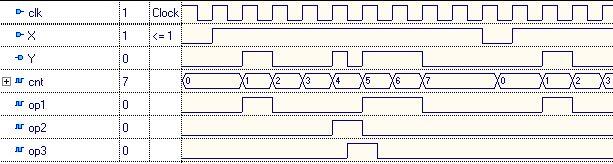

Третий вариант реализации архитектуры, в котором частота clk в два раза меньше чем в предыдущих двух вариантах. Для формирования полутактовых интервалов, поэтому потребовалось ввести три однобитных вспомогательных сигнала op1, op2, op3, разрядность cnt уменьшилась с четырех до трех разрядов. На рис.61 приведена временная диаграмма работы этого варианта описания устройства, а ниже текст на VHDL

Рис.61. Временная диаграмма третьего варианта описания

architecture

RTL3 of example is signal

cnt: std_logic_vector(2 downto 0); signal

op1, op2, op3: std_logic; begin

Y

<= op1 or (op2 xor op3); -- выражение

(op2 xor op3) формирует

полутактовый

--

импульс,

а

op1 все

остальные

control:

process (clk)

begin

if X =’0’ then

cnt<=”000”;

elsif rising_edge(clk)

then

if cnt /=7 then

cnt<= cnt +1;

end if;

end if;

end

process;

operation1: process (clk)

begin

if X =’0’ then

op1<=’0’;

elsif rising_edge(clk)

then

if (cnt=0) or (cnt=4) or

(cnt=5) then

op1<= ’1’;

else

op1<= ’0’;

end if;

end if;

end

process;

operation2: process (clk)

begin

if (X =’0’) or

(op3=’1’) then

op2<=’0’;

elsif rising_edge(clk)

then

if cnt=3 then

op2<= ’1’;

end if;

end if;

end

process;

operation3:

process (clk)

begin

if X =’0’ then

op3<=’0’;

elsif

falling_edge(clk) then

if cnt=4 then

op3<= ’1’;

else

op3<= ’0’;

end if;

end if; end

process; end RTL3;

Сравним эти три варианта описания с точки зрения аппаратных затрат и требований к быстродействию при реализации на FPGA. Последний вариант может быть реализован на более медленныхFPGA, т.к. требуется частота в два раза ниже остальных. Для первого варианта потребуется 5 триггеров, для второго 13, а для третьего 6. Описание второго варианта самое компактное, а у третьего самое громоздкое. Наличие вариантов реализации даже для простого устройства лишний раз подтверждает, что проектирование продолжает оставаться искусством.