- •Позвоночник компьютера

- •Вычислительная машина с одной шиной

- •Шина — это несколько проводников, соединяющих различные устройства. Шины можно разделить на категории

- •Типичная компьютерная организация с несколькими шинами

- •Все устройства, связанные с шиной, должны подчиняться правилам, чтобы платы, которые выпускаются сторонними

- •Шинная архитектура

- •Шины

- •Все связанные с шиной устройства при взаимодействии с ней должны придерживаться некоторого набора

- •В современном ПК довольно много шин периферийных устройств (USB, FireWare и др.), работающих

- •Зачем придумали шину

- •Одни устройства, связанные с шиной, являются активными и могут инициировать передачу информации по

- •Обычно сами устройства не могут давать достаточно интенсивного сигнала, поэтому они подключаются к

- •Устройство шин

- •Синхронизация шины

- •Пример

- •Ф – синхронизирующий сигнал, Aдрес – адресные линии,

- •Что лучше?

- •Арбитраж шины

- •Централизованный

- ••Скорость передачи данных по шине зависит от частоты шины и от ее разрядности.

- •http://library.krasu.ru/ft/ft/b72/0227142/pdf/6/13a.pdf

- •Общение программы с "внешним миром" на компьютере с общей шиной

- ••Центральный процессор может обмениваться с портами байтами или словами (в зависимости от вида

- •Программный вводвывод

- •Дальние подпрограммы. Макросы

- •Отладить программу, написать комментарии к командам, составить схему работы программы

- •Отладить программу, написать комментарии к командам, составить схему работы программы

- •Отладить программу, написать комментарии к командам, составить схему работы программы

- ••Главная задача компьютерной системы – выполнять программы. Программы вместе с данными, к которым

- •Память - совокупность отдельных устройств, которые запоминают, хранят, выдают информацию.

- •В некоторых запоминающих устройствах считывание данных сопровождается их разрушением. В этом случае цикл

- •Запоминающие устройства с произвольным доступом. Цикл обращения таких устройств не зависит от того,

- •Параллельность работы и иерархия памяти

- •Устройства хранения информации

- •Идея использования иерархичечской памяти

- ••Четыре верхних уровня иерархии образуют внутреннюю память ВМ, а все нижние уровни —

- ••На каждом уровне иерархии информация разбивается на блоки, выступающие в качестве наименьшей информационной

- •Параллельность работы. Идея

- •Буфер и Кэш

- •Основная память удовлетворяет запросы кэш- памяти и служит в качестве интерфейса ввода/вывода, поскольку

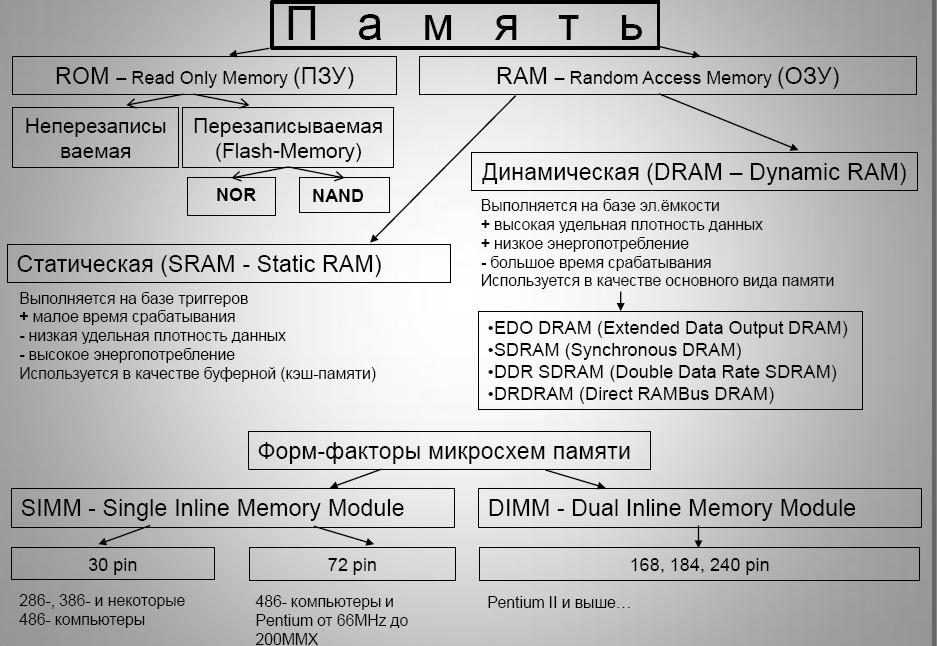

- ••Итак, напомним, что вся современная оперативная память относится к синхронной динамической памяти с

- ••На элементарном уровне запоминающая ячейка SDRAM-памяти, способная запомнить 1 бит информации, представляет собой

- •На системной плате и платах памяти их компоненты (DIP, SIMM, SIPP) организуются в

- •Концепция виртуальной памяти

- •Попробуем представить как будет храниться фраза “школа номер 495” в памяти.

- •Проблема

- •Ошибки

- •Допустим, что слово состоит из m бит данных, к которым мы добавляем r

- •Смысл интервала Хэмминга

- •Интервал Хэмминга полного кода

- •Смысл интервала Хэмминга полного кода

- •Примеры

- •Алгоритм для обнаружения и исправления одиночной ошибки

- •Значения нижнего предела

- •Метод Ричарда Хэмминга

- •Виртуальная память – воображаемая память, по объёму равная максимально адресуемой памяти.

- •Далее…

Идея использования иерархичечской памяти

•Пусть в среднем каждый байт вызывается N раз. Пусть время выборки из памяти

нижнего уровня – T, а из верхнего – t. Среднее время =t+T/N

t

T

•Четыре верхних уровня иерархии образуют внутреннюю память ВМ, а все нижние уровни — это внешняя или вторичная память. По мере движения вниз по иерархической структуре:

•1.Уменьшается соотношение «стоимость/бит».

•2.Возрастает емкость.

•3.Растет время доступа.

•4.Уменьшается частота обращения к памяти со стороны центрального процессора.

•Вывод: иерархическая организация памяти ведет к

уменьшению общей стоимости при заданном уровне производительности.

•На каждом уровне иерархии информация разбивается на блоки, выступающие в качестве наименьшей информационной единицы, пересылаемой между двумя соседними уровнями иерархии. Размер блоков может быть фиксированным либо переменным. При фиксированном размере блока емкость памяти обычно кратна его размеру. Размер блоков на каждом уровне иерархии чаще всего различен и увеличивается от верхних уровней к

•нижним.

•При доступе к командам и данным, например, для их считывания, сначала производится поиск в памяти верхнего уровня. Факт обнаружения нужной информации называют попаданием (hit), в противном случае говорят о промахе (miss). При промахе производится поиск в ЗУ следующего более низкого уровня, где также возможны попадание или промах. После обнаружении необходимой информации выполняется последовательная пересылка блока, содержащего искомую информацию, с нижних уровней на верхние. Следует отметить, что независимо от числа уровней иерархии

пересылка информации может осуществляться только между двумя соседними

уровнями.

•

Параллельность работы. Идея

•Параллельная работа разных уровней памяти, устройств ввода.вывода обеспечивается комплексом программных и аппаратных средств.

•Буфер – это запоминающее устройство небольшой ёмкости.(принцип FIFO)

•Контроллер – специализированный процессор.

Буфер и Кэш

•Эти термины не являются взаимоисключающими, и их функции часто смешиваются, но существует различие в их предназначении. Буфер — временное хранилище, где большие блоки данных сливаются или разбиваются на части. Это необходимо для взаимодействия с запоминающим устройством, которое работает с большими блоками данных, или когда данные передаются в другом порядке чем тот, в котором они формируются, и лишь желательно — в том случае, когда использование мелких блоков неэффективно. Использование буфера приносит пользу, даже если буферизуемые данные пишутся в буфер и читаются из него однократно.

•В свою очередь, использование Кэша предполагает, что данные будут читаться из кэша чаще, чем записываться туда. Его назначение — уменьшить число обращений к запоминающему устройству, а не сделать их более эффективными.

Основная память удовлетворяет запросы кэш- памяти и служит в качестве интерфейса ввода/вывода, поскольку является местом назначения для ввода и источником для вывода.

•Основная память современных компьютеров реализуется на микросхемах статических и

динамических ЗУПВ (Запоминающее Устройство

). Микросхемы статических ЗУПВ (СЗУПВ) имеют меньшее время доступа и не требуют циклов регенерации. Микросхемы динамических ЗУПВ (ДЗУПВ) характеризуются большей емкостью и меньшей

•Итак, напомним, что вся современная оперативная память относится к синхронной динамической памяти с произвольным доступом (Synchronous Dynamic Random Access Memory, SDRAM). Под синхронностью в данном случае понимают тот факт, что все управляющие сигналы и сами данные на шине памяти синхронизированы с некоторой опорной частотой (тактирующими импульсами). Динамической память является

втом смысле, что информация

вней сохраняется только при включенном питании, а кроме того, содержимое этой памяти (в отличие от статической памяти) необходимо периодически обновлять (производить регенерацию памяти).

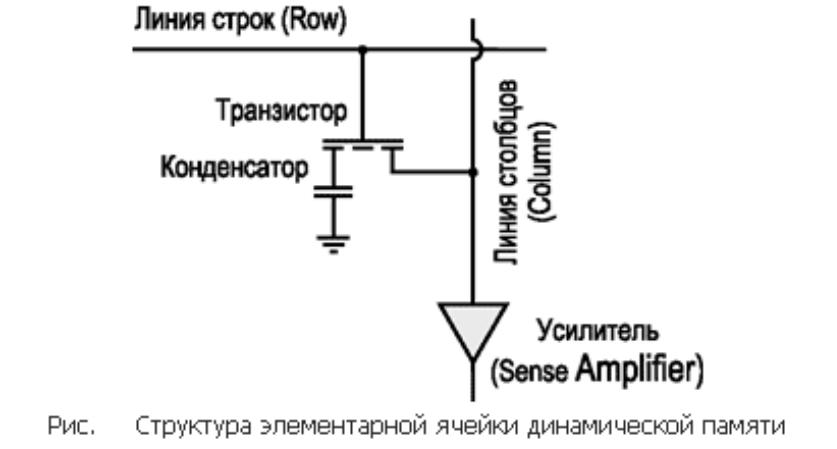

•Ядро микросхемы SDRAM- памяти принято рассматривать как некий двумерный массив (матрицу) ячеек памяти, находящихся на пересечении строк (Row) и столбцов (Column) (столбцы матрицы памяти также иногда называют страницами (Page)). По сути, ячейки памяти подсоединены к линиям строк и линиям столбцов

•На элементарном уровне запоминающая ячейка SDRAM-памяти, способная запомнить 1 бит информации, представляет собой конденсатор, который выполняет функцию хранителя заряда. Наличие заряда на конденсаторе можно ассоциировать с единичным битом информации, а его отсутствие — с нулевым битом.

•Однако одного лишь конденсатора недостаточно для формирования ячейки памяти. Дело в том, что если конденсатор соединить с линией строк и линией столбцов, то он мгновенно разрядится, то есть не сможет сохранять информацию. Поэтому в паре с конденсатором в элементарной ячейке памяти применяется транзистор, выполняющий функцию электронного ключа. Затвор транзистора (управляющий электрод) подключается к линии строк, а остальные два электрода (сток и исток) подключены к одной из обкладок конденсатора и линии столбцов. Если на затвор транзистора не подается напряжение, то транзистор находится в запертом состоянии и конденсатор физически отсоединен от линии столбцов.