V1 v2

OY(A-A) – наблюдаемость узла А в узле А = 1 (по определению);

OY(A-B) – -“ -“ -“ узла А в узле В,

OY(B-C) – В в С,

OY(A-C) – А в С .

OY(A-C) = OY(A-A) OY(A-B) OY(B-C) – свойство мультипликативности.

В общем виде:

OY(J-Q) = OY(J-J) OTF(J-Q) CY(cp.),

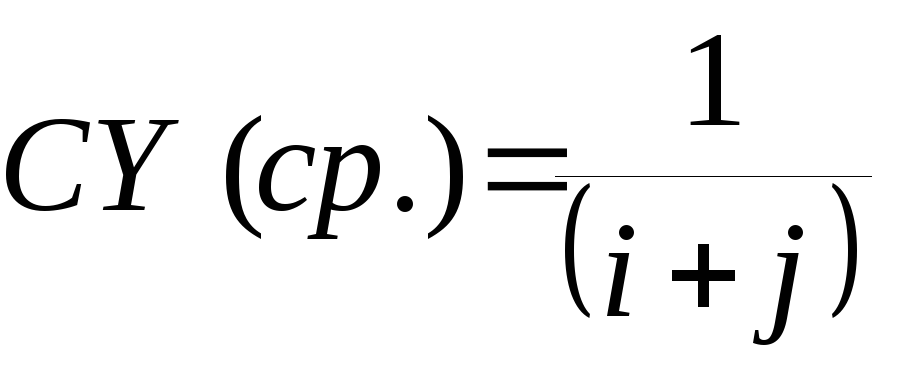

[(CY:

i асинхр.активизир-щих

входов)+ {(СY:

такт.

входов)

(СY:

j синхр.

aктивизир-х

входов)}].

[(CY:

i асинхр.активизир-щих

входов)+ {(СY:

такт.

входов)

(СY:

j синхр.

aктивизир-х

входов)}].

Так как наблюдаемость мультипликативна, ее не нужно вычислять для каждого узла.

Для предыдущего примера имеем:

OY(A-C) = OY(A-A) OY(A-B) OY(B-C),

что эквивалентно математически

OY(A-C) = OY(C-C) OY(B-C) OY(A-B),

Так как OY(A-A0 = OY(C-C) = 1.

Ветвление выхода.

В устройстве с ветвлениями можно наблюдать искомые состояния на первичных выходах. Рассмотрим пример:

V1 Пвых 1

Х

Х

V2

Пвых

2

V2

Пвых

2

В этой схеме состояние узла Х можно наблюдать на выходах 1 и 2. При активизации одного из возможных путей, состояние любого узла можно наблюдать на первичных выходах, что можно рассчитывать при помощи следующего выражения:

OY (составная ) = 1 - [1 – OY(каждого Пвых )]

Для нашего примера

OY(X – (Пвых1, Пвых2 )) = 1 – [1 – OY(X – Пвых1)] [1 – OY(X – Пвых2)].

Сходящиеся ветвления.

Путь 1 1 А

2 В путь 1 1

Путь 1 1 А

2 В путь 1 1

Х

Х

Х

4 Пвых 3

4 Пвых 3

2

2

3

С путь 2

Пвых

3

С путь 2

Пвых

путь 2

Для путей неравной длины нужно выбрать значение OY(X - Пвых), соответствующее кратчайшему путь от Х к Пвых (путь 2 для левого рисунка). Остальные пути блокируются, чтобы информация не сходилась.

Для путей равной длины вычисляется OY(X - Пвых), для обоих путей выбирается путь с наибольшим значением наблюдаемости, другие пути блокируются.

Схемы с цепями обратных связей.

Методика вычислений OY – как в схемах с ветвлениями неравной длины.

1 В

2 С 3 Пвых

1 В

2 С 3 Пвых

А

А

Последовательность вычислений:

OY(C - Пвых),

OY(B - Пвых),

OY(A - Пвых).

Здесь предполагается, что другой вход устройства 1 является управляемым.

Будет лучше, если в цепи обратной связи (ОС) есть устройства, которые увеличивают возможность блокирования распространения информации о неисправности по цепи обратной связи.

Вычисление тестопригодности.

TY(узла) = CY(узла) OY(узла)

TY(схемы) = (TY(узлов))/(число узлов)

Процедура вычислений TY.

Подготовить и проверить схемные соединения.

Вычислить управляемость CY узлов от Пвх через схему. Составить библиотеку значений CTF.

Вычислить наблюдаемость OY узлов от Пвх до Пвых. Составить библиотеку значений OTF.

Вычислить узловые TY.

Вычисление средних значений

и интерпретация результатов.

и интерпретация результатов.

Количественная оценка проектируемых схем.

Численные значения тестопригодности TY помогают сравнительному анализу тестопригодности узлов схемы. Приоритетны значения управляемости CY, затем – наблюдаемости OY.

Величину CY можно увеличить введением дополнительных непосредственно управляемых входов.

Величину OY можно повысить, если улучшить доступ к данной части схемы введением дополнительных контрольных точек.

Рекомендуется вводить соединения, позволяющие контролировать обратную связь, улучшить доступ ко входам или выходам внутренних элементов памяти. Перечисленные выше рекомендации можно проиллюстрировать при помощи следующего примера.

Преобразование структурной схемы для увеличения тестопригодности.

Рассматриваем структурную схему счетчика-делителя на 10.

3

3 3

3

3

3 3

3

x

4 15

x

4 x

4 x

4

x

4 15

x

4 x

4 x

4

C

lk

15

15 15 DIV 10

lk

15

15 15 DIV 10

x 1 U1

1 U2 1 U3 1 U4

x 1 U1

1 U2 1 U3 1 U4

16

16 16 16

16

16 16 16

2

2 2 2

2

2 2 2

V

CC

CC

1

1

12 U5 2

12 U5 2

13

13

Данная схема асинхронного счетчика-делителя на 10 постороена на микросхемах SN7476 (блоки U1 – U4) и логической схеме SN7410 (U5).

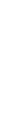

Расчеты показателей тестопригодности дали следующие результаты:

При этом минимальные и максимальные значения соответствующих параметров были получены в следующих узлах:

CYmax (Vcc) = 1, CYmin(U5.12) = 0.607,

OYmax(DIV10) = 1, OYmin(CLK) = 0.432,

TYmin(U5.12) = 0.36 .

Худшие показатели тестопнригодности связаны с цепью обратной связи, улучшить схему можно, реализуя следующие рекомендации:

Ввести соединения, позволяющие оборвать (управлять, наблюдать) любую обратную связь;

Улучшить доступ к входам или выходам внутренних элементов памяти;

Воспользуемся этими рекомендациями и модифицируем схему, для чего необходимы свободные контактные площадки:

Модифицированная схема :

U20

3

3 3 3

3

3 3 3

x

4 15

x

4 x

4 x

4

x

4 15

x

4 x

4 x

4

C

lk

15

15 15 DIV 10

lk

15

15 15 DIV 10

x 1 U1

1 U2 1 U3 1 U4

x 1 U1

1 U2 1 U3 1 U4

16

16 16 16

16

16 16 16

2

2 2 2

2

2 2 2

V

CC

CC

A

1

1

B

12 U5 2

12 U5 2

13

13

Теперь значения соответствующих параметров тестопригодности улучшились:

![]()

Генерация тестов.

Возможны два способа проведения тестирования: вручную или автоматически, при помощи ЭВМ.

а) при генерации тестов вручную можно

Начать с узла с минимальным значением CY;

Начать с узла с минимальным значением OY;

Начать с узла с максимальными значениями CY и OY.

Первые два варианта дадут тест, который автоматически покроет более простые неисправности. Последний вариант – самый простой, зато резкльтат будет получен сразу и возникает моральная поддержка при дальнейшем усложнении задачи.

б) при генерации тестов автоматически используются алгоритмы, в основе которых лежат D- алгоритм, алгоритм «активизированного пути» и т.п. программу генерации тестов можно улучшить на базе знаний параметров тестопригодности схемы либо модифицируя соответствующую программу с использованием изложенной выше компьютеризованной методики анализа тестопригодности (программа CAMELOT).

Реальная мера тестопригодности TY – это затраты на генерацию множества тестов для данной схемы. Рекомендации любой системы оценки тестопригодности позволяют улучшить структурную схему разрабатываемого устройства. Одновременно оцениваются аппаратные затраты при модификациях и стоимость создания дополнительных первичных входов и выходов (Пвх и Пвых), потери быстродействия при введении дополнительных шин и т.д. Результатом оптимизации экономических и функциональных факторов является разработка схемы, наиболее выгодной в проектировании и в эксплуатации.

МЕТОДЫ СТРУКТУРНОГО ПРОЕКТИРОВАНИЯ И САМОТЕСТИРОВАНИЯ.

Различают следующие виды структурного проектирования тестопригодных схем:

Сканирование.

Сканирование пути (scan path);

Сканирование с произвольным доступом (random access scanning);

Проектирование, чувствительное к уровню сканирования (level sensitive scan design).

II. Самотестирование методом сигнатурного анализа.

Сначала вкратце охарактеризуем самотестирование. Эта методика предполагает наличие встроенного поблочного диагностирования логических схем. Сигнатурный анализ (СА) - это метод самотестирования, основанный на использовании встроенного генератора тестовых наборов. Встроенные средства контроля - это коды обнаружения и исправления ошибки: проверки на четность, коды Хэмминга и т.п.

Наиболее распространенным методом структурного проектирования является сканирование, причем сканируемый путь – самый простой и наглядный. Главное условие применение такого метода – обязательное распределение схемы на комбинационную часть и элементы памяти, которые управляются синхросигналами (см. левый рисунок ниже).

СКАНИРУЕМЫЙ

ПУТЬ

y

Пвых

yПвых

Пвых

yПвых

оо х

У1

о У1

У1

о У1

х

о о

х У2 о х У2

х х

0

х Уn-1 о о х Уn-1

0

0

0

х

Уn

0

х

Уn

Пвх Пвх

М21

управление

сканированием

системный тактовый

импульс вход сканируемых

данных

системный

тактовый импульс

Примечание: соединения в схемах только в местах со значком (х), М21 - обозначение схемы мультиплексора «2 в 1»

Для обеспечения алгоритма сканируемого пути нужно обеспечить:

- отдельную проверку элементов памяти (ЭП),

- возможность установить внутренние переменные независимо от предыдущего состояния,

- выходные состояния комбинационной части схемы нужно непосредственно наблюдать, то есть установить определенные состояния на выходах ЭП.

Перечисленные условия можно реализовать, если преобразовать структурную схему, как показано на предыдущем рисунке слева. Последовательностная часть тестируемой схемы преобразуется в сдвиговый регистр при помощи поставленных схем мультиплексоров 21. Теперь можно осуществлять следующую последовательность тестирования:

Установить режим сканирования. Элементы памяти (ЭП) преобразуются в сдвиговый регистр. Проверить ЭП, использовать тесты

“бегущий «0»” или “бегущую «1»” от входа к выходу сканируемых данных

через ЭП,

тест проверки сдвигового регистра, проверка всех комбинаций переходов при подаче последовательности 00110011.

Определить множество тестов проверки комбинационной части схемы

при полном управлении всеми входами,

непосредственно наблюдая состояния всех выходов,

далее по процедуре расчета (оценки) тестопригодности.

Во избежание логических состязаний из-за различных времен задержки в активизированных путях рекомендуется использовать в качестве ЭП двухступенчатые M-S – триггеры.

Сканирование с произвольным доступом применяется в схемах со структурой ЗУПВ, так как нужны схемы дешифраторов для обеспечения произвольной выборки, а любой ЭП – это адресуемый триггер-защелка с раздельными входами «сброса» и «установки».

Сканирование, чувствительное к уровню сканирования – это развитие предыдущего типа сканирования с организацией ЭП накопителя в сдвиговые регистры на триггерах-защелках.

Недостатки методов сканирования:

Увеличение аппаратных затрат, введение дополнительных входов, выходов,

соединений.

Увеличение времени тестового диагностирования.

Невозможность тестирования на предельных рабочих частотах схемы.

Ограничение возможностей проектировщиков использованием определенных логических схем (правда, соединения выполняются творчески).

Достоинства методов сканирования:

Проверка достоверности работы и временной анализ схемы. Возможна автоматизация тестирования.

Генерация тестов нужна только для комбинационной части схемы.

Облегчается доступ к внутренним узлам схемы, улучшается поиск неисправностей.

Простота генерации тестов.

При сравнении нескольких вариантов проекта какого-либо устройства критерием, определяющим выбор варианта, служит стоимость тестирования.

Интересно и перспективно использовать методы структурного проектирования, сочетающие элементы сигнатурного анализа (СА) и методики сканирования. Такой подход называется поблочное диагностирование логических схем (BILBO = built - in logic block observation)

При проектировании схем с высокой тестопригодностью также полезно учесть некоторые советы, сформулированные в результате работы разработчиков ИС. Отметим, что эти советы полезны при проектировании не только полузаказных и не только интегральных схем.

ПРАКТИЧЕСКИЕ РЕКОМЕНДАЦИИ ПО ПРОЕКТИРОВАНИЮ

ТЕСТОПРИГОДНЫХ СХЕМ

Стремиться к максимальным значениям управляемости и наблюдаемости в схеме. Улучшать доступ к внутренним точкам схемы. Использовать мультиплексоры и демультиплексоры совместно со сдвиговыми регистрами.

Исключать логическую избыточность. Узел схемы логически избыточен, если все значения на выходе схемы не зависят от логического состояния узла на всех входных переборах и последовательности состояний. Логические состязания могут быть на основе необнаруженных неисправностей.

Физически разделять аналоговые и цифровые схемы: крутые фронты в ЦИС дают наводки в АИС.

Разбивать большие схемы на подсхемы для уменьшения затрат на генерацию тестов.

Имеем n микросхем. Затраты на 1) генерацию тестов пропорциональны n2, 2) затраты на моделирование неисправностей n3, для n = 100 без разбиения на блоки и с разбиением на блоки получим:

1) 1002 = 104, 1003 = 106,

2)

502+502

= 5103,

503+503

= 25104,

2)

502+502

= 5103,

503+503

= 25104,

экономия в 2 раза , в 4 раза.

Избегать пользоваться асинхронными логическими схемами. Асинхронные схемы обладают высоким быстродействием, т.к. оно определяется только их собственными задержками, но они труднее диагностируются.

Обеспечивать простоту начальной установки элементов памяти.

Обеспечить возможность разрыва цепей обратных связей. Особенно удачно будет, если удастся включать в ОС сигнал тестирования или его запрета:

Ucc

Сигнал

теста Ucc

сигнал

запрета

Сигнал

теста Ucc

сигнал

запрета

Избегать использовать одновибраторы, поскольку невозможно непосредственное наблюдение сигнала с выхода. Заодно возникает проблема быстодействия тестера.

Подключать нагрузку ко всем неиспользуемым входам и к выходам устройств с тремя состояниями и с открытыми коллекторами.

Избегать использования диагностически неразличимых групп элементов (проводное И, проводное ИЛИ) и узлов с большим числом ветвлений.

Разрывать длинные цепи на счетчиках.