ЛЕК+ЛАБА(СУМ) / Лаб / 15ЭУИС-л2+

.pdf

11

2.2.4. Варианты структурного решения БМК

Структурное решение БМК может быть полностью централизованным (см. рис. 2.5а), в котором все каналы ввода-вывода радиально подключаются непосредственно к МК или с децентрализацией (см. рис. 2.5б). Во втором случае некоторые внешние каналы подключаются к МК непосредственно, а большая их часть, как и различные структурные составляющие по рис.2.1, подключаются к МК через шины каналов бит-последовательной передачи данных.

Дискретные |

|

Дискретные каналы |

|

||

каналы |

|

|

|

|

|

|

|

Аналоговые каналы |

|

||

Аналоговые |

МК |

|

|

|

|

Шина приборного канала передачи |

|||||

каналы |

|||||

|

|

|

|

||

Канал |

|

|

|

|

|

передачи |

Каналы |

|

Каналы |

Каналы |

|

Дискретные |

Аналоговые |

Передачи |

|||

данных |

|||||

ввода- |

|

ввода- |

данных |

||

|

|

||||

|

вывода |

|

вывода |

|

|

МК |

Шина

внешнего

канал

передачи

данных

а) |

|

б) |

Рис.2.5. Варианты организации внешних связей МК

1)При проектировании прибора на основе БМК по структуре рис.2.5а ключевым решением является выбора МК с определенными техническими характеристиками. При этом, выбирая МК необходимо предусмотреть резервы по составу и количеству каналов вводавывода на тот случай, если в процессе разработки возникнут потребности развития дополнительных функций, непредвиденные при выборе МК.

Здесь возникает вопрос: а каковы же должны быть эти резервы с учетом того, что с одной стороны – они могут и не потребоваться, а с другой стороны – нет никакой гарантии в том, что предусмотренные резервы окажутся достаточными для решения задач непредвиденных потребностей. И надо учитывать, что в приборах, ориентированных на большие объемы производства, все излишества стркмятся минимизировать.

2)Вариант структуры БМК по рис.2.5б позволяет осуществлять выбор МК ориентируясь главным образом или исключительно на его процессорные возможности, а все задачи ввода-вывода решать с использованием дополнительных структур, подключаемых к приборному каналу передачи данных по мере и в пределах возникающих дополнительных потребностей

Преимущества варианта реализации БМК по рис. 2.5б состоят в следующем:

при выборе МК в большей мере можно руководствоваться его характеристиками как процессора и в меньшей – тем, какое в нем количество каналов ввода-вывода;

состав и количество каналов ввода-вывода определяется выбором структурных составляющих, которые подключаются к шине последовательной передачи сигналов с использованием минимального количества соединительных проводов: два − для электропитания и два (или 4) − информационных. Количество структурных составляющих всегда можно добавить, убавить или изменить;

«точки» ввода-вывода сигналов могут быть пространственно удалены от МК, т.к. количество линий связи с МК минимально;

структурные составляющие, через которые осуществляется ввод-вывод в МК различной информации, осуществляют предварительную обработку сигналов и, следовательно, разгружают МК от решения этой задачи.

12

2.3. Приборный канал (шина) передачи данных

В приборах последовательная передача сигналов может осуществляться по каналам интерфейсов: SPI или I2С.

SPI (Serial Peripheral Interface, SPI bus — последовательный периферийный интерфейс, шина SPI) — стандарт последовательный синхронный передачи данных в режиме полного дуплекса (т.е. возможности одновременной передачи сигнала в обоих направлениях). SPI разработан компанией Мotorola для обеспечения простого и недорогого сопряжении МК с рядом микросхем или блоков, поддерживающих этот интерфейс. Поскольку SPI является синхронным интерфейсом, то любая передача сигнала в нем синхронизирована общим тактовым сигналом, который должен генерироваться МК (см. рис. ниже).

Сигнал

информационный

Тактовый, синхронизация

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Принцип функционирования шины SPI: ведущий-ведомый. МК, как ведущее устройство, выбирает ведомое устройство для передачи данных: для чтения или записи информации. Остальные подключенные к шине микросхемы или блоки в передаче данных участия не принимают. Ведомое устройство (микросхема или блок) синхронизирует получение битовой последовательности принимаемым тактовым сигналом.

I2С– это интерфейс (шина) разработанный фирмой Philips для последовательной синхронной (см. рис. выше) передачи сигнала по шине передачи сигнала (полудуплекс) и по шине синхронизации. Интерфейс предназначен для осуществления эффективного межмикросхемного (IC– интегральная микросхема) взаимодействия. Отсюда и название шины: InterIC, IIC или окончательно – I2C или I2C. Дешевизна и простота реализации помогли I2C стать промышленным стандартом, универсальным средством построения модульной периферии, которая, во-первых, совместима между собой на уровне обмена данными, а во-вторых, подключается к материнской плате (или друг к другу), буквально, двумя проводниками (с учетом линий питания – четырьмя).

В настоящее время только фирма Philips производит более 150 наименований I2C-сов- местимых устройств (микросхем) различного назначения, предназначенных для работы в приборах и другом электронном оборудовании. Аналогичные устройства выпускаются и другими фирмами. Это обстоятельство определяет перспективу широкого и эффективного использования шины I2C при проектировании приборов.

2.3.1. Основные положения приборного интерфейса I2C

1) Схемная реализация шины I2C представлена на рис.2.6.

Передача сигналов в шине I2C осуществляется по линиям: SCL ─ передачи сигнала синхронизации, SDA ─ передачи информационного сигнала; ОП ─ общий провод.

Резисторы Rp предназначены для питания линий SCL и SDA, а их сопротивление может изменяться в диапазоне от 1,8кОм до 47кОм.

ОП

Рис.2.6. Схема интерфейса I2C

13

К линиям SCL и SDA относительно ОП подключаются структурные составляющие Device 1,…, Device 3 и так далее, со встроенным интерфейсом I2C и в пределах его адресной способности. Далее структурные составляющие ПМ, отвечающие требованиям интерфейса I2C, будем обозначать СС-I2C. Это могут быть как микросхемы, так и изделия разного уровня конструктивного исполнения IP.

2) СС-I2C могут иметь следующие функциональные назначения:

ведения часов и календаря для присвоения результатам измерений и событий метки времени (в общем случае: дата, время− часы, минуты, секунды, милисекнды), а также для поддержки архива данных;

увеличения емкости энергонезависимой памяти (EEPROM) до необходимого объема вне зависимости от емкости памяти выбранного МК;

увеличения количества портов ввода-вывода дискретных сигналов, расширяющих функциональные возможности портов ввода-вывода МК;

осуществление аналого-цифрового (АЦП) или цифро-аналогового (ЦАП) преобразований при использовании МК без каналов ввода и вывода аналоговых сигналов или для расширения возможностей выбранного МК;

визуализации данных при их выводе оператору (табло, дисплеи);

преобразователей интерфейса типа «I2C-RS232», позволяющих увеличить до необходимого количества возможность подключения устройств с интерфейсом типа RS232.

Магистральное подключение СС-I2C к шине I2C имеет конструктивные и технологические достоинства.

3) С конструкторской позиции применение СС-I2C при проектировании позволяет:

удешевить и ускорить процесс разработки прибора от функциональной схемы до опытного образца. Поскольку СС-I2C подключаются непосредственно к шине, то в макете или в опытном образце прибора некоторые СС-I2C могут быть изменены, добавлены или убраны без влияния на другие СС-I2C, подключенные к шине;

упростить разработку прибора благодаря тому, что в СС-I2C адресация и протокол передачи данных позволяют прибору быть полностью программно определяемым;

упростить диагностику сбоев и процесс отладка. Нарушения в работе могут быть немедленно отслежены.

сократить время разработки программного обеспечения благодаря использованию библиотеки повторно используемых программных модулей.

4)С позиции технологичности достоинства использования I2C состоят в следующем:

минимальное количество линий связи МК с СС-I2C: линия электропитания, линии связи SCL и SDA, общий провод;

обработка интерфейсных сигналов реализуется в микросхеме, поддерживающей интерфейс I2C, и устраняет необходимость в дешифраторах адреса и других микросхемах низкого уровня интеграции. В результате печатная плата становится меньше и дешевле;

I2C-совместимые микросхемы выпускаются в корпусах любого типа, что позволяет подобрать микросхему в нужном корпусе для установки на печатной плате, изготавливаемой по выбранной технологии.

2.3.2. Принципы функционирования шины I2C

1) Организация шины I2C.

В соответствии с рис. 2.6 к шине I2C подключаются СС-I2C. Передача сигналов осуществляется в соответствии с рис. 2.7: по линии SCL передаются синхроимпульсы, а по линии SDA передаются информационные сигналы.

14

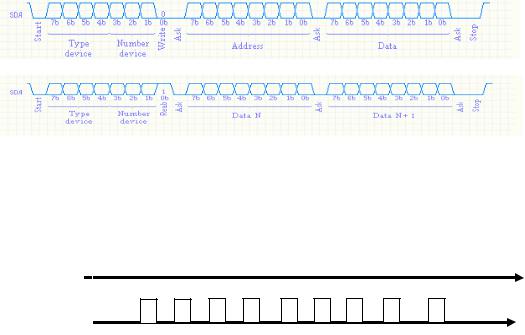

Рис. 2.7. Временная диаграмма протокола передачи данных

Синхронизационные сигналы в линии SCL всегда идут в одном направлении: от ведущего к ведомому. Такой режим передачи сигналов определяется как симплексный.

Информационные сигналы в линии SDA передаются в двух направлениях: от ведущего к ведомому и от ведомого к ведущему, но в каждое из направлений сигналы передается в разное время. Такой режим передачи сигналов по одной линии, но попеременно в разные направления, определяется как полудуплексный.

Скорость передачи сигналов в I2C определяется скоростью передачи сигнала синхронизации: в стандартном режиме передача сигналов синхронизации осуществляется со скоростью до 100 кбит/с, в "быстром" режиме ─ со скоростью до 400 кбит/с. Существует возможность передачи сигнала синхронизации со скоростью до 3.4MГц.

2) Принцип взаимодействия на шине I2C

Принцип взаимодействия устройств на шине I2C определяется как «ведущийведомый».

Ведущий (master) − это СС-I2C, которая управляет работой шины («захватывает» шину и владеет шиной). Ведущий инициирует передачу сигналов: формирует в линию SCL сигналы синхронизации, формирует в линию SDA информационные сигналы для адресуемого ведомого СС-I2C и поддерживает передачу от него ответных информационных сигналов.

Ведомый (slave) –это СС-I2C, которая принимает сигналы ведущего и формирует в SDA ответные сигналы по сигналам синхронизации в линии SCL.

Принцип «ведущий-ведомый» означает, что в каждый конкретный момент времени на шине может быть только один master. Остальные СС-I2C − slave. Особенностью интерфейса I2C является то, что каждая СС-I2C может стать master. Для этого инициативная СС-I2C должна «захватить» управление шиной. Если в одно и то же время управление шиной потребуется двум или более СС-I2C, то возникнет состязание за «захват» шины и сбой в работе ПМ.

3)Передача сигналов по шине I2C .

Винтерфейсе I2C все подключенные к шине активные СС-I2C должны состязаться за «захват» шины. То устройство, которое захватит шину, может передавать сигналы. Остальные будут ждать освобождения шины. Таким образом, в интерфейсе исключаются сбои изза одновременной передачи в линию связи сигналов несколькими активными устройствами.

Захват шины СС-I2C осуществляет посредством формирования сигналов start и stop.

В исходном состоянии (шина свободна) в линиях SDA и SCL устанавливается высокий уровень напряжения, а все СС-I2C контролируют уровень напряжения в линии SDA.

Рис. 2.8. Состояния start и stop

15

Процедура «захвата» шины начинается с того, что некоторая СС-I2C активизируется и формирует состояние start изменением уровня напряжения в SDA из «высокого» в «низкий» при сохранении «высокого» уровня напряжения в SCL (см. рис. 2.8, start condition). Это изменение уровня напряжения в линии SDA воспринимается всеми остальными СС-I2C как признак начала процедуры передачи сигнала и как то, что в шине уже есть ведущий и активность по захвату шины запрещается до окончания процедуры передачи сигнала.

Процедура передачи сигнала завершается тем, что ведущая СС-I2C формирует состояние stop, изменяя уровень напряжения в линии SDA с «низкого» на «высокий» при «высоком» уровне напряжения в линии SCL (см. рис.2.8, stop condition ).

Таким образом, состояния start и stop всегда вырабатывает master для реализации процедуры передачи сигнала: фиксация состояния start определяет «захват» шины, а фиксации состояния stop определяет «освобождение» шины.

Рассмотрим пример: пусть в БМК по I2C к МК подключены ССI2C: флэшпамять, АЦП и ввод дискретных сигналов от датчиков аварийных ситуаций. Первый ССI2C − всегда пассивен, а вот два других − активны. АЦП может быть активен после завершения программы измерений, а ввод дискретных сигналов должен передавать в МК информацию об аварийной ситуации так быстро, как это возможно.

Структура сигналов в линии SDA представлена на рис.2.9.

а) запись

б) чтение Рис. 2.9. Структура сигнала

Передача данных осуществляется байтами размером 8 бит плюс один бит – служебный, предназначенный для подтверждения приема байта. Рассмотрим это по рис.2.10 на примере первого байта, определяющего адресуемое СС-I2C.

SDA |

|

|

|

|

|

|

|

|

|

|

|

7b |

6b |

5b |

4b |

3b |

2b |

1b |

R/W |

ASK |

|

|

|

|

|

|

|

|

|

|

|

|

SCL |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

|

Рис. 2.10. Структура первого байта |

|

||||||

В первом байте передается информация о СС-I2C (идентификатор изделия), и о характере выполняемой операции.

Информация об изделии интерфейса I2C «зашита» в самом изделии так, что старшие биты 7b, 6b, 5b, 4b определяют тип устройства (например, − микросхема флэш-памяти), а следующие три бита 3b, 2b, 1b определяется номер устройства данного типа (например, − по номеру могут различать микросхемы по объем памяти).

Характер выполняемой операции передается последним битом (R/W): 0b = 0 − запись информации в ведомое СС-I2C, 0b = 1 − чтение информации из ведомого СС-I2C.

Например, пусть какая-то СС-I2C выпускается с прошивкой: 1100 000 (C0h). Следовательно, адресация с операцией записи данных в эту СС-I2C должна осуществляться байтом C0h, а операция чтения должна осуществляться байтом C1h.

После приема 8-ми бит приемник информации должен сформировать в линию SDA бит подтверждения − ASK (ответный бит). СС-I2C, передающая информацию, должна

16

контролировать уровень напряжения в линии SDA на 9-том синхроимпульсе в линии SCL. Сигнал ASK =1 передается низким уровнем напряжения и подтверждает прием байта; сигнал ASK=0 передается высоким уровнем напряжения и информирует о том, что не может принимать информацию.

Информация передается последовательностями байт из 8 бит. С начала посылается старший байт, а за ним младший. В байтах биты передаются в линию SDA начиная с MSB (Most Significant Bit)− Наибольшего Значащего Бита.

При выполнении операции «запись» (см. рис.2.9а) после байта, идентифицирующего определяющего само изделие (см. рис.2.10), передается адрес, по которому должна осуществляться «запись» информации, а затем до сигнала stop передается та информация, которая должна быть записана.

При выполнении операции «чтение» ведомая СС-I2C после приема адресуемого к ней сообщения начинает передачу запрошенной информации. Передача начинается с байта своего идентификатора по рис.2.10, а затем − побайтно осуществляется передача запрошенной информации до завершающего сигнала stop.

2.3.3. Примеры СС-I2C в микросхемном исполнении

1) Микросхема последовательного электрически стираемого ППЗУ (EEPROM), емкостью 64К x 8 (512 Кбит) предназначенная для работы в широком диапазоне напряжений питания (от 1.8 В до 5.5 В) и в широком диапазоне температур окружающей среды в рабочем состоянии: -40 °C до +125°С. Конструктивное исполнение устройства в пластиковом 8-вы- водном корпусе SOIC представлено на рис. 2.11:

Рис. 2.11. СС-I2C - EEPROM

Устройство способно к случайному и последовательному чтению вплоть до 512килобитной границы. Vcc и Vss − вводы питания. Вводы А1, А2, А3 − настраиваемый пользователем вы-бор микросхемы при подключении к шине до 8-и аналогичных микросхем памяти. Ввод WP можно подключить либо к Vss, либо к Vcc. Если он подключен к Vss, − разрешена нормаль-ная работа с памятью (чтение/запись всей память); если подключен к Vcc, то операции запи-си запрещены. На операции чтения это не влияет.

2) Микросхема часов реального времени (RTC) с календарем представлена на рис.2.12.

Рис. 5.12. СС-I2C - часы и календарь

Устройство имеют встроенную систему калибровки и систему автоматического переклюючения на резервный источник питания.

17

3) Микросхема маломощного 12-ти разрядного АЦП в компактном корпусе представлена на рис.2.13а: со встроенной схемой фиксации сигнала (T/H), со встроенными источником опорного напряжения, тактовым генератором и двухпроводным интерфейсом I2C. А на рис. 2.13б показан десятиразрядный цифровой индикатор.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

б) |

|

|

|

|

|

|

Рис.2.13. Примеры СС-I2C: АЦП и 10-ти разрядный индикатор