II Элементы последовательностной логики, триггеры

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от их последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательностной логикой. Основным элементом последовательностной логики является триггерный элемент памяти, или просто триггер.

9.5. Триггеры

Т риггер

— это

устройство с двумя устойчивыми состояниями

равновесия, предназначенное для записи

и хранения информации. Под действием

входных сигналов триггер может

переключаться из одного устойчивого

состояния в другое. При этом напряжение

на его выходе скачкообразно меняется.

Как правило, триггер имеет два выхода:

прямой Q

и инверсный Q.

Число входов зависит от выполняемых

функций. По способу записи информации

триггеры делят на асинхронные

и синхронизируемые

(тактируемые).

В асинхронных

триггерах информация может изменяться

в любой момент времени при изменении

входных сигналов. В синхронизируемых

триггерах информация на выходе может

меняться только в определенные моменты

времени, задаваемые дополнительным

синхронизирующим сигналом. Существует

большое число разнообразных триггеров

с различными функциональными возможностями.

Однако в основе всех схем лежит основной

(базовый) асинхронный RS-триггер.

риггер

— это

устройство с двумя устойчивыми состояниями

равновесия, предназначенное для записи

и хранения информации. Под действием

входных сигналов триггер может

переключаться из одного устойчивого

состояния в другое. При этом напряжение

на его выходе скачкообразно меняется.

Как правило, триггер имеет два выхода:

прямой Q

и инверсный Q.

Число входов зависит от выполняемых

функций. По способу записи информации

триггеры делят на асинхронные

и синхронизируемые

(тактируемые).

В асинхронных

триггерах информация может изменяться

в любой момент времени при изменении

входных сигналов. В синхронизируемых

триггерах информация на выходе может

меняться только в определенные моменты

времени, задаваемые дополнительным

синхронизирующим сигналом. Существует

большое число разнообразных триггеров

с различными функциональными возможностями.

Однако в основе всех схем лежит основной

(базовый) асинхронный RS-триггер.

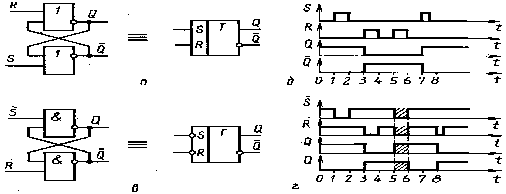

Асинхронный RS-триггер может быть построен на двух логических элементах ИЛИ—НЕ либо И—НЕ (рис. 9.7а,в). Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента. Триггер имеет два входа: S — вход установки в единичное состояние (от англ. set — установка) и R — вход сброса в нулевое состояние (от англ. reset—сброс). Как следует из схемы, данной на рисунке 9.7, а, при S=l и R=0 на выходах будет

![]()

а при S=0 и R=l имеем

![]()

После исчезновения входных сигналов, т. е: при S=R=0, сохраняется выходной сигнал, равный 1 или 0, в зависимости от того, на каком из входов (соответственно S или R) была перед этим единица. Все сказанное можно проследить и на диаграммах (рис. 9.7,б):

0 -й

такт. Входные

сигналы

R

и S

отсутствуют (равны

0). Триггер

в этот момент находился в единичном

состоянии (Q=l).

Необходимо четкое понимание того

обстоятельства, что в исходный момент

времени состояние триггера

— величина

случайная и мы только для определения

начинаем анализ с Q=l.

-й

такт. Входные

сигналы

R

и S

отсутствуют (равны

0). Триггер

в этот момент находился в единичном

состоянии (Q=l).

Необходимо четкое понимание того

обстоятельства, что в исходный момент

времени состояние триггера

— величина

случайная и мы только для определения

начинаем анализ с Q=l.

1-й такт. Входной сигнал S=1. Триггер принудительно устанавливается в единичное состояние, но так как Q уже равно 1, то состояние выходов триггера не меняется.

2

Рис. 9.7. Схемы и

временные диаграммы RS-триггера -й

такт. S=R=0.

Режим хранения информации, записанной

в предыдущем такте: Q=l,

Q=0.

-й

такт. S=R=0.

Режим хранения информации, записанной

в предыдущем такте: Q=l,

Q=0.

3 -й

такт. S=0,

R=1.

Триггер принудительно устанавливается

в нулевое состояние. При этом состояния

Q

и Q

меняются на противоположные.

-й

такт. S=0,

R=1.

Триггер принудительно устанавливается

в нулевое состояние. При этом состояния

Q

и Q

меняются на противоположные.

4

-й

такт. S=R=0.

Режим хранения.

-й

такт. S=R=0.

Режим хранения.

5-й такт. S=0, R=l. Принудительная установка в 0. Но так как Q уже равнялось 0, то состояние выходов триггера не меняется,

6-й такт. S=R=0. Режим хранения.

7-й такт. S=1, R=0. Принудительная установка в единичное состояние. На выходах триггера появляются сигналы Q=l и Q=0.

П

роведенный

анализ позволяет сделать вывод:

роведенный

анализ позволяет сделать вывод:

1) при S=1 и R=0 происходит установка триггера в устойчивое состояние с Q=l и Q=0 (запись единицы);

2) при R=1 и S=0 происходит установка триггера в устойчивое состояние с Q=0 и Q=l (запись нуля);

3) при S=R=0 триггер сохраняет то устойчивое состояние, которое имел до прихода этих сигналов (режим хранения).

Таким образом, состояние триггера (записанную информацию) можно определить или по сигналу на выходе Q, или по инверсии записанного сигнала на выходе Q. Однако при S=R=1 оба выходных сигнала

равны нулю, что не позволяет однозначно определить состояние системы. Поэтому комбинация входных сигналов S=R=1 является запрещенной.

Студентам предлагается самостоятельно провести подобный анализ для схемы RS-триггера на элементах И — НЕ (рис. 9.7,в) и убедиться, что вторая схема работает подобно первой при замене входных сигналов на инверсные с уровнями логических 0. На диаграммах (рис. 9.7,г) заштрихованными участками изображено время, в течение которого на входах RS-триггера действует запрещенная комбинация входных сигналов: R=S=0.

Описание работы RS-триггеров проводились аналитическим и графическим способами, однако это можно сделать и при помощи таблицы переключений (таблицы истинности RS-триггера) (табл. 9.3). Широкому использованию асинхронного RS-триггера в качестве самостоятельного устройства мешают присущие ему серьезные недостатки: наличие запрещенной комбинации входных сигналов, подача информации по двум отдельным цепям (R, S), низкая помехоустойчивость.

Таблица 9.3

|

|

Выход |

Режим работы | ||||

|

ИЛИ - НЕ |

И-НЕ |

Qt+1 |

Qt+1 | |||

|

|

R |

S |

R | |||

|

|

0 |

1 |

1 |

Qt |

Qt |

Хранение |

|

1 |

0 |

0 |

1 |

1 |

0 |

Запись 1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

Запись 0 |

|

1 |

1 |

0 |

0 |

X |

X |

З |

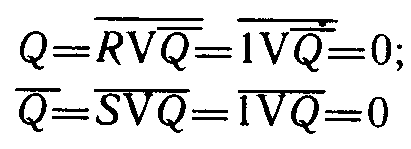

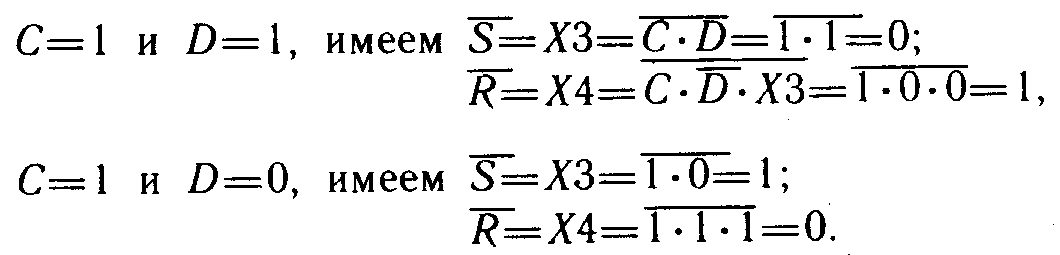

Синхронный D-триггер свободен от недостатков RS-триггера. D-триггер (рис. 9.8,а) образован из RS-триггера и входной комбинационной схемы на двух логических элементах. Сигналы, предназначенные для занесения в триггер, поступают на информационный вход D. На вход синхронизации С подают синхроимпульсы, определяющие момент записи информации. Описание работы триггера при различных комбинациях входных сигналов представлено в таблице 9.4.

Таблица 9.4

|

|

D |

CD =S |

CS =R |

Q |

Режим работы |

|

|

0 |

00=1 |

01=1 |

Предыдущее значение |

Хранение |

|

0 |

1 |

01=1 |

01=1 |

Предыдущее значение |

Хранение |

|

1 |

0 |

10=1 |

11=0 |

0 |

Запись 0 |

|

1 |

1 |

11=0 |

10=1 |

1 |

Запись 1 |

Из таблицы и временных диаграмм (рис. 9.8,в), иллюстрирующих описанный процесс хранения и записи информации, видно, что D-триггер находится в режиме хранения при С=0 и в режиме записи при С=1. Такой триггер задерживает выходной сигнал до окончания того такта, в который он был записан. Так, входной сигнал D=1 заканчивается между первым и вторым, четвертым и пятым синхроимпульсами, а состояние Q=l сохраняется до конца второго и пятого тактов. Отсюда произошло и название D-триггера (от англ. delay—задержка). Если сигнал на входе изменится во время действия синхроимпульса, то в триггере окажется записана та информация, которая присутствовала при окончании синхроимпульса,—момент t3 (рис. 9.8, в). Благодаря этому свойству (изменение информации в течение всего времени, пока С=1) рассмотренный триггер называется статическим синхронным D-триггером. Для нормальной работы статического D-триггера необходимо, чтобы изменение информации на D-входе происходило только при С=0.

В о

всех сериях интегральных схем имеются

D-триггеры.

Так, на рисунке

9.8,г

показаны условно-графическое обозначение

и цоколевка микросхемы К155ТМ7, включающей

четыре D-триггера.

Все триггеры имеют самостоятельные

информационные входы (выводы

2,3,6,7), однако

разрешение записи (входы С

— выводы

13 и

4) осуществляется

одновременно для двух триггеров, так

как в корпусе уже задействованы все

16 выводов.

Микросхема К561ТМЗ содержит четыре

самостоятельных триггера с общим

входом разрешения записи. Эта ИМС

интересна тем, что в зависимости от

уровня управляющего сигнала

V

запись осуществляется либо низким

(при V=0),

либо высоким (при V=l)

уровнем синхросигнала С.

Изменение уровня сигнала С

производится логическим элементом

2И—ИЛИ—2И (рис.

9.8, е).

о

всех сериях интегральных схем имеются

D-триггеры.

Так, на рисунке

9.8,г

показаны условно-графическое обозначение

и цоколевка микросхемы К155ТМ7, включающей

четыре D-триггера.

Все триггеры имеют самостоятельные

информационные входы (выводы

2,3,6,7), однако

разрешение записи (входы С

— выводы

13 и

4) осуществляется

одновременно для двух триггеров, так

как в корпусе уже задействованы все

16 выводов.

Микросхема К561ТМЗ содержит четыре

самостоятельных триггера с общим

входом разрешения записи. Эта ИМС

интересна тем, что в зависимости от

уровня управляющего сигнала

V

запись осуществляется либо низким

(при V=0),

либо высоким (при V=l)

уровнем синхросигнала С.

Изменение уровня сигнала С

производится логическим элементом

2И—ИЛИ—2И (рис.

9.8, е).

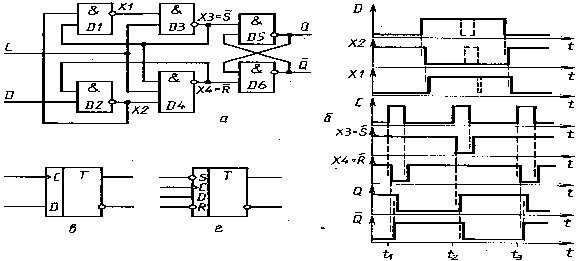

Динамический синхронный D-триггер исключает сквозную передачу сигнала с D-входа на выход триггера во время действия синхроимпульса. В триггере с динамическим управлением информация записывается только в момент перепада напряжения на входе синхронизации. Схема динамического D-триггера изображена на рисунке 9.9,а, а временная диаграмма для сигналов в различных точках триггера — на рисунке 9.9,б.

Р

ассмотрим

работу триггера, учитывая, что в каждый

момент времени значения выходных

сигналов логических элементов равны:X2=DX4,

X1=X2X3,

X3=CX1,

Х4=СХ2ХЗ.

Пока сигнал С

равен нулю, ХЗ=Х4=1.

Поэтому в паузах между синхроимпульсами

выходной триггер находится в режиме

хранения информации, а сигналы на выходах

первых двух элементов (D1,

D2)

полностью определяются входным

информационным сигналом: X2=Dl=D

и Xl=D1=D.

Сигналы Х2

и

XI

инверсные по отношению друг к другу,

поэтому при появлении С=1

только один из них разрешает прохождение

синхроимпульса через один из элементов

— D3

или D4:

ассмотрим

работу триггера, учитывая, что в каждый

момент времени значения выходных

сигналов логических элементов равны:X2=DX4,

X1=X2X3,

X3=CX1,

Х4=СХ2ХЗ.

Пока сигнал С

равен нулю, ХЗ=Х4=1.

Поэтому в паузах между синхроимпульсами

выходной триггер находится в режиме

хранения информации, а сигналы на выходах

первых двух элементов (D1,

D2)

полностью определяются входным

информационным сигналом: X2=Dl=D

и Xl=D1=D.

Сигналы Х2

и

XI

инверсные по отношению друг к другу,

поэтому при появлении С=1

только один из них разрешает прохождение

синхроимпульса через один из элементов

— D3

или D4:

Временные диаграммы (рис. 9.9,б) построены с учетом задержек распространения сигнала в каждом логическом элементе (показаны тонкими линиями). Пунктиром на диаграммах для D, X1 и Х2 показан случай, когда изменение информационного сигнала D происходит во время действия синхроимпульса. Анализ, который студентам предлагается провести самостоятельно, показывает, что этот сигнал проходит только на выходы первых элементов и не пропускается элементами D3 и D4.

Т аким

образом, в рассмотренном триггере с

динамическим управлением запись

сигнала производится по фронту

импульса синхронизации. Условное

графическое изображение динамического

триггера (рис.

9.9,в)

отличается от изображения

статического триггера (триггера с

потенциальным управлением) тем, что

динамический вход синхронизации

изображают на схеме треугольником.

Если вершина треугольника обращена в

сторону микросхемы, то триггер

срабатывает по переднему фронту

синхроимпульса, если от нее

— по

заднему фронту синхроимпульса.

аким

образом, в рассмотренном триггере с

динамическим управлением запись

сигнала производится по фронту

импульса синхронизации. Условное

графическое изображение динамического

триггера (рис.

9.9,в)

отличается от изображения

статического триггера (триггера с

потенциальным управлением) тем, что

динамический вход синхронизации

изображают на схеме треугольником.

Если вершина треугольника обращена в

сторону микросхемы, то триггер

срабатывает по переднему фронту

синхроимпульса, если от нее

— по

заднему фронту синхроимпульса.

В

Рис. 9.9. Схемы и

временные диаграммы динамического

D-триггера

Н

ебольшое

усложнение схемы (рис.

9.9,а)

позволяет получить универсальный

D-триггер

(рис.

9.9,г),

выполняющий функции как RS-триггера,

так и динамического D-триггера.

Модернизация заключается в замене

всех двухвходовых элементов И—НЕ

на трехвходовые элементы И—НЕ.

Появившиеся дополнительные входы

элементов D1

и D5

являются входами сигнала

S,

а входы элементов D2,

D3

и D6—

входами сигнала R.

Пока сигнал на S

и R

равен

1, универсальный

триггер работает как динамический

D-триггер

по входам D

и С.

Как только на один из входов (S

или R)

поступит сигнал, равный

0, так

триггер сразу перестает реагировать

на сигналы С

и

D,

и принимает

состояние, определяемое сигналом S

или

R.

Состояние S=R=0

по-прежнему считается запрещенным.

ебольшое

усложнение схемы (рис.

9.9,а)

позволяет получить универсальный

D-триггер

(рис.

9.9,г),

выполняющий функции как RS-триггера,

так и динамического D-триггера.

Модернизация заключается в замене

всех двухвходовых элементов И—НЕ

на трехвходовые элементы И—НЕ.

Появившиеся дополнительные входы

элементов D1

и D5

являются входами сигнала

S,

а входы элементов D2,

D3

и D6—

входами сигнала R.

Пока сигнал на S

и R

равен

1, универсальный

триггер работает как динамический

D-триггер

по входам D

и С.

Как только на один из входов (S

или R)

поступит сигнал, равный

0, так

триггер сразу перестает реагировать

на сигналы С

и

D,

и принимает

состояние, определяемое сигналом S

или

R.

Состояние S=R=0

по-прежнему считается запрещенным.

И

в ТТЛ и в КМДП сериях микросхем имеются

универсальныеD-триггеры.

Условные обозначения и цоколевка

некоторых из них показаны на рисунке

9.10. Микросхемы

К155ТМ2 и К.561ТМ2 содержат по два независимых

универсальных

D-триггера.

В микросхеме К155ТМ8 находится четыре

D-триггера

с общими для всех триггеров входами

динамической записи (С)

и сброса в нулевое состояние

(R).

в ТТЛ и в КМДП сериях микросхем имеются

универсальныеD-триггеры.

Условные обозначения и цоколевка

некоторых из них показаны на рисунке

9.10. Микросхемы

К155ТМ2 и К.561ТМ2 содержат по два независимых

универсальных

D-триггера.

В микросхеме К155ТМ8 находится четыре

D-триггера

с общими для всех триггеров входами

динамической записи (С)

и сброса в нулевое состояние

(R).

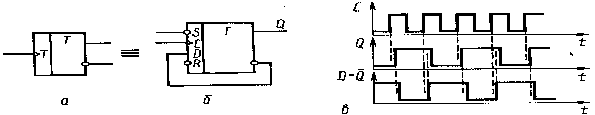

Счетный T-триггер имеет один управляющий вход и два выхода (рис. 9.11,а). Информация на выходах такого триггера меняется на противоположную при каждом положительном перепаде напряжения на счетном входе Т, поэтому счетный триггер используется в качестве делителя частоты входного сигнала. Триггер такого типа может быть создан из D-триггера с динамическим управлением, если его инверсный выход соединить с информационным входом (рис. 9.11,б). Если на выходе Q нулевой уровень, то на входе D в это же время уровень Q=l. По фронту первого синхроимпульса единица с D-входа перепишется (с опозданием, равным задержке одного логического элемента: рис. 9.11,в) на выход Q. Соответственно на выходе Q и входе D появится нулевой уровень (с опозданием, равным задержкам двух логических элементов). В следующем такте на выход Q будет переписано нулевое значение с входа D и т.д.

С

Рис. 9.11. Обозначение

и временная диаграмма работы T-триггера

оздать

счетный триггер на базе статического

D-триггера

таким же образом (обратной связью с

выхода Q

на вход D)

нельзя. Так как статический триггер

имеет потенциальное управление, то при

С=1 напряжение

на выходе за счет влияния обратной

связи будет постоянно меняться на

обратное, т. е. возникнут высокочастотные

колебания. Убедиться в этом можно,

построив временные диаграммы, подобные

изображенным на рисунке

9.8,в,

с учетом задержек сигналов в логических

элементах.

оздать

счетный триггер на базе статического

D-триггера

таким же образом (обратной связью с

выхода Q

на вход D)

нельзя. Так как статический триггер

имеет потенциальное управление, то при

С=1 напряжение

на выходе за счет влияния обратной

связи будет постоянно меняться на

обратное, т. е. возникнут высокочастотные

колебания. Убедиться в этом можно,

построив временные диаграммы, подобные

изображенным на рисунке

9.8,в,

с учетом задержек сигналов в логических

элементах.

Вход

Вход

S

S 0

0 апрещенный

(Q=Q)

апрещенный

(Q=Q)

C

C

0

0