- •Министерство образования и науки российской федерации

- •6.2. Применение сумматоров

- •6.3. Последовательные двоичные сумматоры

- •6.4. Арифметико-логические устройства (алу)

- •7. Схемы сравнения

- •7.1. Имс двоичных компараторов

- •7.2. Последовательные схемы сравнения

- •13. Умножители двоичных чисел

- •13.1. Матричные умножители

- •3.2. Последовательные умножители

- •2. Практическая часть

6.3. Последовательные двоичные сумматоры

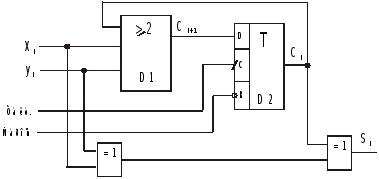

В последовательных сумматорах числа X и Y поступают в последовательном коде, начиная с младших разрядов. Функциональная схема последовательного сумматора представлена на рис. 74. Сумматор в каждом такте вычисляет значение суммы с учетом переноса из предыдущего такта сложения, т.е. в сумматоре должен запоминаться перенос Ci+1 в следующий разряд. Для этого в сумматоре используется D-триггер, который перед сложением должен обнуляться, т.к. C0= 0. Функции последовательного сумматора можно представить в виде: Ci+1 = xiyi + xiCi + yiCi = D (вход триггера); Si = xi Е yi Е Ci. Сумма Si также формируется в последовательном коде. Для реализации используется трех входовой мажоритарный элемент D1.

Сложность последовательных сумматоров не зависит от разрядности чисел xi, yi. Разрядность определяет время сложения, что является существенным недостатком. По приведенной функциональной схеме реализована ИМС последовательного сумматора ИМ7.

Рис. 74

6.4. Арифметико-логические устройства (алу)

АЛУ – это функционально законченное устройство, выполняющее определенный набор арифметических и логических операций над двумя многоразрядными числами. Набор операций определяется областью применения АЛУ. Стандартные АЛУ обычно выполняют полный набор логических функций двух переменных, арифметическое сложение и вычитание. Т.е. АЛУ включает в себя сумматор и набор комбинационных схем.

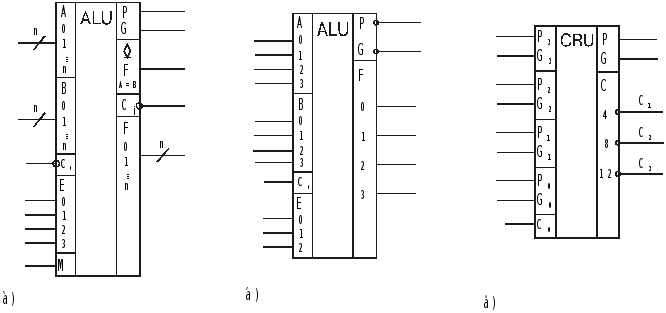

В виде отдельных ИМС выпускаются секции АЛУ – 2-х, 4-х, 8-и разрядные. Для обработки чисел с большей разрядностью осуществляется параллельное каскадирование отдельных секций. Для ускорения операций сложения в АЛУ используются схемы ускоренного переноса, для чего в каждой секции формируются вспомогательные функции Pi и Gi. На рис. 75,а представлено УГО АЛУ с полным набором функций. К таким АЛУ относится ИП3 – 4-х разрядная секция.

Рис. 75

Все АЛУ по выходам Fi и FA=B выполняют одинаковые арифметические и логические операции. Арифметические операции задаются значением сигнала М(Mode)=0, а логические М =1. Выбор одной из 16 логических или арифметических операций задается кодом Е(Е3Е2Е1Е0).

Таблицы функций конкретных АЛУ приводятся в справочниках.

Сигналы переносов С0, Ci, P и G используются для организации ускоренного переноса при каскадировании секции АЛУ. Кроме того С0 и Сi позволяют последовательно соединять отдельные секции.

Кроме универсальных АЛУ выпускаются АЛУ с сокращенным числом операций. К таким АЛУ относятся 4-х разрядные секции ИК2 (рис. 75, б). Данная АЛУ не имеет сигнала Ci, что допускает только параллельное наращивание секций с использованием сигналов P и G. В ИК2 отсутствует разделение функций на логические и арифметические. Для организации ускоренного переноса при объединении секции АЛУ используются специальные ИМС, например, ИП4 – устройство ускоренного переноса для четырех 4-х разрядных АЛУ (рис. 75, в).

7. Схемы сравнения

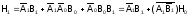

Для

сравнения операндов в цифровых системах

используются специальные схемы сравнения

– двоичные компараторы. Простейшая

схема для определения равенства двух

одноразрядных операндов А и В реализуется

логической операцией «Равнозначность»

.

На рис. 76,а представлена функциональная

схема реализующая функцию

.

На рис. 76,а представлена функциональная

схема реализующая функцию .

.

Рис. 76

Для определения равенства многоразрядных операндов выполняется логическое умножение, т.е. конъюнкция результатов сравнения отдельных разрядов:

Fn = F0F1...Fn-1.

Более сложными и широко используемыми являются схемы сравнения для определения неравенства операндов А и В, в которых реализуются функции:

;

;

.

.

Для

одноразрядных операндов A0

и B0

такие функции сравнения реализуются

на основе операции «Запрет»: F0=A0 ,

,

(рис. 76,б).

(рис. 76,б).

Для двухразрядных операндов А=А1А0 и В=В1В0 функции неравенства определяются следующими выражениями:

Аналогично можно записать функции сравнения для n-разрядных операндов.

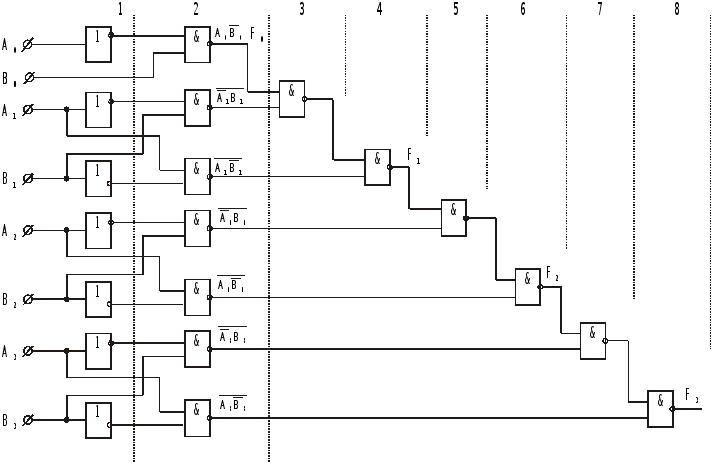

Операция сравнения производится последовательно начиная с младшего разряда. Реализация функции F иллюстрируется схемой сравнения двух 4-х разрядных операндов (рис. 77). Схема представляет собой двоичный компаратор с последовательной структурой. Общая задержка формирования сигнала F равна tF = 2ntз. Для 4-х разрядных операндов tF = 8ntз. Поэтому для разрядности больше, чем 4, такие схемы имеют низкое быстродействие и не используются.

Рис. 77

Для повышения быстродействия цифровых компараторов используют одновременное (параллельное) сравнение всех разрядов операндов в соответствии с вышеуказанными выражениями, в которых осуществляется подстановка функции F и H, выраженных через соотношения операндов.

В этом случае формирование сигнала сравнения F происходит с задержкой tF=4tЗ и не зависит от числа разрядов операндов. Однако в таких схемах требуются логические элементы умножения с числом входов n+1, реализация которых при n>8 затруднена. Вариант схемной реализации параллельного двоичного компаратора представлен на рис. 78.

Рис. 78

Приведенные варианты не являются единственными для построения схем сравнения двоичных чисел.