- •Министерство образования и науки российской федерации

- •6.2. Применение сумматоров

- •6.3. Последовательные двоичные сумматоры

- •6.4. Арифметико-логические устройства (алу)

- •7. Схемы сравнения

- •7.1. Имс двоичных компараторов

- •7.2. Последовательные схемы сравнения

- •13. Умножители двоичных чисел

- •13.1. Матричные умножители

- •3.2. Последовательные умножители

- •2. Практическая часть

7.1. Имс двоичных компараторов

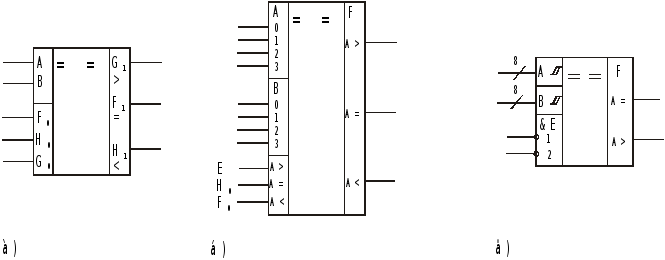

На рис. 79,а представлено УГО двоичного компаратора, реализующего по выходу полный набор функций сравнения. В качестве примера на рис. 79 приведены ИМС двоичных компараторов 555СП1 (б) и 74LS683 (в) с триггерами Шмитта на входах.

Рис. 79

В приведенных ИМС осуществляется параллельное сравнение, функции сравнения <, > , = программируются сигналами Е, Н0, F0.

Для реализации многоразрядных схем сравнения отдельные ИМС включаются последовательно (рис. 80).

Рис. 80

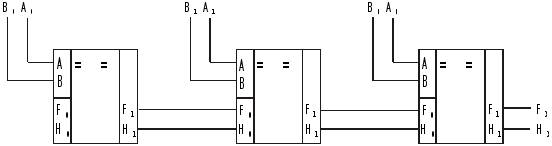

На рис. 81 приведена 12-разрядная схема сравнения на ИМС 561ИП2 при последовательном включении. Внешние сигналы H0,F0и Е устанавливают режим сравнения и выбирают выходные функции сравнения.

Рис. 81

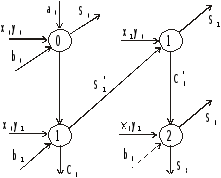

7.2. Последовательные схемы сравнения

Последовательные схемы сравнения удобны при представлении двоичных чисел в последовательном коде, а также требуют для реализации значительно меньше логических элементов. На рис. 82 представлена функциональная схема последовательного двоичного компаратора. Поскольку при сравнении получается три результата: G(A>B), H(A=B), F(A<B), то схема содержит два триггера, которые необходимы для хранения промежуточных значений функций сравнения. На выходах триггеров после поразрядного сравнения фиксируются результирующие значения функций. Данная схема не зависит от количества разрядов чисел А и В. Разрядность входных чисел определяет количество циклов сравнения, которое в свою очередь определяет время сравнения.

Рис. 82

13. Умножители двоичных чисел

Операция умножения требует значительных временных затрат, поэтому разработаны различные варианты схем умножения, обеспечивающие максимальное быстродействие. Высокое быстродействие имеют комбинационные схемы умножения. Простейший способ умножения двух n- и m-разрядных чисел описывается следующим алгоритмом:

,

,

Y – m-разрядный множитель,

Pj=X yj2j – частные произведения.

В качестве примера приведен процесс умножения двух чисел с разрядностью n = m = 4.

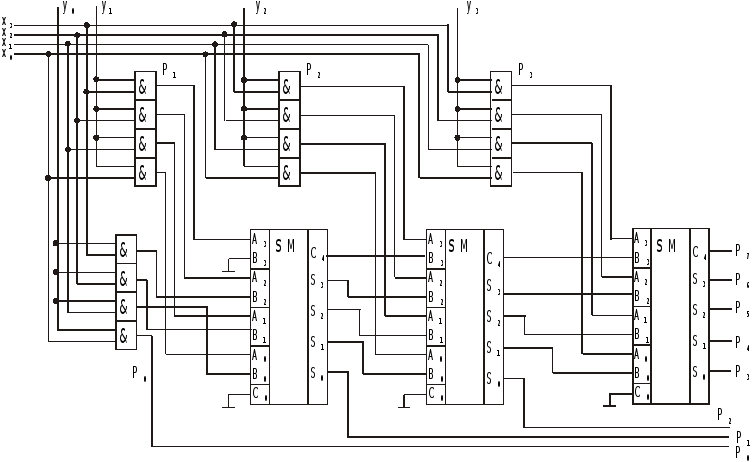

На рис. 83 приведена схема 4-х разрядного умножителя, реализованного по приведенному алгоритму с использованием ИМС полных сумматоров.

Рис. 83

13.1. Матричные умножители

Алгоритм матричного умножения можно записать в виде: XnґYm+An+Bm, где An и Bm – дополнения из младших разрядов при умножении. Максимальная разрядность результата умножения определяется выражением 2n+m -1 и определяется суммой разрядностей операндов.

Для 2-х разрядных чисел n = m = 2 можно записать алгоритм умножения в виде:

X2×Y2+A2+B2 = x1x0 ґy1y0+a1a0+b1b0 = x1y122 + (x1y0+x0y1+a1+b1)21 + (x0y0+a0+b0)20.

Такое вычисление можно реализовать с помощью четырех одноразрядных сумматоров типа ИМ1 (рис. 84).

Рис. 84

Операция умножения xi yi осуществляется логическими элементами «И», которые являются входными блоками сумматоров ИМ1. Сумма и перенос определяется выражениями:

Графически формирование произведения можно представить в виде:

Такая схема имеет регулярную структуру и может быть расширена до любых значений. Комбинационные схемы, имеющие такую функцию, называются матричными умножителями.

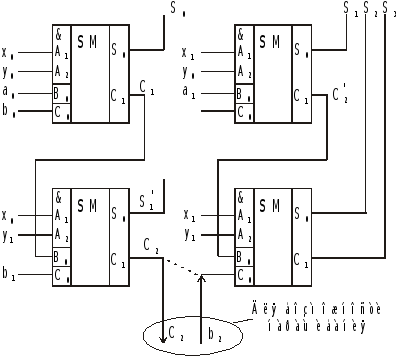

По данной схеме выполнена ИМС ИП5 – матричный умножитель 2ґ2. Условное обозначение MPL (Multiplier - умножитель) (рис. 85,а). Одноразрядные сумматоры в ИМС ИП5 реализованы по схеме на рис. 85,б.

Рис. 85

Существуют быстрые матричные умножители, использующие ускоренный алгоритм вычисления частичных произведений. Например: ИП8, ИК1 – быстрые умножители 4ґ2.

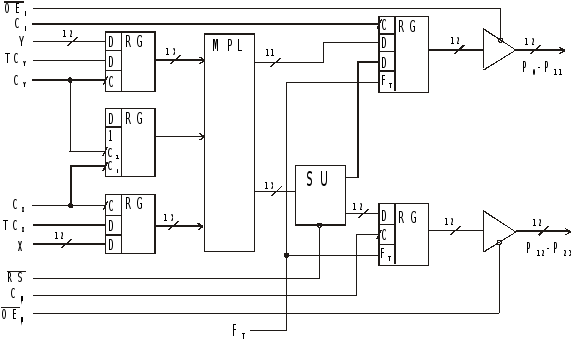

1802ВР4 – специализированная БИС умножения 12ґ12; tумн»100нсек, Pпот= 3Вт. Функциональная схема 1802ВР4 предсталвена на рис. 86.

Сигналы TCY, TCX указывают на дополнительный код умножаемых чисел.

CL и CM – (L – Least - младший, M – Most - старший) – тактовые сигналы записи младшей и старшей групп произведения.

SU – сдвигающее устройство.

Сигнал

(Right

Shift

– сдвиг вправо) указывает на присвоение

знака произведения младшей группе.

(Right

Shift

– сдвиг вправо) указывает на присвоение

знака произведения младшей группе.

Рис. 86.

FT – сигнал «прозрачности» регистров произведения.

По аналогичной структуре реализованы матричные умножители типа 1802ВР3 – 8х8 и 1802ВР5 – 16х16.

В настоящее время максимальную производительность обеспечивают умножители, реализованные на ПЗУ.