Введение

Рисунок 1.1

Классификация видов цифровых микросхем

Рисунок 1.1

Классификация видов цифровых микросхем

Рисунок 3.1

Условно-графическое изображение цифровых

микросхем.

Рисунок 3.1

Условно-графическое изображение цифровых

микросхем.

Рисунок 3.2

Уровни логических сигналов на выходе

цифровых ТТЛ микросхем

Рисунок 3.2

Уровни логических сигналов на выходе

цифровых ТТЛ микросхем

Рисунок 3.3

Уровни логических сигналов на входе

цифровых ТТЛ микросхем

Рисунок 3.3

Уровни логических сигналов на входе

цифровых ТТЛ микросхем

Рисунок 3.4.1

Путь протекания выходного тока единицы

цифровых микросхем

Рисунок 3.4.1

Путь протекания выходного тока единицы

цифровых микросхем

Рисунок 3.4.2

Путь протекания выходного тока нуля

цифровых микросхем

Рисунок 3.4.2

Путь протекания выходного тока нуля

цифровых микросхем

Рисунок 3.5

Определение длительности переднего и

заднего фронта выходного импульса

Рисунок 3.5

Определение длительности переднего и

заднего фронта выходного импульса

Рисунок 3.6

Определение времени задержки цифровой

микросхемы

Рисунок 3.6

Определение времени задержки цифровой

микросхемы

Таблица 3.1 Таблица истинности цифровой микросхемы

|

№ комбинации |

вх1 |

вх2 |

вх3 |

Вых1 |

Вых2 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

0 |

|

6 |

1 |

1 |

0 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

Раздел 2

Таблица 1.1 Таблица истинности логического инвертора

|

In |

Out |

|

0 |

1 |

|

1 |

0 |

Рисунок 1.1

Схема простейшего логического инвертора

Рисунок 1.1

Схема простейшего логического инвертора

Рисунок 2.

Условно-графическое изображение

логического инвертора

Рисунок 2.

Условно-графическое изображение

логического инвертора

Таблица 1.2 Таблица истинности схемы, выполняющей логическую функцию "2И"

|

In1 |

In2 |

Out |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Рисунок 1.2

Принципиальнае схема, реализующая

логическую функцию "2И"

Рисунок 1.2

Принципиальнае схема, реализующая

логическую функцию "2И"

Рисунок 1.3

Условно-графическое изображение схемы,

выполняющей логическую функцию "2И"

Рисунок 1.3

Условно-графическое изображение схемы,

выполняющей логическую функцию "2И"

Таблица 1.3 Таблица истинности схемы, выполняющей логическую функцию "3И"

|

In1 |

In2 |

In3 |

Out |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

Рисунок 1.4. Условно-графическое

изображение схемы,

выполняющей логическую функцию "3И"

Рисунок 1.4. Условно-графическое

изображение схемы,

выполняющей логическую функцию "3И"

Таблица 1.4. Таблица истинности схемы, выполняющей логическую функцию "2ИЛИ"

|

In1 |

In2 |

Out |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Рисунок 1.5.

Принципиальная схема, реализующая

логическую функцию "2ИЛИ"

Рисунок 1.5.

Принципиальная схема, реализующая

логическую функцию "2ИЛИ"

Рисунок 1.6.

Условно-графическое изображение

логического элемента, выполняющего

функцию "2ИЛИ"

Рисунок 1.6.

Условно-графическое изображение

логического элемента, выполняющего

функцию "2ИЛИ"

Рисунок 2.1.

Принципиальная схема базового логического

элемента "2И", выполненного на

диодах

Рисунок 2.1.

Принципиальная схема базового логического

элемента "2И", выполненного на

диодах

Рисунок 2.2

Принципиальная схема усовершенствованного

логического элемента "2И", выполненного

на диодах

Рисунок 2.2

Принципиальная схема усовершенствованного

логического элемента "2И", выполненного

на диодах

Рисунок 2.3.

Принципиальная схема базового логического

элемента ДТЛ микросхемы

Рисунок 2.3.

Принципиальная схема базового логического

элемента ДТЛ микросхемы

показано на рисунке 2.4, а таблица истинности приведена в таблице 2.1

Рисунок 2.4.

Условно-графическое изображение

логического элемента "2И-НЕ"

Рисунок 2.4.

Условно-графическое изображение

логического элемента "2И-НЕ"

Таблица 2.1. Таблица истинности схемы, реализующей логическую функцию "2И-НЕ"

|

x1 |

x2 |

F |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рисунок 2.5.

Принципиальная схема инвертора ДТЛ

микросхемы

Рисунок 2.5.

Принципиальная схема инвертора ДТЛ

микросхемы

Рисунок 2.6.

Принципиальная схема логического

элемента "2ИЛИ-НЕ" ДТЛ микросхемы

Рисунок 2.6.

Принципиальная схема логического

элемента "2ИЛИ-НЕ" ДТЛ микросхемы

Рисунок 2.7.

Условно-графическое изображение элемента

"2ИЛИ-НЕ".

Рисунок 2.7.

Условно-графическое изображение элемента

"2ИЛИ-НЕ".

Таблица 2.2. Таблица истинности схемы, выполняющей логическую функцию "2ИЛИ-НЕ"

|

x1 |

x2 |

F |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Рисунок 3.1.

Принципиальная схема базового логичиского

элемента ТТЛ микросхемы

Рисунок 3.1.

Принципиальная схема базового логичиского

элемента ТТЛ микросхемы

Рисунок 3.2. Условно-графическое

обозначение логического

элемента "2И-НЕ"

Рисунок 3.2. Условно-графическое

обозначение логического

элемента "2И-НЕ"

Таблица 3.1. Таблица истинности схемы, выполняющей логическую функцию "2И-НЕ"

|

x1 |

x2 |

F |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рисунок 3.3.

Принципиальная схема инвертора ТТЛ

микросхемы

Рисунок 3.3.

Принципиальная схема инвертора ТТЛ

микросхемы

Рисунок 3.4.

Принципиальная схема ТТЛ микросхемы

"2И-2ИЛИ-НЕ"

Рисунок 3.4.

Принципиальная схема ТТЛ микросхемы

"2И-2ИЛИ-НЕ"

Рисунок 3.5.

Условно-графическое обозначение

логического элемента "2И-2ИЛИ-НЕ"

ТТЛ микросхем

Рисунок 3.5.

Условно-графическое обозначение

логического элемента "2И-2ИЛИ-НЕ"

ТТЛ микросхем

Рисунок 3.6.

Уровни логических сигналов на выходе

цифровых ТТЛ микросхем

Рисунок 3.6.

Уровни логических сигналов на выходе

цифровых ТТЛ микросхем

Рисунок 3.7.

Уровни логических сигналов на входе

цифровых ТТЛ микросхем

Рисунок 3.7.

Уровни логических сигналов на входе

цифровых ТТЛ микросхем

Рисунок 4.1.

Принципиальная схема инвертора,

выполненного на комплементарных МОП

транзисторах (КМОП инвертор)

Рисунок 4.1.

Принципиальная схема инвертора,

выполненного на комплементарных МОП

транзисторах (КМОП инвертор)

Рисунок 4.2.

Зависимоть тока потребления КМОП

микросхемы от частоты

Рисунок 4.2.

Зависимоть тока потребления КМОП

микросхемы от частоты

Рисунок 4.3.

Принципиальная схема логического

элемента "2И-НЕ",

выполненного на комплементарных МОП

транзисторах (КМОП)

Рисунок 4.3.

Принципиальная схема логического

элемента "2И-НЕ",

выполненного на комплементарных МОП

транзисторах (КМОП)

Рисунок 4.4.

Условно-графическое изображение

логического элемента "2И-НЕ"

Рисунок 4.4.

Условно-графическое изображение

логического элемента "2И-НЕ"

Таблица 4.1. Таблица истинности МОП микросхемы, выполняющей логическую функцию "2И-НЕ"

|

x1 |

x2 |

F |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рисунок 4.5.

Принципиальная схема логического

элемента "2ИЛИ-НЕ", выполненного

на комплементарных МОП транзисторах

Рисунок 4.5.

Принципиальная схема логического

элемента "2ИЛИ-НЕ", выполненного

на комплементарных МОП транзисторах

Рисунок 4.6. Условно-графическое

изображение элемента

"2ИЛИ-НЕ"

Рисунок 4.6. Условно-графическое

изображение элемента

"2ИЛИ-НЕ"

Таблица 4.2. Таблица истинности МОП микросхемы, выполняющей логическую функцию "2ИЛИ-НЕ"

|

x1 |

x2 |

F |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Рисунок 4.7.

Полная принципиальная схема КМОП

инвертора

Рисунок 4.7.

Полная принципиальная схема КМОП

инвертора

Рисунок 4.8.

Уровни логических сигналов на выходе

цифровых КМОП микросхем

Рисунок 4.8.

Уровни логических сигналов на выходе

цифровых КМОП микросхем

Рисунок 4.9.

Уровни логических сигналов на входе

цифровых КМОП микросхем

Рисунок 4.9.

Уровни логических сигналов на входе

цифровых КМОП микросхем

Рисунок 5.1.

Эквивалентная схема протекания выходного

тока ТТЛ микросхемы

Рисунок 5.1.

Эквивалентная схема протекания выходного

тока ТТЛ микросхемы

Рисунок 5.2.

Логические уровни микросхем с пяти- и

трех вольтовым питанием

Рисунок 5.2.

Логические уровни микросхем с пяти- и

трех вольтовым питанием

Рисунок 5.3.

Выходные логические уровни 3- вольтовых

и входные уровни 2,5- вольтовых микросхем

Рисунок 5.3.

Выходные логические уровни 3- вольтовых

и входные уровни 2,5- вольтовых микросхем

Рисунок 5.4.

Выходные логические уровни 2,5- вольтовых

и входные уровни 3- вольтовых микросхем

Рисунок 5.4.

Выходные логические уровни 2,5- вольтовых

и входные уровни 3- вольтовых микросхем

Рисунок 6.1.

Пример сигнала на входе цифровой

микросхемы

Рисунок 6.1.

Пример сигнала на входе цифровой

микросхемы

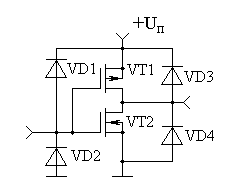

Рисунок 6.2.

Схема триггера Шмитта

Рисунок 6.2.

Схема триггера Шмитта

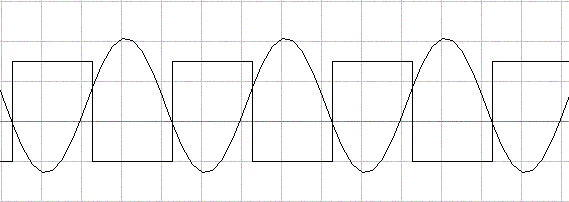

Рисунок 6.3.

Преобразование синусоидального сигнала

в логический при помощи триггера Шмитта

Рисунок 6.3.

Преобразование синусоидального сигнала

в логический при помощи триггера Шмитта

Рисунок 6.4.

Преобразование синусоидального сигнала

в логический при помощи компаратора.

Рисунок 6.4.

Преобразование синусоидального сигнала

в логический при помощи компаратора.

Рисунок 6.5.

Условно-графическое обозначение триггера

Шмитта

Рисунок 6.5.

Условно-графическое обозначение триггера

Шмитта