- •Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

- •Глава 1 структура вычислительной машины

- •1.1 Общее устройство

- •1.2 Корпус pc

- •Slimline

- •Desktop

- •Корпус типа атх

- •1.3 Материнская плата

- •Chipset

- •Rom bios

- •1.4 Процессор

- •Типы процессоров

- •Сопроцессор

- •Оперативная память

- •Контроллеры

- •1.5 Устройства хранения данных

- •Дисководы

- •Винчестеры

- •Глава 2 конфигурирование системы пэвм

- •Install, installhigh

- •Глава 3 устройства вывода данных

- •Глава 4 назначение и функции операционной системы

- •Глава 5 производительность компьютера. Способы ее измерения

- •Глава 6 сети эвм и средства телекоммуникационного доступа

- •Глава 7 устройства ввода данных

- •Лекция 1. Эволюция микрокомпьютеров.

- •2.1. Введение

- •2.2. Структура памяти

- •2.3. Сегментация памяти

- •2.4. Структура ввода-вывода

- •2.5. Регистры

- •2.6. Операнды и режимы адресации операндов

- •2.7. Замечания о режимах адресации

- •4. Назначение выводов мп

- •3. Программная модель микропроцессора

- •9 Интерфейсы ввода-вывода

- •9.1 Интерфейсы последовательной связи

- •9.2 Параллельная связь

- •9.5. Контроллрры прямого доступа к памяти

- •9.6. Контроллеры накопителей на гибких дисках

- •9.7. Интерфейс максимального режима и 16-битной шины

- •10. Полупроводниковая память

- •§ 10.5 Касается разнообразных видов пзу.

- •10.1. Общая организация памяти

- •10.2. Статические зупв

- •10.3. Динамические зупв

- •10.4. Резервное питание для полупроводниковой памяти

- •10.5. Постоянные запоминающие устройства

- •2) Компьютерные сети

- •2.1. Общие понятия

- •2.2.1. Топологии

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •-Звезда

- •2.2.2. Компоненты сети -Концентратор и коммутатор

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •2.3. Беспроводные сети

- •2.3.1. Radio-Ethernet

- •2.3.2. Gprs

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы для Ноутбуков, кпк и пк

- •Gprs модемы существуют в нескольких исполнениях:

- •Nokia d211

- •2.3.3. Bluetooth

9.2 Параллельная связь

Параллельная связь осуществляется одновременной передачей нескольких бит по отдельным линиям. Ее преимущество по сравнению с последовательной связью заключается в том, что для линий с заданной максимальной двоичной скоростью обеспечивается более высокая скорость передачи информации. Недрстажем же является, конечно, стоимость дополнительных пиний, и так как расходы увеличиваются с расстоянием, ' параллельная связь применяется на большие расстояния, если только требуется высокая скорость передачи данных.

В отличие от-лоследовательной связи четкие стандарты на параллельную связь отсутствуют. Параллеяьные передачи выполняются либо простым помещением данных в буферный регистр выходных данных интерфейса или восприятием данных из буферного регистра входных данных интерфейса, либо .ими управляют сигналы квитирования и (или) синхронизации. Обычно одновременно передается один символ <или другая единица информации) и необходимости определения конца символа или начала передачи не возникает. Четко определенный формат синхронной или асинхронной передачи отсутствует, но, если действия устройства и интерфейса координирует сигнал синхронизации, передача считается синхронной. Если же применяются только квитирующие сигналы, передача считается асинхронной.

Интерфейс можно спроектировать только на вывод, только на ввод, на ввод и вывод по отдельным наборам линий, или выполнять ввод-вывод по одному набору двунаправленных линий. Если интерфейс подключен к строчному принтеру, тдолжен только выводить данные, а если он обслуживает карточный считыватель, интерфейс должен телько-вводить данные. В интерфейсе, обслуживающем перфоленточные считыватель и перфоратор, потребуются один набор входных линий и один набор выходных линий, но в интерфейсе для устройства, которое не производит одновременные ввод и вывод данных, можно применить один набор двунаправленных линий. "ь

На рис. 9.20,а показан типичный выходной параллельный интерфейс, в котором отсутствуют линии управления. В этом случае содержимое буферного регистра данных постоянно выдается на линии данных, связывающие интерфейс и устройство вывода. Если устройство вывода состоит из регистра-защелки и управляемого им набора реле, компьютер может управлять этими реле, просто помещая данные в буферный регистр данных. На рис. 9.20,бизображен типичный параллельный интерфейс с линиями квитирования и отдельными подключениями к периферийному устройству для ввода и вывода. В этом случае при в'ВоДе данные сначала помещаются на шину данных, а затем на линии готовности входных данных устанавливается 1.Интерфейс должен отреагировать загрузкой данных в буфер входных данных и формированием 1на пинии подтверждения вход:

Рис. 9.20.Типичные интерфейсы параллельной связи:

а —только ввод;б —ввод-вывод

ных данных. При получении подтверждения устройство снимает сигналы данных и готовности. Когда интерфейс принял данные, он устанавливает бит состояния "готовность" и, возможно, посылает сигнал запроса прерывания. После того как процессор вводит данные, .гюерфьйх- сбрасывав iбит состоянияsготовность" и перевопит лина-и данных в высокоимгедансно! состояние. Ei-либыл „делан запрос прерывания, он обрабатывается обычным образом

При выводе интерфейс устанавливает бит состояния "го",овнос1ь' и, возможно, формирует запрос прерывания, когда буфер выходных данных освободился- После того как процессор выводит данные, интерфейс сбрасывает ^л \остояния 'готовность",помещает данные на шину выходных данных и сигналичируе'!у( тройству по линии готовности выходных данных. Когда >стройстзо готово воспринять данные, оно загружает их в регистр-защелку, а затем возвращает подтверждение. После этого интерфейс снимает сигнал готовности выходных данных и вновь устанавливает бит состояния "готовность".

Лекция Программируемый периферийный интерфейс

Примером параллельного интерфейса служит микросхема 8255А программируемого периферийного интерфейса. Как показано на рис. 9.21,она имеет регистр управления и три отдельно адресуемых порта А, 3и С. Обращение к 8255А определяет сигналCS, а направление обращения -сигналыRDиWR\ Адресуемый регистр определяют сигналы на входах А1 и АО. Следовательно, младший адрес порта, назначаемый 8255А, должен быть кратным 4.Полная адресация 8 25 5А содержится в табл 9.2

Таблица 9.2

Адресация микросхемы 8255А

Так как биты порта С иногда используются как биты управления, 8 25 5А спроектирован так, что в них можно выводить по отдельности, пользуясь командой установки/сброса. Когда 8255А принимает байт, направляемый в его регистр управления, он анализирует бит 7данных. Если этот бит содержит 1,данные передаются в регистр управления; если же бит 7=0,данные считаются командой установки/сброса и применяются для установки или сброса определяемого командой бита порта С, Биты 3-1дают номер изменяемого бита, а бит 0показывает сброс или установку. Остальные биты не используются.

Биты трех портов выведены на контакты, которые подключаются к устройству ввода-вывода. Они разделены на группы А и В, причем группу А образуют биты порта А и 4старших бита порта С, агруппу В -порт В и 4младших бита порта С. Группа А может работать в трех режимах (О, 1, 2),а группа В -в двух режимах (0и 1).Режимы определяются содержимым регистра управления, формат которого приведен на рис. 9.22.

Рис. 9.21.Схема интерфейса 8255А

Режим 0.В этом режиме группа разделяется на два набора. В группе А этими набора ми являются порт А и старшие 4бита порта С, а в группе В -порт В и младшие биты порта С. Каждый набор можно использовать для ввода или вывода, но не для двунаправленных передач. БитыD4,D3,D1 иDOв регистре управления определяют, какие наборы предназначены для ввода, а какие -для вывода. Эти биты ассоциируются с наборами следующим образом:

Рис. 9 22.Формат регистра управления микросхемы 8255А

D4iiopiA

D3старшая половина порта С,

D1 -порт В,

DO- младшая половина порта С

Если бит содержит 0,соответствующий набор применяется для вывода, а в противном случае для ввода

Режим 1.Когда в этом режиме работаем группа порт А используется для ввода или вывода в соответствии с битом D4 (D4 =- 1указывает ввод),dстаршая половина порта С применяется для сигналов квитирования и управления.

При вводе старшим битам пота С назначены следующие названия и определения-

РС4 STB^ -сигнал 0на этом контакте заставляет РА7-РАО "стробироваться" в порт А.

РС5 1ВРд —показывает, что входной буфер заполнен. Устанавливается в 1,когда порт А содержит данные, которые еще не введены в процессор. Когда действует сигнал 0,устройство может вводить в интерфейс новый байт.

РС6,РС7 -применяются для вывода сигналов управления в устройство или ввода состояния из устройства. Если бит D3в регистре управления содержит 0,эти линии выходные; в противном случае -входные. Привыводе:

РС4,РС5 -выполняют те же функции, что и РС6, РС7 при вводе.

РС7 ОВРд -показывает, что выходной буфер заполнен. Формирует сигнал 0в устройство, когда порт А выводит в устройство новые данные.

РС6 АСКд -устройство подает 0на этот вход, когда оно восприняло данные из порта А.

В режиме 1с группой А ассоциируется РСЗ, обозначаемыйINTRn. Этот сигнал применяется как линия запроса прерывания и подключается к одной из линийIRсистемной шины. При вводе в порт А на этом выходе формируется сигнал 1,когда новые данные помещаются в порт А (т. е. им управляет РС4),и сигнал 0,когда процессор считывает данные. При выводе на выходеINTRnформируется сигнал 1,когда содержимое порта А воспринято устройством, и сигнал 0,когда процессор загружает новые данные. Если группа В находится в режиме 1,порт В является входным или выходным в зависимости от состояния бита D1регистра управления (D1 = 1определяет порт В входным). При вводе РС2 и РС1 обозначаютсяSTBoиIBFg; они выполняют для группы В те же функции, что и сигналыSTBnи 1ВРд для группы А. Аналогично при выводе РС1 и РС2 обозначаютсяOBFgи АСК„. Выход РСО превращается вINTRgи используется аналогично'INTR^. Разрешением прерываний для группы А управляют РС4 в режиме ввода и РС6 в режиме вывода. Например, в режиме ввода прерывание для группы А разрешается установкой РС4 и запрещается сбросом РС4 с помощью команды установки/сброса. Аналогично разрешением прерываний для группы В управляет установка/сброс РС2.

Режим 2.В данном режиме может работать только группа А, хотя в ней для генерирования запросов прерываний используется РСЗ. В режиме 2порт А становится двунаправленным, а 4старших бита порта С определяются следующим образом:

<РС4STB*-сигнал 0на этой линии заставляет данные с РА7-РАО стробироваться в порт А.

РС5 1ВРд -формируется сигнал 1,когда в порт А загружаются новые данные1с линий РА7-РАО, и сигнал 0,когда процессор считывает данные. РС6 АСКд -показывает, что устройство готово воспринимать данные с линий;РА7-РАО.

w "iJbtд формирует сигнал , »i^i,р >це (.ор 3iiр) лш. в иор1 А ио^sданные., и с й''налd, когда данные принягы устройством.

Когда гpyппа А находится в режиме 2,группа В может работать вpeжиме О или 1если группа В находится в режима 0только РС2 РГО можно использовать для ввода или вывода, ».>к к» к Р*'3лужи! запросом прерываний л^>iр^ппы \ Обычноeiто птшApd6oi4tiз режиме \ РС2 РГО по гклю »йе1ся к контактам управления и <остояния 'ipo^tiai. коюр<\>ik/. соединено к ;'я:иямfitрта А Дляэт.^лже целей мижч тоимеьять "я порт В

Во всех тех режимах порт С отражает сигналы на линиях РС7-РСО и его можно считать командой WR.

9 2.2Пример использования

На рис. 9.23показано возможное подключение микросхемы 8255А к аналого-цифровой и цифро-аналоговой подсистемам. Так во время аналого-цифрового преобразования аналоговое напряжение должно оставаться неизменным, необходима схема выборки i-го сохранения. Группа А работаетнаввод в режиме 1.Преобразование инициируется сигналом на выходе РС7, это стимулирует преобразователь выдать сигнал занятости. Линия занятости подключена на .вход управления выборкой и сохранением (S/H) я на вход одновибратора, запускаемого спадающим фронтом. Пока сигнал занятости имеет высокий уровень, схема выборки и сохранения поддерживает постоянный выход, а когда в конце преобразования сигнал занятости снимается, запускается одновибратор. Его выход инвертируется и подается на вход 8ТВд (РС4) микросхемы 8255А. Он заставляет цифровой отсчет стробироваться в порт А. В цифро-аналоговой части подсистемы порт В работает как выходной в режиме 0;он подключен непосредственно на двоичный вход цифро-аналогового преобразователя. Квитирование здесь не применяется.

Предположим, что порты А, В и С и регистр управления имеют адреса FFF8,IFF9FFFAиFFFB. Тогда команды

MOV AL.10110000В OUT DX,AL

заставляют порт А работать в режиме 1,порт В -в режиме 0,а РС7 быть выходом. Следующий фрагмент формирует импульс на входе запуска аналого-цифрового преобразователя.

MOV DX,OFFFBH

MOV AL,00001111B

OUT DX,AL

MOV AL,00001110B

OUT DX,AL

Здесь первая команда загружает в регистр DXадрес, ассоциируемый с командой установки/сброса, которыйcoвпадает с адресом регистра управления Следующие две команды формируют сигнал Ю -=• 1,а последние две ~ сигнал РС7 = 0.Фрагмент программного ввода преобразованных данных имеет вид

MOV DX.OFFFAH AGAIN: IN AL,DX

TEST A L.,001 OOOOOB JZ AGAIN MOV DX.OFFF8H IN AL,DX

Рис. 9.23.Интерфейс аналого-цифровой и цифро-аналоговой подсистем с применением микросхемы 8255А

Для вывода байта из регистра ALв цифро-аналоговый преобразователь требуются только две команды.

MOV DX.OFFF9H

OUT DX,AL

Как только байт появляется в порту В, его биты сразу подаются на входы цифро-аналогового преобразователя, который в свою очередь сразу же преобразует их в аналоговый сигнал.

В данном примере предполагается, что синхронизация преобразований осуществляется программой и что коэффициенты усиления входного и выходного аналоговых усилителей регулируются. Чтобы получить от программы равномерное распределение входных и выходных отсчетов, необходимо учитывать времена выполнения команд. Между

MOV CX,N IDLE NOP

LOOP IDLE

между вводами или выводами. Схема ввода с программной синхронизацией отсчетов аналого-цифрового преобразования представлена на рис. 9.24

Часто в аналого-цифровой и цифро-аналоговой подсистеме применяются программируемые генераторы синхронизации и усилители, что позволяет более точно управлять расположением отсчетов и цифро-аналоговых выходов, а также динамически изменять усиление Кроме того, в такую подсистему часто вводят контроллер ПДП для увеличения скорости ввода и вывода.

На рис 9.23показаны только 8-битные преобразователи, имеющие разрешающую способность 1из256.Если диапазон входного или выходного напряжений равен -10 . . . +10В, разрешающая способность составляет

20/256=0,078В.

Для улучшения разрешающей способности применяются 10-, 12-или 14-битные преобразователи. В этом случае приходится пользоваться комбинацией портов А и С или В и С (см упр. 14)или параллельно включать две микросхемы 8255А (см. § 9.7).

Лекция ПРОГРАММИРУЕМЫЕ ТАЙМЕРЫ И СЧЕТЧИКИ СОБЫТИЙ .

Довольно часто требуется устройство формирования временных интервалов для процессора и внешних устройств, подсчета внешних событий и ввода показаний в процессор, а также генерирования внешней синхронизации, которую может программировать процессор. Такое устройство называется программируемым интервальным таймером/счетчиком событий.Некоторыми областями применение такого устройства являются:

прерывание операционной системы с разделением времени через равномерные интервалы, чтобы она осуществляла переключение программ;

вывод точных временных сигналов с программируемыми периодами в устройство ввода-вывода (например, в аналого-цифровой преобразователь);

программируемая генерация скорости передачи в бодах;

измерение временной задержки между внешними событиями;

подсчет числа появлений событий во внешнем эксперименте и ввод показания в компьютер;

Рис. 9.25.Типичный интервальный таймер/счетчик событий

прерывание процессора после появления запрограммированного числа внешних событий.

Типичная организация интервального таймера/счетчика событий показана на рис. 9.25. Слева находятся четыре доступных компьютеру регистра: два верхних являются выходними портами, а два нижних - входными. Сам счетчик прямо процессору не доступен, но может инициализироваться из регистра начального счета и считывается посредством передачи его содержимого в выходной регистр счетчика. Счетчик запускается с начального значения и отсчитывает до 0. Вход CLK определяет скорость счета, сигнал GATE разрешает и запрещает вход CLK и, возможно, выполняет другие функции, а выход OUT-становится активным при достижении счетчиком 0 или, возможно, при подаче сиг-нала АТЕ. Выход OUT подключается к линии запроса прерывания в системной шине, поэтому прерывание возникает при достижении счетчиком 0; его же можно подключить к устройству ввода-вывода для инициирования необходимых действий.

Устройство вводит значение в регистр начального счета, передает его в счетчик и выполняет счет "назад" (т. е. вычитание) импульсами со входа CLK. Текущее содержимое счетчика в любой момент можно ввести в процессор, не нарушая работы счетчика, посредством передачи его в выходной регистр счетчика с последующим считыванием из этого -регистра. При буферировании содержимого счетчика не требуется вводить его в процессор немедленно. Индикация нуля в счетчике обычно фиксируется на выходе OUT и в одном бите' регистра состояния. Поэтому для обнаружения нуля допускается применять Программный ввод-вывод и ввод-вывод по прерываниям.

Регистр управления определяет режим работы и выполняет другие функции. Режим точно определяет, что происходит при достижении счетчиком 0 и (или) при подаче сигнала на вход GATE. Возможными действиями являются:

вход GATE применяется для разрешения и запрещения входа CLK;

вход GATE вызывает реинициализацию счетчика;

[ i. вход GATE прекращает счет и формирует высокий уровень на выходе OUT;

- при достижении 0 счетчик выдает сигнал OUT и останавливается;

при достижении 0счетчик выдает сигналOUTи автоматически реинициализируется из регистра начального счета.

Режимы могут также определяться комбинациями перечисленных возможностей Рассмотрим, например, применение интервального таймера в операционной системе разделением времени. В этом случае на вход CLKподаются сигналы синхронизации, ) выходOUTподключается к линии запроса прерывания, возможно, немаскируемой прерывания. ВходGATEздесь не требуется. При включении системы в регистр начальщ го счета загружается значение

начальный счет ==частота синхронизации Х Т,

где Т -продолжительность каждого временного кванта в секундах. Задается такой режим, что при достижении счетчиком 0содержимое регистра начального счета вновь загружается в счетчик, а выходOUTстановится активным. Поскольку сигналOUTиспользуется как запрос прерывания, процедура прерывания для переключения программ будет выполняться с интервалом Т секунд.

9.3.1Программируемый интервальный таймер

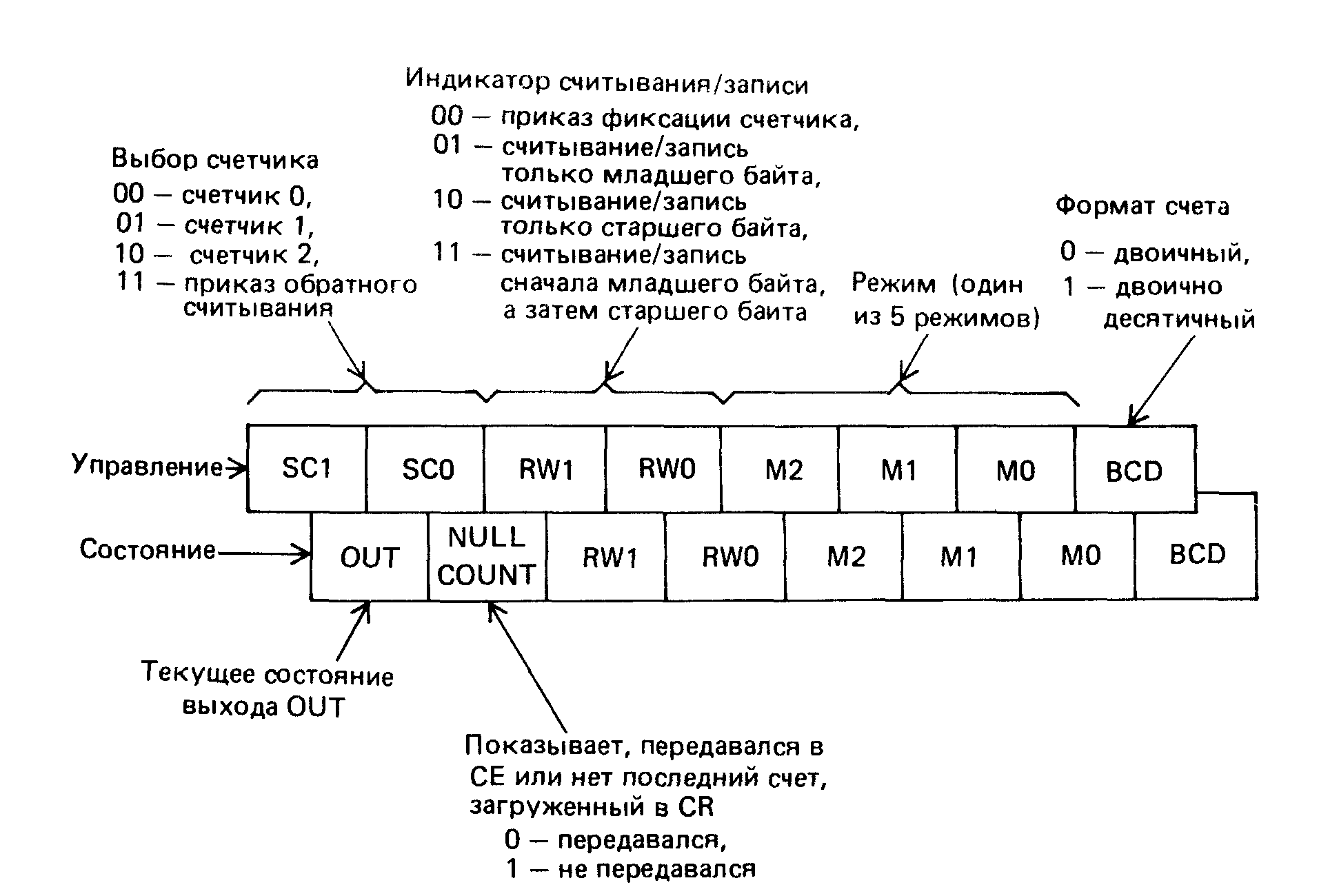

На рис. 9.26представлена схема интервального таймера/счетчика событий 8254фирмыIntel. В нем имеются три одинаковые счетные схемы со своими входами CLKиGATEи выходомOUT. Каждая схема имеет регистр управления и состояния, регистр счетчика (CR) для приема начального счета, счетного элемента (СЕ) ,который выполняет счет, но непосредственно процессору недоступен, и выходного регистра-защелки (OL) для фиксации содержимого СЕ, так что его может считать процессор. Полагается, что CR,СЕ и OLпредставляют собой пары 8-битных регистров. (Реальные схемы несколько отличаются от приведенных, но для программиста рисунок абсолютно точен.)

Обращения к регистрам производятся в соответствии с табл. 9.3.

Таблица 9.3

Обращения к регистрам таймера/счетчика 8254

Все остальные комбинации приводят к тому, что линии данных переводятся в высокоимпедансное состояние. Когда А1 =АО = 1,выполнение записи в регистр управления или выдачи приказа зависит от старшего бита выводимого байта. В последних трех комбинациях считывание OLили регистра состояния определяет предыдущий приказ.

Имеются два вида приказов. Приказ фиксации счетчика заставляет соответствующий OLзафиксировать содержимое СЕ счетчика, определяемого двумя старшими битами приказа. Приказ обратного считывания фиксирует комбинацию СЕ или "готовит" комбинацию регистров состояния для считывания. Подготовка регистра состояния означает

Рис. 9.26.Схема таймера/счетчика 8254

его считывание, когда в следующей операции считывания осуществляется ввод из счет-'чика. Состояния 00, 01и 10двух старших бит показывают приказ фиксации счетчика, а состояние 11 -приказ обратного считывания. В приказе фиксации биты 5и 4должны быть нулевыми, а остальные биты не используются. Приказ обратного считывания имеет следующий формат:

![]()

ILЕсли битCOUNT = 0,фиксируются СЕ всех счетчиков, битыCNTкоторых содержат 1. |всли, например,CNTO =CNT2 = 1иCNT1 = 0,то СЕ в счетчиках 0и 2фиксируются,"»в счетчике 1не фиксируется. АналогичноSTAT = 0вызывает подготовку регистров

Рис 9 27Регистры управления и состояния счетчиков

состояний счетчиков для ввода. Действия по фиксации и подготовке допускается указывать в одном приказе.

Форматы регистров управления и состояния показаны на рис. 9.27.Если два старших бита равны 1,они задают приказ обратного считывания; в противном случае они определяют счетчик. Если указан счетчик и биты 5-4содержат нули, то имеет место приказ фиксации, который направляется в регистр управления выбираемого старшими битами счетчика. Когда же комбинация в битах 5-4отличается от 00,она указывает тип ввода изOLили вывода вCR. Комбинация 01идентифицирует операции считывания/записи из (в)OL^/CR, комбинация 10 -из (в)OLix/CRv» и комбинация 11 -выполнение операций парами (первый байт из (в)OLi/CRiи второй из (в)OLn/CR^i) Запись одного байта в CRвызывает сброс другого байта Биты 1, 2и 3определяют режим, а бит 0определяет формат счета.

Таймер/счетчик имеет следующие режимы работы (через Nобозначен начальный счет)

Режим 0(прерывания по концу счета) .СигналGATE = 1разрешает счет,aGATE =О запрещает счет, причемGATEне влияет на выходOUT. Содержимое CRпередается в СЕ по первому импульсуCLKпосле того, как процессор осуществил запись в CR,независимо от сигнала на входеGATEИмпульс, который загружает СЕ, не учитывается при счете На выходеOUTформируется низкий уровень при записи в регистр управления, который сохраняется до достижения счетчиком 0.Режим 0предназначен в основном для счета событий.

Режим 1(аппаратно перезапускаемый одновибратор).После загрузки значения NвCRпереход 0 -* 1на входеGATEвызывает загрузку СЕ, переход 1 -»0на выходеOUTи запускает счет. Когда счетчик достигает 0,на выходеOUTформируется высокий уровень; таким образом, результатом является отрицательный импульс на выходеOUTс продолжительностью Nпериодов синхронизации

Ре&им 2<гчрч' v-и^йnilерьиышй гаймер) Посл„ шрузки значения Nв CR следующий импульс синхроь^ации осуществляет передачу из CRв СЕ На выходеOUTвозникаем переход 1-^ 0.когда счетчик достигает 0низкий уровень сохраняется в течение одною импульсаCJ-KЗгпсмна выходеOUT.появляется высокий уровень, производится повюрная загрузка СГ из CR,в результате на выходе 01Л появляется отрицательный импульс через Nгакгов синхронизации СигоалGAU --- 1разрешает счет, аGATiUзапрещаег Переход 0 " 1на входеGAJ 1вызыв^ г реинициализацию счета следующим импульсом <инхрони-)авд'и Данный pt-л.лviприменяется для реализации периодического интервального ыймера

Режим 3(генератор прямоугольного сигнала).Аналогичен режиму 2,но на выходе От формируется низкий уровень при достижении половины начального счета; этот уровень сохраняется до достижения счетчиком 0.Как и прежде, сигналGATEразрешает и запрещает счет, а его переход 0 -* 1рсинициализирует счет Этот режим применяется в генераторах, определяющих скорость передачи в бодах.

Режим 4(программно-запускаемый строб) .Аналогичен режиму 0,но на выходеOUTв процессе счета действую высокий уровень, а при достижении счетчиком 0появляется отрицательный импульс с продолжительностью в один такт синхронизации

Режим 5(аппаратно-запускаемый строб с перезапуском) После загрузки CRпереход 0^ 1на входеGATFвызывает передачу из CRв СЕ следующим импульсомCLK. В процессе счета на выходеOUTдействует высокий уровень, а при достижении счетчиком 0формируется отрицательный импульс с продолжительностью в один периодCLKСигналGATEможет в любой момент времени реинициализировать счет.

Начальное значение счета 0во всех режимах интерпретируется как 216или Ю4в зависимости от формата счета. Мы привели общие принципы работы микросхемы 8254,а подробное описание содержится в фирменных материалах.

MOV DX.OFFE9H MOV AL.,0 OUT DX,AL

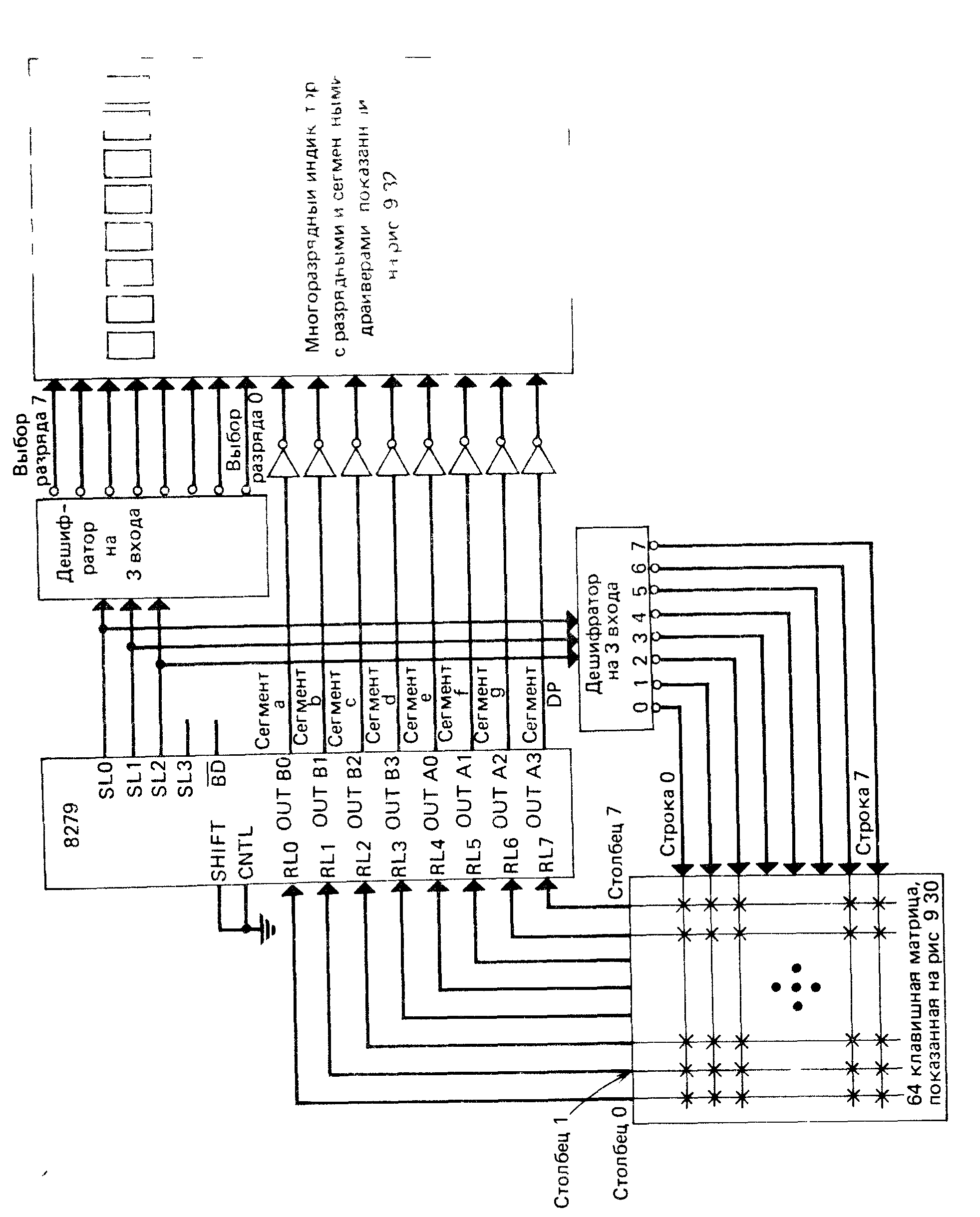

Рис 9 35Применение контроллера 8279в интерфейсе клавиатуры и многоразрядного индикатора

Таким образом, символы, сформированные нажатыми клавишами, можно считать через память IIFOДалее приведен программный фрагмент, в котором применяется программный ввод вывод для ввода восьми кодовых слов и запоминания их в 8байтном массивеKFYS(первый байт находи гся по старшему адресу)

МПу SI 8

MOV DX.OFFE9H

M0\/ A L,01000000 В

OUT OX.AL ^БХ7 MOV ПХОГГГ9Н !f l г •N М. ПХ

tls AL,Ot h

JZ IDLE

MOV DX,OFFE8H

IN AL,DX

MOV KEYS[SI-1],AL

DEC SI

JNZ NEXT

Первая команда инициализирует счетчик в SI, следующие )ри задаю г вводiioкт.но-му адресу как ввод изHIО Очередные три команды, начиная сmcskh IDL1 ,загтавля ют процессор ожидать до готовности ввода, а находящиеся за ними еще три команды передают введенные данные вKbYSПоследние две команды вызывают повторение последовательности до тех пор, пока не будут введены восемь символов

Для индикации символов процессор должен сначала выдать приказ записи в '1амя!ь индикатора, а затем выводить в нее данные Следующий фрагмеш индицирует восемь цифр, которые хранятся, начиная с DIGITS(младшая цифра хранится по меньшему ал.pecv)

MOV S1.8

MOV DX,OFFE9H MOV AL,10010000В OUT DX,AL MOV DX.OFFFSH AGAIN MOV AL,DIGi"[b(Si 1 j OUT DX,AL DEC SI JNZ AGAIN

Первая команда образует в SIсчетчик цифр, следующие 1ри выводят прикчз записи в память индикатора, а находящаяся за ними команда члгрул'-^ к вDXа фее буферной^ регистра данных Последние команды образуютциклвывода п'(фр вшмять индг каюра