- •Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

- •Глава 1 структура вычислительной машины

- •1.1 Общее устройство

- •1.2 Корпус pc

- •Slimline

- •Desktop

- •Корпус типа атх

- •1.3 Материнская плата

- •Chipset

- •Rom bios

- •1.4 Процессор

- •Типы процессоров

- •Сопроцессор

- •Оперативная память

- •Контроллеры

- •1.5 Устройства хранения данных

- •Дисководы

- •Винчестеры

- •Глава 2 конфигурирование системы пэвм

- •Install, installhigh

- •Глава 3 устройства вывода данных

- •Глава 4 назначение и функции операционной системы

- •Глава 5 производительность компьютера. Способы ее измерения

- •Глава 6 сети эвм и средства телекоммуникационного доступа

- •Глава 7 устройства ввода данных

- •Лекция 1. Эволюция микрокомпьютеров.

- •2.1. Введение

- •2.2. Структура памяти

- •2.3. Сегментация памяти

- •2.4. Структура ввода-вывода

- •2.5. Регистры

- •2.6. Операнды и режимы адресации операндов

- •2.7. Замечания о режимах адресации

- •4. Назначение выводов мп

- •3. Программная модель микропроцессора

- •9 Интерфейсы ввода-вывода

- •9.1 Интерфейсы последовательной связи

- •9.2 Параллельная связь

- •9.5. Контроллрры прямого доступа к памяти

- •9.6. Контроллеры накопителей на гибких дисках

- •9.7. Интерфейс максимального режима и 16-битной шины

- •10. Полупроводниковая память

- •§ 10.5 Касается разнообразных видов пзу.

- •10.1. Общая организация памяти

- •10.2. Статические зупв

- •10.3. Динамические зупв

- •10.4. Резервное питание для полупроводниковой памяти

- •10.5. Постоянные запоминающие устройства

- •2) Компьютерные сети

- •2.1. Общие понятия

- •2.2.1. Топологии

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •-Звезда

- •2.2.2. Компоненты сети -Концентратор и коммутатор

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •2.3. Беспроводные сети

- •2.3.1. Radio-Ethernet

- •2.3.2. Gprs

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы для Ноутбуков, кпк и пк

- •Gprs модемы существуют в нескольких исполнениях:

- •Nokia d211

- •2.3.3. Bluetooth

9.5. Контроллрры прямого доступа к памяти

В гл 6было показано, что контроллер ПДП может стагь ведущим шины и управлягь передачей данных между ингерфейсом ввода-вывода и памятью или интерфейсом внешней памяти и памягью В процессе передачи он должен помещать адресtн-г тину, а также выдавать и принимать сигналы квитированияiai\, л.'к эго целае! логика управления ши ной Назначение коптролл1ра ПДП осущестпячь последовательное п.. передач(ieпередачу блока) по<редством пропусков ("кражи") циклов шины

Обычно контроллер ПДП рассчитан на обслуживание одною или нескольких интерфейсов ввода-вывода или внешней памяти и каждый интерфейс подключается к контроллеру набором проводников Часть контроллера ПДП, предназначенная для обслужи вания одного интерфейса, называется каналом

Общая организация одноканального контроллера ПДП и его основные связи показа ны на рис 9 36Кроме обычных регистров управления и состояния, в каждом канале должны быгь регистр адреса и счетчик байт (или слов) Иницьачтпаиия контроллера со-

?Рис 9.36.Общая организация контроллера ПДП

стоит в загрузке в эти регистры начального (конечного) адреса массива в гамяти, который служит буфером, и числа передаваемых байт (слов) При вводе в памягь при наличии данных интерфейс делает запрос ПДП Затем контроллер формируег запрос шины и при получении разрешения шины выводит содержимое регистра адреса на шину адреса, посылает подтверждение в интерфейс и выдает сигналы считывания ввода-вывода и записи в память После этого интерфейс помещает данные на шину данных и снимае! свой запрос Когда память воспринимает данные, она возвращает в контроллер сигнал готовности; контроллер осуществляет инкремент (декременг) регистра адреса, декремент счетчика байт (слов) и снимает запрос шины При достижении счегчиком нуля процесс прекращается и выдается сигнал в процессор как запрос прерывания или в ишер-феис для извещения о том, что передачи завершены Вывод реализуется аналогично, но контроллер выдает сигналы записи ввода-вывода и считывания из памяти, а данные пе редаются в другом направлении.

В качестве примера рассмотрим контроллер ПДП 8237фирмыIntel. Его общая организация вместе с дополнительной логикой, необходимой в системе на базе микропроцессора 8088,приведена на рис 9 37,а конфигурация в минимальном режиме с контроллером ПДП -на рис 938

Когда данные помещаются в регистры контроллера или считываются из них, контроллер ведет себя как любой другой интерфейс ввода-вывода. В качестве ведомого он воспринимает 16-битные адреса, причем 12их старших бит определяют выбор микросхе мы, а 4младших применяются для внутренней адресации. Когда сигналыHRO=^CS — = 0,контроллер превращается в ведомого и линииTORиIOWявляются входными Процессор может обратиться к внутренним регистрам, формируя активный сигналIORИлиТО\У СигналAEN, которым ведущий контроллер идентифицирует выдачу адреса, на-Находится в состоянии 0до тех пор, пока система взаимодействует с внутренними регистрами

Рис 9 37Организация контроллера ПДП 8237

В качестве ведущего контроллер должен выдавать адреса шины Младший байт адре са выводится на линии А7 АО, а старший -на линииDB7DBOс одновременной установ койAEN = 1При таком уровне сигналаAENразрешается внешний регистр защелка адреса обеспечивая вывод старшего байта адреса на линии А15 А8 СигналAFNприме няется также для запрещения регистров защелок адреса 8282,подключенных к линиям А19 А8 иAD7ADOпроцессора Через небольшой временной интервал после выдачи сиг нала AENна выходе строба адреса (ADSTB) формируется импульс Он применяется для загрузки бит 8-15адреса в регистры защелки 8282,подключенные к линиям А15 А8 Старшие 4бита адреса А19 А16 контроллер 8237не выдает,и их необходимо програм мировать отдельно до начала блоковой передачи Для хранения этих бит адреса потребу ется 4-битный порт ввода вывода, в который можно вывести данные, как в любой дру гой порт Во время блоковой передачи содержимое этого порта изменять нельзя, следо вательно, за одну передачу можно передать максимум 216байт

Рис 938Система на базе микропроцессора 8088в минимальном режиме с контролле ром 8237

Рис 939Схема кодирования сигналовRD^ЫиЮ/М

Примечание Если t eтребуются трж табильные линии п щкчзов можно исполь зовать дешифрагор (8205ти ^S^"1) Микросхема 741S25 /не рекомендуется из за возможних выбросов напряжения, когда она переходит в вьп ок '»имнеданснос состоя ние или выхотит из него

Являясь ведущим, контроллер дочжен выводигь также необходимые сигналы считы вания/залиси Это уже знчкомые нам сигналы~10К' (считывание ввоца-вывода) ,'MEMR(считывание из памяти),lOW(запись ввода-вывода) и1МЕМЛУ (запись в память) Так как эти сигналы не соответствуют выходным сигналам ^D,"WRи Ю/М микропроцессо ра 8088в минимальном режиме, для преобразования сигналов контроллера потребую ся схема кодирования сигналов считывания/запит (рис 9 ^9)Во время передачи ПДП контроллер запрещает выхсгы схемы кодирования считывания/записи сигналомAFNКонечно, интерфейсы памяти и ввода-Biгвода в слстсме необходимо спроектироватьтак чтобы они реагировали на сигналыMFMR,MFUW~T<7R,"КЖ вместо сигналов "RD"WRи Ю/Ч Как и в процессоре, сигнал КГAD\ применяетсяs1я расширения циклов шины при обслуживании медленных угтройсгв посредством введения сосгоянлй ожидадия СигналRESETсбрасывает регистры управления, остояния и временною храпения и флажки запросов, л также Уетанавливчет ф гажки масок ГииияFOP- двунаправлен ная При достижении счетчиком нуля на ней формируется отрицательный имчуль кото рый лиС'0(лу-кит запросом прерывания ибо подается ч интерфейсvтройствч Ро и ин тщфейс может выдать на эту линию сшнал с активным ьизким уровнем В люЭом сту чае ыпкий \ровень на линии ГОР приосгана"гiв°ет бло)- овую гнр^м1^ После приоггаHOBK-fсе молсо воюбновить в соответствии с режимом ра^оти ьочтрптсра 8^37

В составе коюроллера име ;ея риис^ры управления, состоя ыя и временною хра нения a^iже четыре канала Каждый каьал имеет свои регипр режима тек пш" рг гкс р адреса базовый регистр адреса, текущий регистр счетчика баЛь базовый регистр счетчика б йт, флажок запроса и флажок маек» Каждыйлзkihi ю-цдопускает ?^боту в отцом из четырех режиг^ов, текущий рсжип определясгся битами 7и 6канггьного ре гистра режима Кратко охарактеризуем режчмь! работы контроллст

Режимодиночной передачи (01)После калдой перепачи контроллерoci»бождает шину процессору минимум на один цикл шичы, но сразу же начинаетщсверку входэвDREQи, как только обнаруживает активный игаал инициирует следующую передачу

Р"жим блоковой передачи (10)Активный сигналDRbQдолжен сохрдня^ь^1теii,»uдо формирования активного сигналаDACKпосле ч г о шияа т»е о^нобожгл?с ято ч в^рпд ьлч пре^ачи вгего 1пока

Режим передачи по требованию (00)Аналогичен предыдущему нопослр каждой пе ре ^ачи провсряегся сигналDRbQ Iели он пассивный передачи приостанавливаются до тех пор 1юка сигналDRTО не будет активным После этого передача про юлжается с той точки в коюрой она была приостановлена Данный режим позволяет интерфейсу остановить передачу если устройство не может продолжать ее

Каскадный режим (11)Обеспечивает каскадирование конгроллеров 8237для слу чая когда в подсистеме ПДП требу eir-яболее четырех каналов При каскадировании контроллеры второго уровня подключаются к контроллерам первого уровня линиямиHRQкDREQиHLD4 кDACК Объем данной книги не позволяег рассмотреть этот ре жим подробнее

В любом режиме при достижении счетчиком нуля формируется сигнал ЕОР = 0и пе редача прекращается

Бит 5в регистре режима определяет инкремент (0)или декремент (1)регистра ад реса после каждой передачи т е идентифицирует порядок запоминания данных в памя ти Когда бит 4содержит 1,разрешается автоинициализация При начальной загрузке те кущих регистров адреса и счетчика байт их содержимое помешается также в базовые регистры адреса и счетчика байт Если автоинициализация разрешена, при достижении счетчиком н\ля содержимое базовых регистров автоматически передается в текущие ре гисгры Биты 2и 3определяют тип производимой передачи контроль (00),запись (01) и считывание (10)Контроль предназначен для проверки информации, относящейся к предыдущей операции ввода или вывода и фактически не связан с текущей передачей Мы не будем подробнее останавливаться на контроле Два младших бита при выводе в регистр режима идентифицируют выбираемый канал ПДП

Кроме блоковых передач между памятью и устройствами ввода вывода или внешней памятью, контроллер 8237может управлять передачами памяти -память При этом бай ты из области-источника помещаются во внутренний 8-битный регистр временного хранения, а затем передаются в область-получатель Следовательно, для каждой передачи па мять —память требуются два цикла шины Для адресации источника применяется теку щий регистр адреса канала 0Текущие регистры адреса и счетчика байт канала 1обеспе чивают адресацию получателя и счет Инкремент или декремент адреса получателя необ ходимо производить как обычно, но при }становке соответствующего бита в регистре управления адрес источника можно сохранять кетменным При этом один и ют же байт данных передается во всю область получатель

В регистре управления передача память -память разрешается установкой бита 0в состояние 1гри этом единичное состояние бюд 1показывает что адрес источника необ ходимо сохранять неизменным Бит 2применяется для разрешения (0)или запрещения(1)контроллера а бит 3определяет тип синхронизации Iели позволяет быстродействие сисгемы бит 3можно установить в о юянле 1,определяя сжатую синхронизацию В этом сгуча» для випоч {"ния бог[ьшинс1ва передач требуются всего дьа такта синхро низании (^мimet) Бит ч чре ^e^гeтфиксироч-яныузи циклические (круговые,» приоритеты Обычно к-и ал 0имеег высший приоритет, а канал 3 -низший, но если бит4содержит 1,приоритеты после каждой передачи циклически изменяются Например, если до передачи бьли приоритеты 2л 0 1то после передачиohf станут 3012Цикли ческое изменение приоритетов позволяет контр шеру предотвратить монополи $ацию Шины одним каналом При использовании оСычь >й еинхргшэяци-iконтроллер допуска ет программное определение продол кителььосш сигналовTOWh'hehw Состояние 1 бита 5показывает, что эти сигналы расширяются на два тактд синхронизации Програм ма может тч^жс определитьvpo^e^ активно и сиги1ов Р ^>hDACKустановкой юи IГро ом бита(\(bki ''))и б(ia7<r»/\CK1i 1ди-ж'и ( ст.'н е би а 6показывв1 т чтоDRI-'Qимеет активный низкий уровень, а бита 7 --чтоDACKимеет активный выг кий уровень. Установка состояний этих бит зависит от характеристик тины

В регистре состояния младшие 4бита показывают состояния счетчиков четырех к-d налов, а старшие 4бита фиксируют наличие или отсутствие запросов ПДП. Для млал ших 4бит состояние 1битаппоказывает, что в каналепсчетчик достиг 0;для старши?4бит состояние 1битап + 4сигнализирует о наличии запроса в каналеп.

В каждом канале имеются также флажок запроса и флажок маски. Запрос ПДП мож но запрограммировать так, как будто подается сигнал DREQ. Установка в канале флаж ка запроса имеет те же последствия, что и активный сигнал DREQ;флажок сбрасывает ся активным сигналом ЕОР. При установке в состояние 1флажок маски запрещает ка нал, поэтому запросы ПДП (аппаратные или программные) не распознаются. Если кана! не запрограммирован на автоинициализацию, флажок маски автоматически устанавли вается активным сигналом ЕОР.Флажки запроса и маски программируются с помощьк приказов, в которых бит 2определяет состояние флажка, а биты 1и 0задают номер ка нала. Остальные биты приказа не используются. Предусмотрен также приказ воздей ствия сразу на все 4флажка масок. В этом приказе состояние битаппереводит в знало гичное состояние флажок маски каналап.

Кроме приказов, определяющих состояния флажков, имеются приказы главной сброса и сброса триггера первый/последний. Приказ главного сброса имеет те же послед ствия, что и сигнал RESET. Триггер первый/последний предназначен для загрузю 16-битных регистров адреса и счетчиков. Так как контроллер 8237может одновремен но воспринимать только по одному байту, загрузка каждого регистра производится дву мя операциями вывода. Если первоначально триггер первый/последний находится в со стоянии 0,первый выводимый в эти регистры байт загружается в младший байт, а триг гер устанавливается в состояние 1.При выводе второго байта единичное состояние триг гера направляет его в старший байт. После этого триггер сбрасывается в состояние О Приказ сброса триггера первый/последний предназначен для инициализации триггера дс производства операций вывода. Ни один из двух рассмотренных приказов не связанsпередачей данных по шине данных. Они автоматически выполняются контроллером когда осуществляется запись по соответствующему адресу.

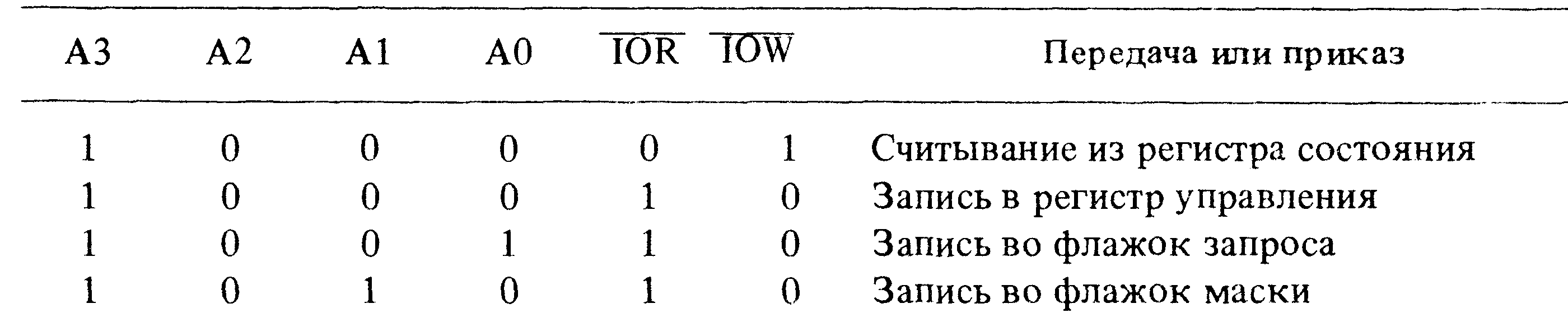

Адресация разнообразных регистров и приказов осуществляется с помощью лини^ CS,IOR, IOWи АЗ-АО. Сигнал~CS == 0определяет обращение к контроллеру. Сигна;

A3 == 0при адресации регистров адреса или счетчика и A3 = 1при обращении к регист рам управления или состояния, а также при выдаче приказа. При адресации регистре! адреса или счетчика линии А2 и А1 определяют номер канала; АО == 0задает текущий регистр адреса и АО = 1 —текущий счетчик. В операции считывания IOR == 0и IOW = = 1,а в операции записи 10R = 1иtow = 0.Запись в текущий регистр адреса или счет чик одновременно загружает в соответствующий базовый регистр. Суммарные сведеню по адресации сведены в табл. 9.5.

Таблица 9.5

Адресация в контроллере ПДП

Отметим, что наименьший адрес порта, назначаемый контроллеру. 8237,должен быть кратным 16,Регистр временного хранения можно считать только по завершению всей блоковой передачи память —память. Все не показанные в таблице комбинации являются недопустимыми.

Действия контроллера во времени разделяются на состояния SI,SO,SI,S2, S3,S4 иSW(см. схему на рис. 9.40).Между передачами контроллер реализует последовательность холостых состоянийSI. В каждом состоянииSIпроизводится проверка линийDREQ —не запрашивается ли передача ПДП. Если CS~— 0и все сигналы DREQпассивны, контроллер превращается в ведомого и с ним может взаимодействовать процессор. При наличии активного сигнала DREQформируется сигналHRQи контроллер переходит в состояниеSO. СостоянияSOповторяются до получения ответного сигналаHEDA, после чего контроллер повторяет состоянияS1-S4. Состояние SIможно пропустить, если старший байт адреса передачи изменять не нужно. Когда в передаче участвует устройство, которое не может реагировать достаточно быстро, вводятся состояния ожиданияSW.В обычной синхронизации необходимы состояния S3,но, если шина и интерфейсы допускают сжатую синхронизацию, состояния S3удаляются. В состоянии S4проверяется режим передачи и, за исключением незаконченной передачи блока в режиме блоковой передачи и в режиме по требованию, выполняется возврат в состояние SI.Временная диаграмма передачи из интерфейса в память представлена на рис. 9.41.