3.1. Центральное обрабатывающее устройство

Центральное обрабатывающее устройство (далее процессор) предназначено для обработки данных, выполнения вычислений с различными типами данных (целые числа, числа с плавающей точкой, адреса), формирования физического адреса и.т.д. Это все требует значительного времени. Поэтому при разработке необходимо ориентироваться прежде всего на увеличение быстродействия проектируемой ЭВМ. На данном этапе проектирования это возможно путем введения конвейерной обработки исполняемых команд.

При разработке процессора будем опираться на семейство СБИС Am29300, в которое входят следующие микросхемы, необходимые согласно варианту:

Аm29332 - арифметико-логическое устройство;

Am29331 - cеквенсор микрокоманд.

Было взято именно это семейство, поскольку микросхемы являются 32-разрядными, а также на основе этого семейства автором был выполнен курсовой проект по дисциплине “Схемотехника”.

Характерной особенностью архитектуры проектируемой ЭВМ является наличие конвейерной обработки как на уровне команд, так и на уровне микрокоманд. Это достигается тем, что после микропрограммной памяти находится конвейерный регистр микрокоманд. Таким образом, в цикле исполнения i-той микрокоманды можно смело читать из микропрограммной памяти (i+1)-ую, которая будет сохранена в регистре микрокоманд и исполнена в (i+1)-цикле.

Получаем один конвейер: “ПНА Секвенсор МПП Регистр микрокоманд”, реализованный в микропрограммном устройстве управления; и второй: “АЛУ Выходной регистр адреса (данных)”, реализованный в операционном блоке.

Структурная схема процессора изображена в приложении 2.

В составе процессора можно выделить три функциональных узла: операционный блок, микропрограммное устройство управления, буфер TLB (адресный КЭШ). Определим назначение и особенности реализации этих узлов.

Операционный блок (ОБ) состоит из арифметико-логического устройства (АЛУ), регистра адреса и буфера входных и выходных данных. Предназначен для выполнения логических, арифметических и сдвиговых операций над поступающими на вход данными и выдачи результата на выходную шину данных АЛУ. Этот результат может быть сохранен в регистре выходных данных или в регистре адреса в зависимости от характера данных.

Регистры входных и выходных данных, а также регистр адреса являются интерфейсными. Через них операционный блок обменивается информацией с шинами адреса (AB) и данных (DB).

АЛУ является полностью комбинационным устройством, выполняющим некоторый набор операций в зависимости от инструкций, поступающих с регистра микрокоманд. Результат операции АЛУ выставляет на выходной шине данных.

Микропрограммное устройство управления (МУУ) состоит из регистра команд, регистра микрокоманд, преобразователя начального адреса, секвенсора микрокоманд и микропрограммной памяти. Предназначено для управления последовательностью выполнения микрокоманд, организации прерываний.

Регистр команд, также как и регистры адреса и входных и выходных данных, является интерфейсным. Через него с шины данных подается очередная команда.

Преобразователь начального адреса (ПНА) предназначен для дешифрации кода операции в адрес микропрограммной памяти, по которому находится первая микрокоманда. ПНА может быть выполнен как комбинационным устройством, так и в виде ПЗУ, в котором зашиты начальные адреса последовательностей микрокоманд.

Микропрограммная память (МПП) представляет собой ПЗУ и предназначена для хранения последовательностей микрокоманд.

Регистр микрокоманд является конвейерным регистром, выдающим по фронту синхроимпульса очередную микрокоманду для выполнения.

Секвенсор – основное устройство МУУ. Оно адресует микропрограммную память. Для выбора адреса следующей микрокоманды используются источники:

ПНА;

регистр микрокоманд;

зависит от флагов;

стек.

Имеется вход INTR секвенсора микрокоманд. На этот вход с шины управления поступает запрос на прерывание. Пусть при возникновении прерывания секвенсор будет производить действия, аналогичные секвеносору Am29331. Секвенсор определяет момент, когда прерывание возможно обработать и выставляет сигнал подтверждения INTA. Устройство, подавшее запрос, а точнее, контроллер устройства, выставляет на шину данных вектор прерывания. Процессор по вектору прерывания формирует физический адрес устройства.

В озможность

вложенных прерываний определяется

способом сохранения слова состояния

процессора. В данном секвенсоре

используется стек для сохранения адреса

возврата и слова состояния. Таким

образом, при такой структуре количество

вложений ограничивается размером стека.

Если стек полон, то помещение на верхушку

адреса возврата повлечет за собой потерю

самого первого (“нижнего”) адреса

возврата, что недопустимо. Поэтому при

полном стеке прерывание игнорируется.

Например, вAm29331

поддерживается 33 уровня вложения

прерываний, а в секвенсоре Am2910

только 5.

озможность

вложенных прерываний определяется

способом сохранения слова состояния

процессора. В данном секвенсоре

используется стек для сохранения адреса

возврата и слова состояния. Таким

образом, при такой структуре количество

вложений ограничивается размером стека.

Если стек полон, то помещение на верхушку

адреса возврата повлечет за собой потерю

самого первого (“нижнего”) адреса

возврата, что недопустимо. Поэтому при

полном стеке прерывание игнорируется.

Например, вAm29331

поддерживается 33 уровня вложения

прерываний, а в секвенсоре Am2910

только 5.

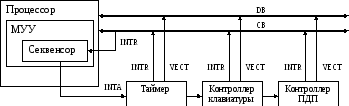

Система прерываний характеризуется 2 “параметрами”. Заданием предложена последоваельная структура стистемы прерываний с обработкой на микроуровне.

Последовательная структура означает, что имеется одна линия запроса, входящая в состав шины управления (CB) и цепочка сигналов подтверждения, проходящая через контроллеры устройств. По схеме видно, что приоритет прерывания определяется только порядком подключения устройств к линии подтверждения. Рассмотрим, что произойдет, выставляет запрос контроллер клавиатуры:

сформируется сигнал запроса, который подается на вход INTR секвенсора;

процессор выставит сигнал подтверждения, который пройдет через таймер;

цепочка оборвется на контроллере клавиатуры;

получив сигнал подтверждения, контроллер клавиатуры выставляет вектор прерывания и данное прерывание будет обработано.

Прерывание на микроуровне имеет меньшее время ответа, то есть время между подачей запроса на прерывание и началом его обработки, поскольку нет необходимости ждать завершения выполнения команды. Прерывание производится по окончании микрокоманды. Однако, необходимо запоминать больше информации. В отличии от информации, которую надо запомнить при прерывании на макроуровне, еще необходимо запомнить адрес текущей микрокоманды. Возврат из прерывания осуществляется выталкиванием из стека адреса возврата и выполнением микрокоманды по этому адресу.

Буфер TLB – Translocation Lookaside Buffer – адресный КЭШ. КЭШ – сверхоперативное запоминающее устройство. Назначение TLB – уменьшение времени обращения к медленной по сравнению с СОЗУ оперативной памяти.

Прежде чем проектировать буфер TLB, рассмотрим организацию памяти. Заданием предложена страничная организация памяти. Линейное адресное пространство объемом 232 = 4Гбайт делится на 1М страниц по 4 Кбайт каждая. Физическая память также подразделяется на страницы того же размера.

П роцессор

выставляет линейный адрес, из которого

с помощью страничного преобразования

необходимо получить физический. Так

как размер страницы – 4Кбайт, то смещение

в пределах страницы задается 12 младшими

разрядами. Следовательно для выбора

страницы остаются 20 старших разрядов.

Процесс преобразования можно изобразить

следующим образом:

роцессор

выставляет линейный адрес, из которого

с помощью страничного преобразования

необходимо получить физический. Так

как размер страницы – 4Кбайт, то смещение

в пределах страницы задается 12 младшими

разрядами. Следовательно для выбора

страницы остаются 20 старших разрядов.

Процесс преобразования можно изобразить

следующим образом:

Это преобразование - одноэтапное и является скорее теоретическим, чем практическим, поскольку потребуется линейная таблица на 1М элементов. Каждый элемент таблицы будет занимать 4 байта (20 бит – номер физической страницы + служебная информация) и являтся дескриптором страницы. Получаем, что для хранения таблицы страниц необходимо выделить блок памяти 4Мбайт. А в многозадачной среде такая таблица требуется для каждой задачи, что, конечно, практически неосуществимо. Для решения этой проблемы воспользуемся решением, предложенным в процессоре i486. Там реализовано двухэтапное преобразование. Основа преобразования – регистр управления CR3. Он содержит 20-битный физический базовый адрес каталога страниц текущей задачи и называется регистром базового адреса каталога страниц – PDBR (Page Directory Base Register). Данный регистр является единственным внутренним регистром процессора, который содержит физический адрес памяти. Младшие 12 бит адреса считаются нулевыми, поскольку каталог выравнен по границе страниц. Предполагается, что каталог постоянно находится в памяти.

Таблица страниц первого уровня называется каталогом страниц. Она содержит 1024 32-битных дескриптора, называемых элементами каталога страниц PDE (Page Directory Entry). Каждый из них адресует свою подчиненную таблицу страниц второго уровня. Каждая таблица страниц содержит 1024 32-битных дескриптора, называемых элементами таблицы страниц – PTE (Page Table Entry). И, наконец, каждый элемент PTE адресует страничный кадр в физической памяти. Надо отметить, что каталог страниц и каждая таблица страниц входят ровно на одну страницу (1K x 4байта = 4Кбайт).

Таким образом, преобразование линейного адреса в физический можно представить последовательностью следующих действий:

старшие 10 бит (31-22) линейного адреса служат индексом каталога страниц, выбирая один из 1024 элементов; выбранный элемент PDE определяет 20 битный адрес таблицы страниц;

средние 10 бит (21-12) линейного адреса индексируют таблицу страниц, выбирая из нее элемент PTE; он содержит 20-битный базовый адрес страничного кадра в физической памяти;

базовый адрес из элемента PTE сцепляется с 12 младшими битами (11-0) линейного адреса, в результате чего получается 32-битный физический адрес памяти, по кторому производится обращение.

За счет двойного обращения к оперативной памяти (таблица PDE, таблица PTE) снижается скорость работы. Однако, вариантом предусмотрен адресный КЭШ для элементов таблицы страниц. КЭШ имеет большую вероятность попадания, поэтому резко снижается количество обращений к оперативной памяти и количество циклов шин. Дополнительные циклы шины выполняются только при обращении к новой странице.

Теперь

разберемся, что должно находиться в

этих таблицах. Очевидно, что в каталоге

страниц должны находиться базовые

адреса страничных таблиц. В самой таблице

страниц должны, по всей видимости,

находятся дескрипторы страниц. Элемент

таблицы является 4-байтовым и имеет

структуру, аналогичную дескриптору

страницы в i486:

Теперь

разберемся, что должно находиться в

этих таблицах. Очевидно, что в каталоге

страниц должны находиться базовые

адреса страничных таблиц. В самой таблице

страниц должны, по всей видимости,

находятся дескрипторы страниц. Элемент

таблицы является 4-байтовым и имеет

структуру, аналогичную дескриптору

страницы в i486:

В поле адреса начала страничного кадра находится физический базовый адрес страницы. Так как в физической памяти страницы таблиц выравнены по границам страниц (по границам 4 Кбайт), младшие 12 бит базового адреса считаются нулевыми. В элементе PDE адрес страничного кадра является адресом таблицы страниц. В элементе РТЕ адрес страничного кадра является адресом страницы, содержащей данные или команды.

Биты 11-9 - биты системного программиста. Процессор никогда не использует и не изменяет их. Разработчики операционных систем могут привлечь эти биты своих целей.

Биты D и A изначально были предусмотрены для алгоритма своппинга LRU для КЭШа малого размера. Для больших КЭШей используется алгоритм псевдоLRU, а биты A и D оставили для преемственности. Эти биты содержат информацию об использовании страницы. Бит А сообщает об обращении для считывания или записи к странице или таблице страниц второго уровня, а бит D сообщает об обращении к таблице для записи. Бит D в элементах РDЕ каталога не определен.

Биты PCD и PWT применяются для управления кэшированием на уровне страниц.

Биты считывания/записи и пользователь/супервизор применяются в механизме защиты.

Бит присутствия P показывает, отображается ли адрес страничного кадра на страницу в физической памяти. Когда P=1, страница находится в памяти. Когда бит Р=0, страницы в памяти нет, и остальная часть элемента таблицы страниц доступна для операционной системы, например, для хранения информации о местонахождении отсутствующей страницы.

Теперь непосредственно перейдем к буферу TLB. Как понятно из всего вышесказанного, буфер TLB работает только с 20 старшими битами линейного адреса. Алгоритм записи – обратная запись, то есть при КЭШ-попадании запись только в КЭШ, иначе и в КЭШ и в память. Это уменьшает количество обращений к памяти и обеспечивает работу КЭШа как по чтению, так и по записи.

Буфер TLB представляет собой четырехнаправленную ассоциативную по множеству память. В блоке данных имеются восемь множеств по четыре элемента в каждом для хранения 32 элементов PTE. Элемент данных содержит 20 старших бит физического адреса. Их можно считать базовым адресом страницы, в котором младшие 12 бит содержат нули.

Блоку элементов данных соответствует блок достоверности, атрибутов и тэгов. Тэг содержит старшие 17 бит линейного адреса. В операции преобразовании адреса процессор использует биты 12, 13 и 14 для выбора одного из восьми множеств, а затем проверяет соответствие четырех тэгов этого множества старшим 17 битам линейного адреса. Если среди тэгов выбранного множества обнаруживается равенство и нужный бит достоверности содержит 1, то происходит преобразование линейного адреса путем замены его старших 20 бит на 20 бит элемента данных, где обнаружено равенство.

Для каждого множества предусмотрено три бита LRU, которые они следят за использованием данных в множестве и проверяют, когда требуется новый элемент, а ни один из элементов в множестве не является недостоверным. Применяется алгоритм замены псевдо-LRU. Он заключается в следующем: если в множестве есть недостоверная строка (бит достоверности равен 0), то для заполнения выбирается именно эта строка. Когда нет ни одной недостоверной строки, заменяемая строка выбирается с привлечением бит из блока LRU. Обозначим элементы данных в множестве через L0,L1,L2,L3. Каждому множеству в блоке LRU соответствуют три бита B0,B1,B2. Они модифицируются при каждом попадании и заполнении следующим образом:

если последнее обращение в множестве было к строке L0 или L1, то бит B0 устанавливается в 1; при обращении к строке L2 или L3 бит B0 сбрасывается в 0;

если последнее обращение в паре L0-L1 было к строке L0, то бит B1 устанавливается в 1; если к строке L1, то бит B1 сбрасывается в 0;

если последнее обращение к паре L2-L3 было к строке L2, то бит B2 устанавливается в 1; если к строке L3, то бит B2 сбрасывается в 0;

Далее выбор заменяемой строки определяется битами B0,B1 и B2:

-

B0

B1

B2

Заменяемая строка

0

0

Х

строка L0

0

1

Х

строка L1

1

Х

0

строка L2

1

Х

1

строка L3

О рганизация

буфера TLB:

рганизация

буфера TLB:

Подведем небольшой итог по буферу TLB. Процессор выставляет линейный адрес. Его необходимо преобразовать в физический. Сначала этот адрес поступает в TLB (адресный КЭШ). При совпадении ассоциативных признаков линейный адрес заменяется на физический и обращения к оперативной памяти вообще не происходит. При этом производятся соответствующие изменения с битами LRU. При КЭШ-промахе, то есть отсутствии данного тега в TLB, производится полное обращение к каталогу страниц (1-ое обращение к ОП), к таблице страниц (2-ое обращение к ОП) и по сформированному физическому адресу (3-ье обращение к ОП).