- •Цели работы.

- •Исходные данные.

- •Общие исходные данные.

- •Структурная схема процессора.

- •Описание структурной схемы процессора.

- •Система прерываний.

- •Адресный кэш.

- •Адресный сопроцессор.

- •Клавиатура и монитор.

- •Память.

- •Сопроцессор ввода/вывода.

- •Структурная схема сопроцессора ввода/вывода.

- •Управляющая информация для операций ввода/вывода.

- •Форматы основных видов управляющей информации.

- •Команды.

- •Формат команды.

- •Управляющие слова канала.

- •Формат управляющего слова канала.

- •Формат слова состояния канала сск.

- •Приказы.

- •Комментарии к функциональной схеме сопроцессора в/в.

- •Выводы.

- •Список литературы.

-

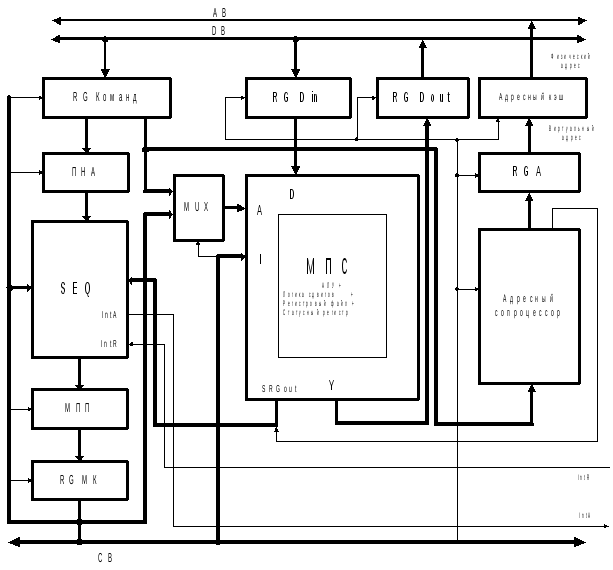

Структурная схема процессора.

-

Описание структурной схемы процессора.

На кристалле процессора расположено устройство управления, процессорная секция, содержащая АЛУ, логику сдвигов, статусный регистр и регистровый файл; адресный сопроцессор и адресный кэш, а также набор интерфейсных элементов для обеспечения взаимодействия CPU с системной шиной.

Микропрограммное устройство управления служит для задания последовательности микрокоманд, содержит:

-

Регистр команд хранит код операции, также адреса РОН, участвующих в операции. Из регистра команд КОП попадает в ПНА.

-

ПНА – преобразователь начального адреса, который может быть выполнен на PLD.

Секвенсор микрокоманд адресует микропрограммную память, результат выборки из которой сохраняется в регистре микрокоманд и является набором управляющих сигналов для всей ЭВМ. Включение в схему МУУ регистра микрокоманд определяет порядок конвейера – 2 и позволяет выбирать следующий адрес на этапе выполнения текущей микрокоманды.

-

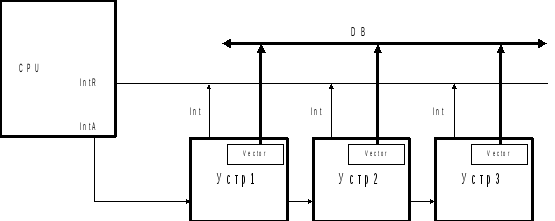

Система прерываний.

Система прерываний цепочечная на микро уровне.

Цепочечная структура прерываний характеризуется наличием единой линией запроса на прерывание, и линией подтверждения (INTA), проходящей через все источники прерываний и определяющей приоритеты прерываний в соответствии с порядком подключения устройств. Получив запрос, процессор переводит свой выходной буфер данных в третье состояние и выдает подтверждение по линии INTA, который проходит от одного устройства к другому, пока не достигнет инициатора прерывания, тем самым разрешая этому устройству выставить на шине данных свой идентификационный номер (косвенный адрес обработчика прерывания). Данная структура характерна более низкими затратами как аппаратных, так и программных средств на реализацию, но недостаток состоит в том, что приоритет устройства фиксирован и определяется порядком подключения, а также сигнал Interrupt Acknowledge (INTA) распространяется с некоторой временной задержкой.

Прерывания на микропрограммном отличаются коротким временем ответа, так как запрос на прерывание подается на вход секвенсора INTR, что означает возможность получения ответа по окончанию текущего микроцикла, если прерывания разрешены (сигнал INTEN = H), то #INTAL. Далее адрес возврата из прерывания сохраняется в стеке (возможна вложенность прерываний) и происходит переход к подпрограмме обработки прерывания по вектору.

Микропрограмма обработки прерывания должна сохранить все необходимые для дальнейшей работы регистры, PSW (слово состояния процессора). После завершения обработки прерывания адрес, на котором была остановлена прерванная микропрограмма, выталкивается из стека.

-

Адресный кэш.

Кэш память используется во всех современных компьютерах – это сравнительно небольшого объема статическая ассоциативная память, интегрированная на кристалл процессора, работающая на частоте АЛУ и содержащая наиболее необходимую для работы процессора информацию для уменьшения числа обращений к медленным устройствам, например, оперативной памяти (например, ALU – 1400 MHz, FSB – 266 MHz). При обращении к памяти в кэш записывается блок, содержащий как запрашиваемую, так и расположенную по соседним адресам информацию. Коэффициент успешных обращений к кэш памяти достигает 98 %.

Адресный кэш представляет собой память небольшого объема, предназначенную для хранения информации о преобразовании виртуальных адресов в физические. При использовании страничной организации памяти необходимо преобразовать виртуальный адрес в физический, для этого используют таблицу страниц, которую удобно загрузить в кэш, а не располагать в оперативной памяти. Это снизит время преобразования к минимуму и увеличит быстродействие процессора в целом. Конечно, адресный кэш эффективен в случае редких переходов между программами.