- •Цель работы

- •Задание

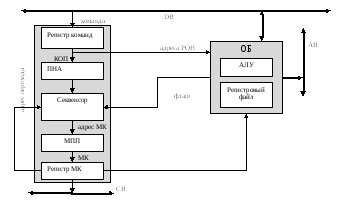

- •Разработка и описание структурной схемы

- •Центральный процессор

- •Первое слово команды

- •Второе слово команды

- •Оперативная память

- •Контроль памяти по Хеммингу

- •Система прерываний

- •Блок синхронизации и таймер

- •Прямой доступ к памяти (пдп)

- •Основные устройства ввода/вывода Клавиатура

- •Монитор

- •Жесткий диск

- •Разработка функциональной схемы кэш памяти команд и данных

- •Принцип работы схемы кэш памяти

- •Приложение

Первое слово команды

|

Адрес в ОЗУ | |

|

31 |

0 |

Второе слово команды

Рисунок 2 – Обобщенная структурная схема центрального процессора

Оперативная память

Основная память служит для хранения данных, программ, промежуточных или конечных результатов. По задания ОП многоблочная. ОП делится на ОЗУ и ПЗУ, в ПЗУ хранится программа начальной загрузки ЭВМ, ОЗУ служит для временного хранения данных и программ в процессе работы. 32 разряда шины адреса позволяют адресовать до 4Г слов.

Принцип многоблочности состоит в следующем, адресное пространство разбито на группы последовательных адресов и каждая такая группа обеспечивается отдельным банком памяти. Это позволяет легко заменять неисправные блоки памяти, а так же позволяет повысить производительность.

Все блоки памяти должны иметь разрядность хранимого слова равную 39 битам, 32 бита данных и контрольных 7 битов для обнаружения и исправления ошибок по коду Хемминга. Для ПЗУ будем использовать схему типа FLASH, а для ОЗУSDRAM

Для обращения к ПЗУ используются адреса с 0 по 220-1. Таким образом, можно адресовать 1М слов.

Адреса с 220по 221-1 используются для адресации ОЗУ. 18 старших разрядов адреса ОЗУ поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку. Два младших бита адреса содержат номер банка, это позволяет равномерно распределить нагрузку между банками, так как чтение обычно происходит последовательно из нескольких соседних адресов. Выбор банка обеспечивается дешифратором, который разрешает работу выбранному банку. В функциональном отношении такое ОП рассматривается как единое ЗУ, емкость которого равна суммарной емкости составляющих блоков, а быстродействие – быстродействию отдельного банка.

Рисунок 3 – Обобщенная структурная схема ОЗУ

Для формирования временных диаграмм записи, считывания, регенерации SDRAM, а также для выбора блока, к которому происходит обращение, необходим контроллер памяти. В контроллере есть счетчик регенерации. Когда этот счетчик выставляет флаг о необходимости регенерации ОЗУ, то контроллер блокирует доступ к памяти для ЦП и формирует специальные временные задержки для регенерации ячеек памяти в микросхеме. В контроллер памяти также входит блок контроля по Хеммингу.

Контроль памяти по Хеммингу

Поскольку при работе с памятью не исключена возможность различных сбоев и отказов, желательно иметь систему обнаружения и исправления ошибок. Для обнаружения ошибок и исправления некоторых из них используется код Хемминга. Код Хемминга позволяет обнаруживать и исправлять любые одиночные ошибки, а также обнаруживать двойные ошибки.

Для реализации контроля и исправления ошибок в памяти с использованием кода Хемминга возможно использовать специальную микросхему типа IDT49C465 или синтезировать схему на ПМЛ, позволяющую строить системы контроля на 32 бита.

При записи 32-разрядного слова в память корректор формирует 6-разрядный синдром и 1 разряд паритета, которые записываются в дополнительные разряды адресуемой ячейки ОЗУ (в памяти хранятся слова по 39 бит). При чтении слова из ячейки памяти информационные разряды поступают в корректор, туда же поступают и корректирующие разряды, схема вычисляет синдром.

Корректор анализирует полученную информацию и, если ошибки нет, то информационные разряды передаются на системную шину данных без изменений. В случае возникновения одиночной ошибки, корректирующая логика исправляет дефектный бит и формирует сигнал одиночной ошибки (#ERR), который дальше не нужен. Если же обнаруживается двукратная или более ошибка, то формируется сигнал «неисправимая ошибка» (#MERR), этот сигнал передается в систему прерываний, возникает соответствующее прерывание, которое должно быть обработано программой обработки такого рода ошибок.

Рисунок 4 – Схема обнаружения и исправления ошибок по Хеммингу