2.3.Блок синхронизации и таймер.

Блок синхронизации (БС) предназначен для обеспечения синхронной работы всех устройств ЭВМ. В его задачи входит генерация последовательностей синхросигналов заданной формы и длительности для ЦПУ, контроллеров, ОП и других устройств, входящих в состав ЭВМ. Необходимо предусмотреть возможность приостановления такта, изменения его длительности, что бывает нужно, например, для обмена информацией процессора с «медленными» внешними устройствами.

Таймер предназначен для деления машинного времени на временные интервалы. Представляет собой кварцевые часы, которые можно программно опрашивать, устанавливать, использовать в качестве будильника, в определённое время выдающего сигнал в процессор, или в качестве секундомера при замерах интервалов времени между внешними событиями и т. д.

2.4.Кэш команд и данных.

Кэш-память представляет собой быстродействующее статическое ОЗУ небольшого объёма, в котором по мере работы процессора сохраняется наиболее актуальная информация.

При раздельной кэш-памяти выборка команд и данных может производиться одновременно, при этом исключаются возможные конфликты. Последнее обстоятельство существенно в системах, использующих конвейеризацию команд, где процессор извлекает команды с опережением и заполняет ими буфер или конвейер.

Обычно ОП разрабатывается на базе динамического ОЗУ, быстродействие которого примерно в 10 раз ниже статического. При считывании информации из ОП она, попутно, запоминается в кэш-памяти, причем “на всякий случай” запоминается информация из соседней с ней ячеек. Так как программы обычно имеют циклический характер, а данные и команды размещены в соседних ячейках, в кэш-памяти постепенно накапливаются, а затем в ходе работы, автоматически обновляются текущие коды команд и данных, которые процессор часто использует. Таким образом в кэш-памяти накапливаются рабочие копии данных, хранимых в основном ОЗУ, причем считывание этих копий производится примерно в 10 раз быстрее, чем если бы считывались оригиналы данных. При записи информации, мы должны обязательно записать новые значения в ОЗУ, поэтому при этой операции мы не можем воспользоваться преимуществами кэш-памяти. Кэш со сквозной записью.

Ниже приведена таблица условий сохранения и обновления информации в ячейках кэш-памяти и ОП.

|

Режим работы |

Наличие копии в кэш-памяти |

Информация рмация | |

|

В кэш-памяти |

В ОЗУ | ||

|

Чтение |

Копия есть |

Не изменяется |

Не изменяется |

|

Копии нет |

Создается копия |

Не изменяется | |

|

Запись |

Копия есть |

Обновляется |

Обновляется |

|

Копии нет |

Создается копия |

Обновляется | |

2.5.Клавиатура и монитор.

Клавиатура и монитор содержат контроллер клавиатуры и адаптер монитора соответственно для обеспечения взаимодействия с узлами ЭВМ. Контроллеры содержат регистры статуса, команд и регистр данных.

Клавиатура предназначена для ввода информации в компьютер.

Монитор позволяет представлять данные в графической форме на экране дисплея.

2.6.Память.

Оперативной памятью называют устройство, которое служит для хранения информации (данных программ, промежуточных и конечных результатов обработки), непосредственно используемые в процессе выполнения операций в арифметическо-логическом устройстве и устройстве управления процессором [2].

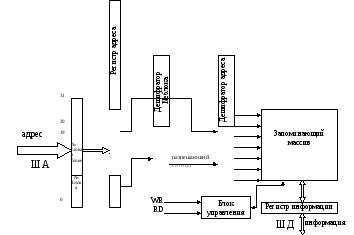

Многоблочная оперативная память представляет собой блоки одинакового размера по 2^20=1Мbколичеством до 2^12=4096 штук, которые выглядят, как представлено на рисунке 4

Элементарный

блок ОП

Данная оперативная память не подразумевает виртуальность памяти, т.е. она не может быть расширена за счет ВЗУ, а физический адрес ячейки памяти формируется следующим образом:

Физ. адрес = № блока ОП + смещение (адрес) в блоке

ОП функционирует следующим образом. С МП или КПДП приходит адрес по ША, который записывается в регистр адреса ОП, после чего старшие 12 разрядов дешифрируются в дешифраторе блока ОП и если адрес принадлежит данному блоку выдается разрешающий сигнал на дешифратор адреса в блоке, который формирует адрес ячейки памяти в запоминающем массиве. После чего по шине управления приходит сигнал WRилиRDот МП или КПДП и происходит запись или чтение информации в/из ОП.

2.7.Система ввода/вывода.

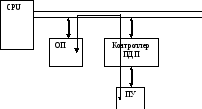

В соответствии с вариантом задания в качестве системы ввода/вывода в разрабатываемой ЭВМ должен быть реализован Прямой Доступ к Памяти (ПДП) – такой способ организации пересылки данных, когда устанавливается непосредственная связь между ПУ и ОП. При вводе/выводе CPUтолько производит инициализацию ПДП. Используется один контроллер прямого доступа для всех ПУ.

SYS

BUS

SYS

BUS

Рис.

Система Ввода/вывода

В данной ЭВМ реализован Прямой Доступ к Памяти с захватом цикла системной шины

ПДП ПДП ПДП ПДП

ЦП

ЦП

ЦП ЦП ЦП

ЦП

ЦП ЦП ЦП

Функции контроллера ПДП:

Формирование адреса ОП и управление адресной шиной

Управление пересылкой данных

Определение момента окончания обмена

Управление режимом

Так как несколько устройств управляют шиной, то нужен арбитраж, он находится в CPU. При арбитраже контроллер ПДП имеет более высокий приоритет, чем CPU.

Принцип захвата шины:

Контроллер выставляет сигнал BR (ЗШ) – захват шины, получив этот сигнал, арбитр выдаёт сигнал

BG (ПШ) – предоставление шины, получив сигнал BG контроллер выставляет сигнал BB (ШЗ) – шина занята, по этому сигналу все устройства отключаются от шины.

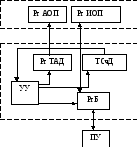

РгБ

– буферный регистр РгТАД

– счётчик текущего адреса данных

При

инициировании операции ввода/вывода

в ТСчД заносится размер подлежащего

передаче блока, а в РгТАД – начальный

адрес области памяти, используемой при

передаче. При передаче каждого байта

содержимое РгТАД увеличивается на 1,

при этом формируется адрес очередной

ячейки ОП, участвующей в передаче.

Одновременно содержимое ТСчД уменьшается

на 1. Обнуление ТСчД указывает на

завершение передачи. КПДП имеет более

высокий приоритет, чем у CPU.

Управление памятью переходит к КПДП

как только завершится цикл её работы,

выполняемый для текущей команды

процессора.

ОП

+1 -1

КПДП

Рис.

КПДП

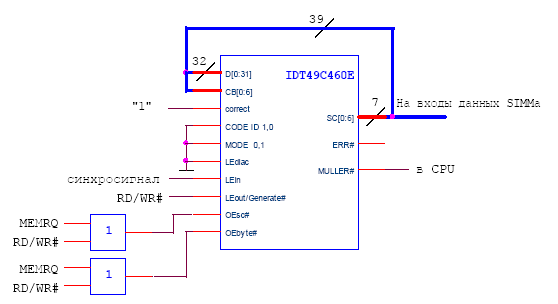

2.8.Система контроля:

При использовании в качестве ОЗУ микросхем динамической памяти возможно возникновение ошибок. Ошибки обычно бывают двух видов: постоянные и типа «сбой». Постоянные ошибки характеризуются тем, что содержимое одной или нескольких адресуемых ячеек заранее определено- из них всегда считывается одна и та же информация. Ошибки типа «сбой» связаны с разрядом конденсаторов динамических элементов памяти из-за действия кратковременных импульсов случайных помех по цепи питания

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

3.Разработка укрупненной структурной схемы арифметического сопроцессора и алгоритма деления.

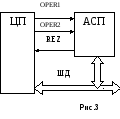

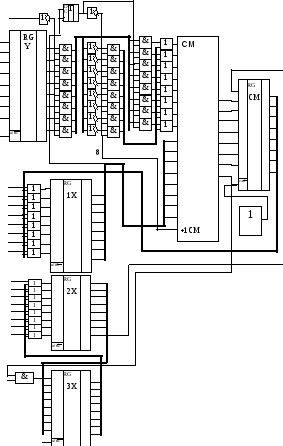

В данной структурной схеме у нас находится

арифметический сопроцессор, который

выполнят функции деления и

умножения. Структурная схема

функционирования представлена на

рисунке 3 и работает по следующему

алгоритму: при поступлении по ШД данных

в ЦП и одновременно в АСП (без кода

операции), содержащие коды операций,

дешифратором кода операций МП они

дешифрируются, после чего если текущая

дешифрированная операция является

операцией деления или умножения

микропроцессором выдаётся соответственно

сигналOPER1

или OPER2

на сопроцессор и не выполняет ее, а ждёт

результатов

данной структурной схеме у нас находится

арифметический сопроцессор, который

выполнят функции деления и

умножения. Структурная схема

функционирования представлена на

рисунке 3 и работает по следующему

алгоритму: при поступлении по ШД данных

в ЦП и одновременно в АСП (без кода

операции), содержащие коды операций,

дешифратором кода операций МП они

дешифрируются, после чего если текущая

дешифрированная операция является

операцией деления или умножения

микропроцессором выдаётся соответственно

сигналOPER1

или OPER2

на сопроцессор и не выполняет ее, а ждёт

результатов

с сопроцессора. При получении сигналов OPR1 или OPR2 на сопроцессор он выполняет операцию деления/умножения и выставляет результат на ШД. После этого АСП выдает сигнал REZ на МП сигнализируя, что результат операции находится на ШД и при получении данного сигнала МП считывает результат в аккумулятор и начинает считывать следующую команду.

Распределитель Делит ель

Mod2

Д

е

л

и

м

о

е

ст.

1

Д

е

л

и

м

о

е

мл.

1

Алгоритм деления

Берутся модули от делимого и делителя

Исходное значение остатка полагается равным старшим разрядам делимого

Частичный остаток удваивается путём сдвига на один разряд влево, при этом в освобождающийся при сдвиге младший разряд частичного остатка заносится очередная цифра делимого

Из сдвинутого частичного остатка вычитается делитель, если остаток положителен, иначе – прибавляется

Очередная цифра модуля частного равна 1, если результат вычитания положителен, и 0 если отрицателен

Пункты 3-5 последовательно повторяются для получения всех цифр модуля частного

Знак частного плюс, если знаки делимого и делителя одинаковы, иначе – минус

4.Выводы.

В данном курсовом проекте была разработана структурная схема гипотетической ЭВМ, а также функциональная схема арифметического сопроцессора, реализующего операцию деления