- •1)Цели выполнения и задание на курсовой проект 4

- •2) Разработка структурной схемы эвм

- •3) Разработка основных блоков эвм

- •3.1.) Центральный процессор

- •3.2.) Система прерываний

- •3.3) Арифметический сопроцессор

- •3.4.) Основная память

- •3.5.) Система ввода – вывода

- •3.6.) Блок синхронизации и таймер

- •3.7.) Монитор

- •3.8.) Клавиатура

- •4) Разработка контроллера прямого доступа к памяти

- •5) Выводы

- •Список литературы

3) Разработка основных блоков эвм

При разработке блоков ЭВМ мы будем основываться на семействе микросхем АМ29300. Этот выбор обусловлен наличием знаний по данному семейству микросхем (опыт при разработке курсового проекта по дисциплине «Схемотехника»), а также рекомендациями преподавателя.

3.1.) Центральный процессор

Как оговаривалось выше, процессор состоит из двух блоков: микропрограммное устройство управления и операционный блок. Опишем состав этих блоков:

Микропрограммное устройство управления:

Регистр команд

Предназначен для захвата слова команды из памяти ЭВМ (по шине DB)

Преобразователь начального адреса (ПНА)

Преобразует код операции (команды) в код стартовой микрооперации этой команды.

Секвенсор микрокоманд

Устройство, выполняющее выборку слов микрокоманд из микропрограммной памяти (либо посредством инкрементирования адреса микрооперации, либо безусловный переход к микрооперации, при этом адрес микрокоманды указывается явно, или же переход по флагу)

Микропрограммная память (МПП)

Хранит микрокоманды, выполняемые в данной ЭВМ

Регистр микрокоманд

Служит для захвата микрокоманды, извлеченной из МПП и выдачи ее на шину управления (CB).

Операционный блок

Двухпортовая микропроцессорная секция (МПС)

Выполняет арифметические и логические операции над данными в ЭВМ. Используется МПС AM29332 (выполнено наращивание разрядности до 32 бит).

Двухпортовый регистровый файл

Исполняет роль регистра общего назначения (РОН) для данной ЭВМ. Используется БИС AM29334 (выполнено наращивание разрядности до 32 бит). Все встроенные регистры программно- и микропрограммно-доступны.

Регистр входных и регистр выходных данных для МПС

Связывают МПС и шиной DB.

Дополнительные элементы обвязки

Служат для организации взаимодействия элементов процессора друг с другом и другими элементами ЭВМ. В их число входят:

Мультиплексоры выбора источника адреса для РОН (команды или микрокоманда)

Мультиплексоры задания ширины обрабатываемого битового поля

Логические элементы для организации условного тактирования

Описание процесса инициализации процессора.

При включении питания на вход секвенсора подается сигнал инициализации. При этом секвенсор блокирует все источники микроадреса и безусловно формирует на выходе нулевой адрес. По этому адресу в МПП записана микропрограмма инициализации процессора при выполнении которой производится начальный старт блоков ЭВМ. В реальных ЭВМ при инициализации начинается запуск операционной системы.

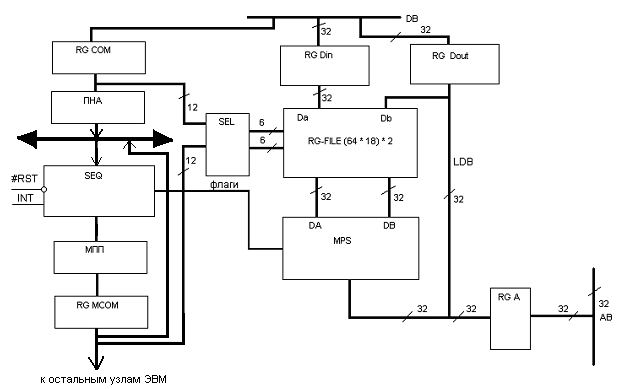

Ниже на рис. 3.1.1 представлена структурная схема процессора.

Рис. 3.1.1 Структурная схема процессора

3.2.) Система прерываний

Прерывания представляют собой средство программной обработки тех или иных событий, возникающих в вычислительной системе. Функции системы прерывания:

Организация вхождения в прерывающую программу

Организация приоритетного выбора между запросами, поступающими одновременно

Организация возврата в прерванную программу

Реализация прерываний оказывает значительное воздействие на производительность и гибкость системы. Это связано с тем, что оперативность системы при ответе на запрос напрямую зависит от метода реализации системы прерываний.

DB

Из

регистра МК ЦП

Из

регистра МК ЦП

ЦП PIC Устройство1 Устройство2 Устройство

N ПЗУ

вектор

INT

………………

Рис. 3.2.1 Структурная схема системы прерываний

При необходимости прерывания некое устройство выставляет запрос контроллеру. Контроллер прерываний обрабатывает запрос и выдает сигнал процессору о прерывании, помимо этого контроллер выставляет вектор прерывания, т.е. необходимую минимальную информацию об источнике прерывания. Информация же о причине прерывания считывается из регистра состояния устройства, вызвавшего прерывание. Вектор также является косвенным адресом программы обработки прерывания. Вектор поступает в ПЗУ, где происходит дешифрация вектора и преобразование его в стартовый адрес программы обработки, полученный адрес передается в ЦП. Все программы обработки прерываний перед непосредственной обработкой прерывания должны сохранять информацию о прерванной программе (слово состояния), а после обработки прерывания необходимо загружать в процессор данные прерванной программы. Управление контроллером осуществляется с шины CB. Данные прерванной программы оформляются в виде слова состояния процессора (ССП). Существует три основных способа реализации сохранения ССП:

Сохранять слово состояния в ОП, а вектор использовать в качестве косвенного адреса ОП.

Достоинство: простота и экономичность реализации. В качестве дополнительного оборудования потребуется только схема преобразования вектора в адрес ОП.

Недостаток: невозможно выполнять два прерывания подряд по одной и той же причине, т.к. в таком случае предыдущее ССП теряется.

Сохранять ССП в стеке

Достоинство: относительная простота реализации, возможны любые прерывания в любой последовательности. При этом максимальная глубина прерываний ограничена возможностью стека.

Недостаток: возврат к прерванным программам возможен только в последовательности их прерывания.

Использовать набор регистров, подключенных к ЦП

Достоинство: высокая скорость сохранения/выдачи ССП, как следствие – высокая реактивность системы.

Недостаток: высокая сложность реализации, высокая стоимость реализации. Как следствие цены – низкая максимальная глубина прерываний. Затраты на дополнительные регистры можно сократить, используя РОН процессора, но это приводит к сокращению регистров, которые могут использоваться для хранения переменных программ.

Оптимальным из этих трех вариантов считаю вариант использования стека. Физически же стек не реализуется. Вместо стека используется, как правило, последовательный блок адресов в ОП. Используется SP – stack pointer (указатель стека), т.е. адрес первой ячейки стека.