-

Блок синхронизации и таймер.

Для обеспечения синхронной работы всех узлов в структуре ЭВМ предусмотрен блок синхронизации. Блок синхронизации генерирует синхропоследовательности заданной формы и длительности для ЦП, таймера, контроллеров, ОП и других устройств, входящих в состав ЭВМ. С помощью БС можно реализовать изменение длительности такта, например, для чтения/записи из/во внешние устройства, обмен с которыми обычно происходит медленнее, чем с ОП или другими узлами.

В качестве системного тактового генератора была выбрана микросхема P2084A производителя Alliance Semiconductor. Устройство представляет собой универсальный умножитель частоты, способный выдавать синхропоследовательность частотой до 312 МНz.

В качестве делителя частоты выбран четырёхразрядный счетчик с синхронным сбросом и установкой.

Рис 4 . Блок синхронизации ЭВМ.

Таймер обеспечивает деление машинного времени на интервалы – кварцевые часы, которые программно доступны для записи/чтения. С помощью таймера можно, например, выдавать запрос контроллеру ОП для выполнения цикла регенерации памяти.

-

КЭШ.

Кэш память используется во всех современных компьютерах – это сравнительно небольшого объема статическая ассоциативная память, интегрированная на кристалл процессора, работающая на частоте АЛУ и содержащая наиболее необходимую для работы процессора информацию для уменьшения числа обращений к медленным устройствам, например, оперативной памяти. При обращении к памяти в кэш записывается блок, содержащий как запрашиваемую, так и расположенную по соседним адресам информацию. Коэффициент кэш-попаданий в буфер TLB составляет 95- 98 %. И только при кэш-промахе включается страничный механизм.

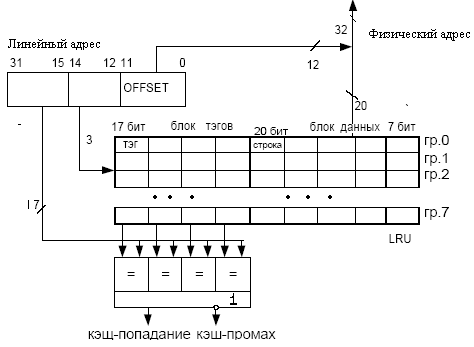

Буфер быстрого преобразования адреса (TLB — Translation Look-aside Buffer), или буфер ассоциативной трансляции, или буфер опережающей выборки представляет собой кэш-память. При каждом преобразовании номера виртуальной страницы в номер физической страницы результат заносится в TLB: номер физической страницы в блок данных, а виртуальной — в блок тэгов. Таким образом, в TLB попадают результаты нескольких последних операций трансляции адресов. При каждом обращении к ОП преобразователь адресов сначала производит поиск в памяти тегов TLB номера требуемой виртуальной страницы. При попадании адрес соответствующей физической страницы берется из памяти данных TLB. Если в TLB зафиксирован промах, то процедура преобразования адресов производится с помощью страничной таблицы, после чего осуществляется запись новой пары «номер виртуальной страницы — номер физический страницы» в TLB.

Блок данных разбивается на строки. Всего этих строк 32 и ширина строки 20 бит. В строку можно загрузить 20 старших бит начального адреса страницы. Каждой строке ставиться в соответствие тег в блоке тэгов. Тэг имеет ширину 17 бит.

Блок LRB - блок достоверности.

Рис 5.Структура буфера быстрого преобразования адресов

-

Клавиатура и монитор.

Клавиатура и монитор содержат контроллер клавиатуры и адаптер монитора соответственно для обеспечения взаимодействия с узлами ЭВМ. Контроллеры содержат регистры статуса, команд и регистр данных.

Клавиатура предназначена для ввода информации в компьютер. Для предоставления клавиатуре наивысшего приоритета, целесообразно подключить контроллер клавиатуры первым в цепи распространения сигнала INT A.

Монитор позволяет представлять данные в графической форме на экране дисплея.