- •Понятие о микропроцессорах и

- •Понятие о микропроцессорах и микроконтроллерах

- •Понятие о микропроцессорах и микроконтроллерах

- •Шинная организация. Характеристики шин.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

- •Структура микроконтроллера семейства MCS-51

- •Структура микроконтроллера семейства MCS-51

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Блок управления

- •Функции блока управления:

- •Функции блока управления:

- •Структура блока счетчика команд (СК)

- •Режимы работы блока счетчика команд

- •Процедура чтения и выполнения команды:

- •Арифметико-логическое устройство

- •Арифметико-логическое устройство

- •Принцип работы арифметико-логического

- •Принцип работы арифметико-логического

- •Принцип работы арифметико-логического

- •Порты микроконтроллера

- •Порты микроконтроллера

- •Порты микроконтроллера

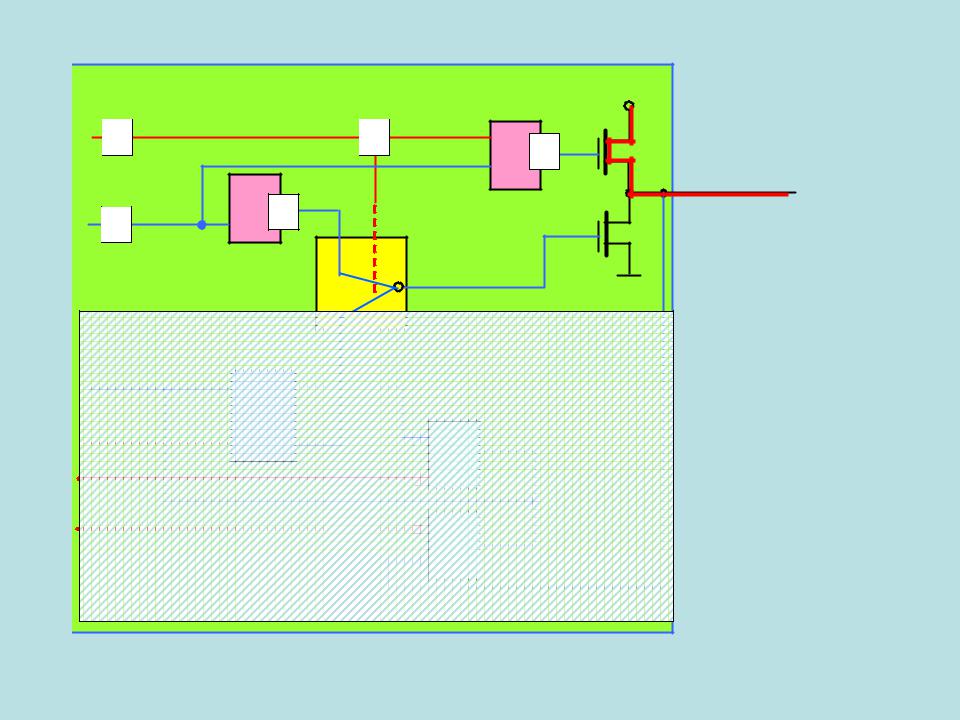

- •Структура разряда порта P0

- •Структура разряда порта P0

- •Организация памяти

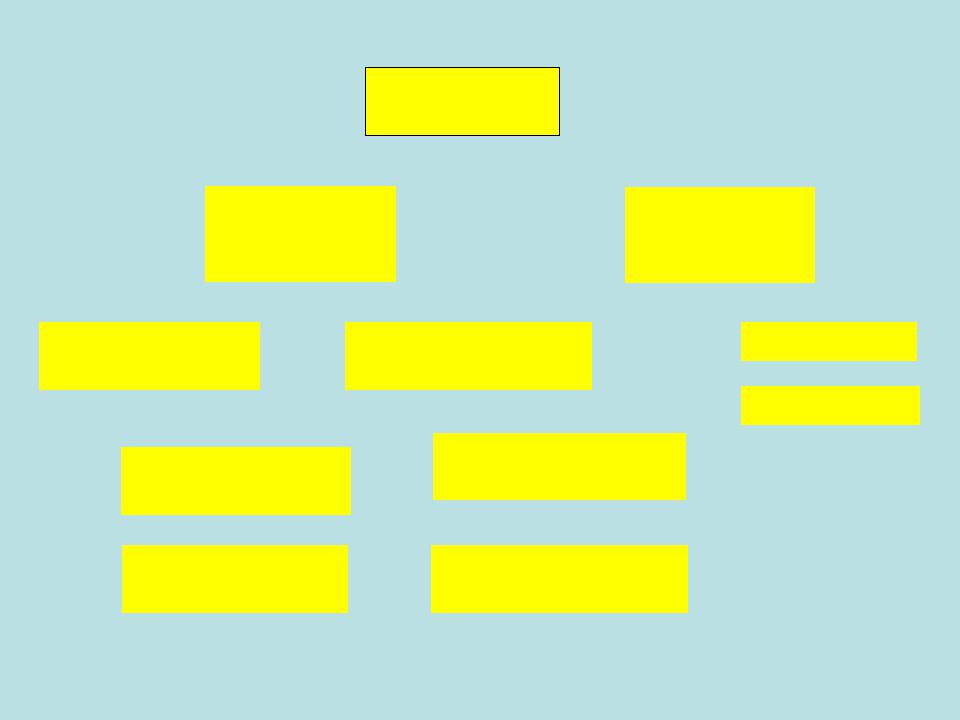

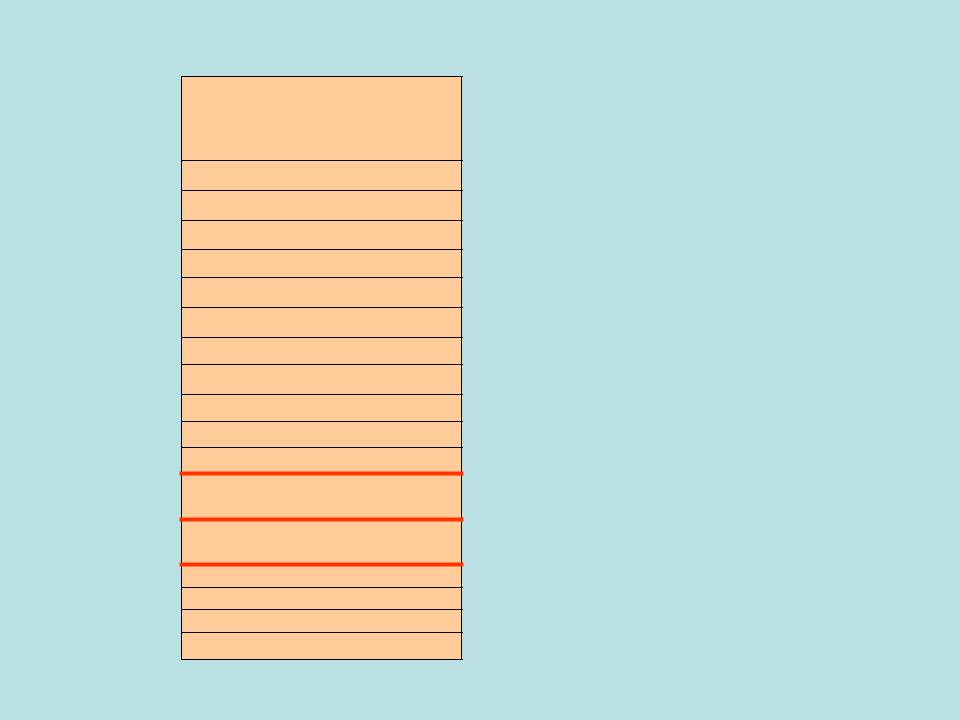

- •Классификация памяти микроконтроллера

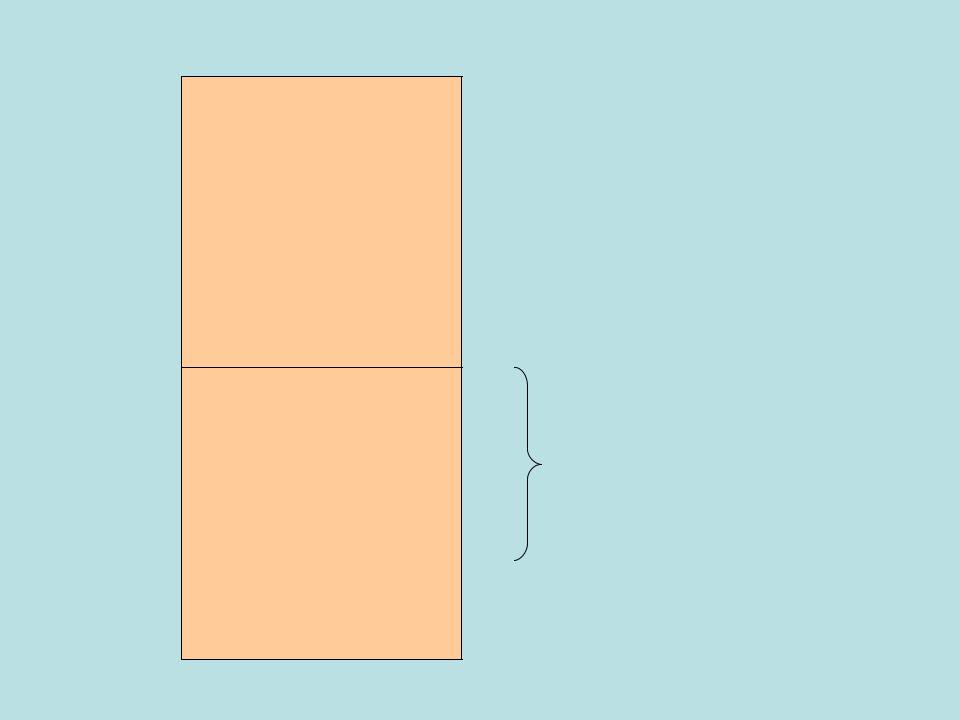

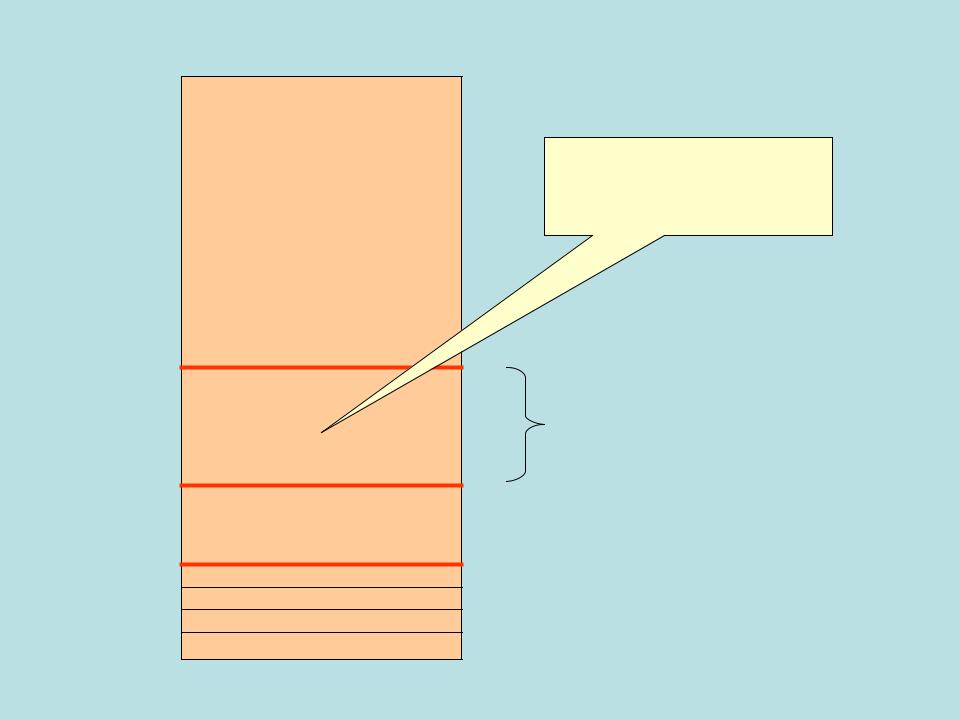

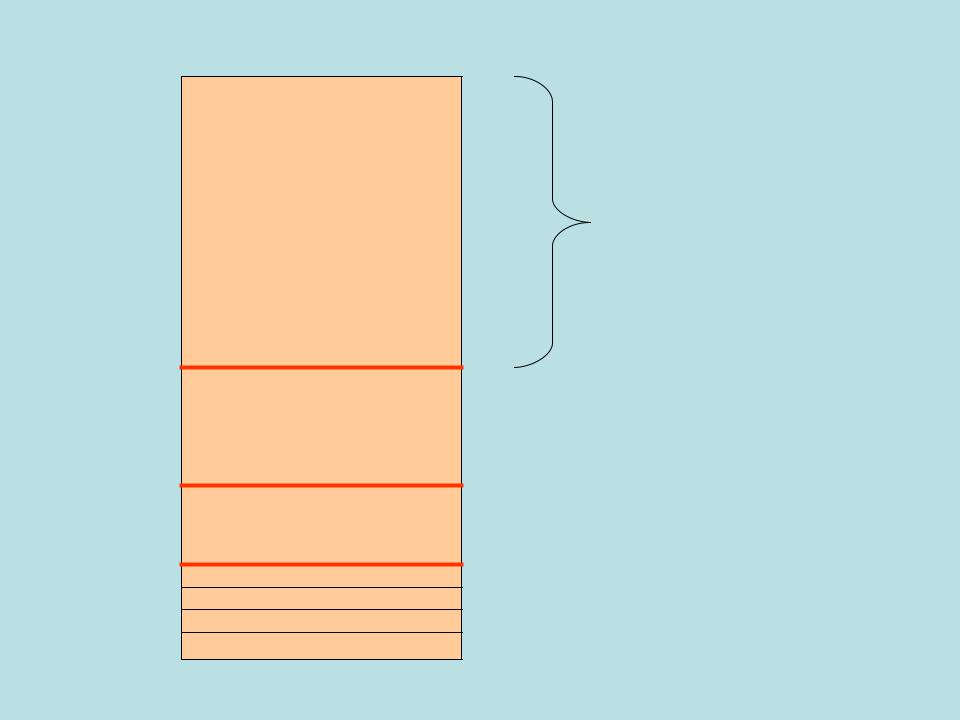

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

- •Структура памяти битового доступа

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

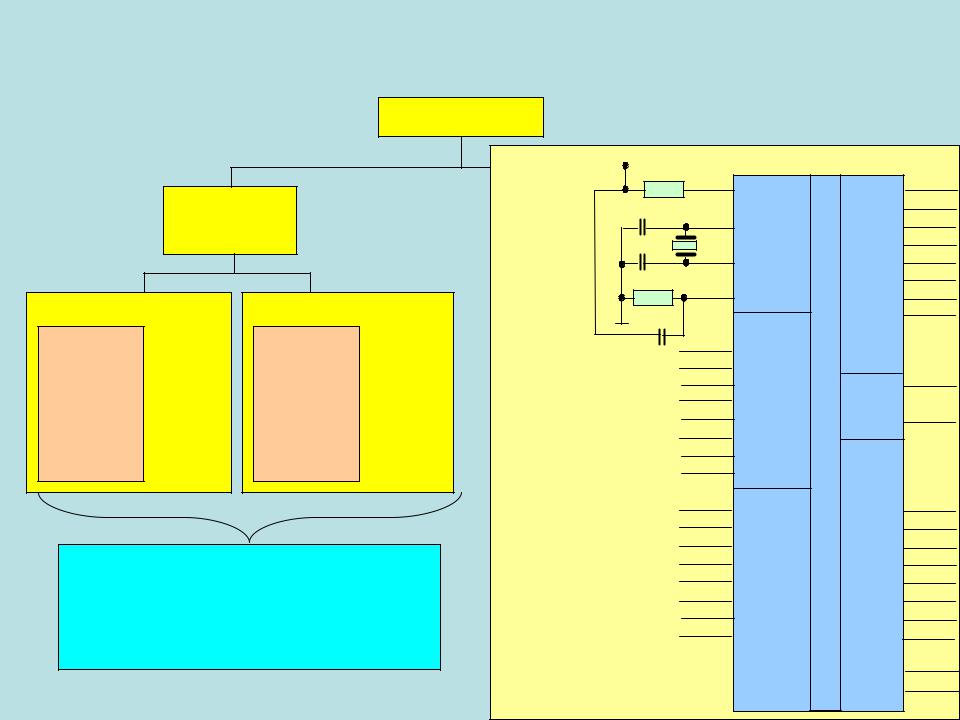

- •Подключение внешней памяти

- •Подключение внешней памяти программ

- •Подключение внешней памяти данных

- •Подключение внешней памяти программ и данных

- •Блок таймеров / счетчиков

- •Блок таймеров / счетчиков

- •Пример.Организация временных отметок

- •Пример.Организация временных отметок

- •Система прерываний

- •Система прерываний

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Структура блока прерываний микроконтроллера MCS-51

- •Настройка блока прерываний. Программирование типа запросов прерывания от

- •Настройка блока прерываний. Разрешение прерывания от

- •Настройка блока прерываний. Программирование приоритетов разрешенных прерываний. Таймер 0 и последовательный канал с

- •Прохождение запросов прерывания при поступлении по одному

- •Прохождение запросов прерывания разного уровня приоритета при одновременном поступлении

- •Прохождение запросов прерывания при одновременном поступлении двух запросов одного уровня приоритета

- •Процедура обработки прерывания (нет запроса)

- •Процедура обработки прерывания (поступление запроса)

- •Процедура обработки прерывания (запись содержимого счетчика

- •Процедура обработки прерывания (модификация адреса)

- •Процедура обработки прерывания (выполнение программы

- •Процедура обработки прерывания (восстановление сохраненного в

- •Блок последовательного канала (интерфейса)

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

Структура разряда порта P0 |

|

||||

|

|

|

|

5B |

|

Управление |

|

1 |

|

|

|

1 |

|

& 1 |

T1 |

|

|

|

|

|

5В |

||

|

1 0 |

|

|

Вывод |

|

Адрес / |

|

МХ |

P0.X |

(лог. 1) |

|

1 |

|

|

T2 |

|

|

данные |

|

|

|

|

|

Внутренняя |

|

|

|

|

|

шина данных Защелка |

|

|

|

|

|

|

D Q |

|

|

|

|

Запись |

_ |

|

B1 |

|

|

C Q |

|

|

|

||

|

|

|

|

||

Чтение защелки |

|

|

|

|

|

Чтение выводов |

|

B2 |

|

|

|

|

|

|

|

|

|

• Режим передачи адреса/данных |

|

||||

Структура разряда порта P0 |

|

||||

|

|

|

|

5B |

|

Управление |

|

1 |

|

|

|

1 |

|

& 0 |

T1 |

|

|

|

|

|

0В |

||

|

1 1 |

|

|

Вывод |

|

Адрес / |

|

МХ |

P0.X |

(лог. 0) |

|

0 |

|

|

T2 |

|

|

данные |

|

|

|

|

|

Внутренняя |

|

|

|

|

|

шина данных Защелка |

|

|

|

|

|

|

D Q |

|

|

|

|

Запись |

_ |

|

B1 |

|

|

C Q |

|

|

|

||

|

|

|

|

||

Чтение защелки |

|

|

|

|

|

Чтение выводов |

|

B2 |

|

|

|

|

|

|

|

|

|

• Режим передачи адреса/данных |

|

||||

Организация памяти

Запоминающие

устройства

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Постоянные |

|

|

|

|

|

Оперативные |

|

|

||||||||||

|

|

|

|

запоминающие |

|

|

|

|

|

запоминающие |

|

|

||||||||||

|

|

|

|

устройства |

|

|

|

|

|

устройства |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Однократно |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Статические |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

программируемые |

|

|

|

|

Репрограммируемые |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Динамические |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

С ультрафиолетовым |

|

|

|

|

||||||

|

|

Масочные |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

стиранием |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

Программируемые |

|

|

|

|

С электрическим |

|

|

|

|

|||||||||||

|

|

пользователем |

|

|

|

|

стиранием (FLASH) |

|

|

|

|

|

|

|||||||||

Классификация памяти микроконтроллера |

|

||||||

|

Память |

|

|

|

|

|

|

|

|

+5B |

|

DD1 |

|

|

|

|

|

R1 |

31 |

|

|

39 |

|

|

|

EA |

|

P0.0 |

|||

Память |

|

|

|||||

|

|

|

38 |

||||

C1 |

19 |

|

|

P0.1 |

|||

|

|

37 |

|||||

программ |

|

X1 |

|

P0.2 |

|||

|

|

|

36 |

||||

C2 |

18 |

|

|

P0.3 |

|||

|

|

X2 |

|

P0.4 |

35 |

||

|

|

|

|

|

34 |

||

|

|

R2 |

9 |

|

|

P0.5 |

|

|

|

|

|

33 |

|||

Внутренняя |

Внешняя |

RST |

|

P0.6 |

|||

|

|

|

32 |

||||

C3 |

|

|

|

P0.7 |

|||

|

|

|

|

||||

Адресное ХХХХ |

Адресное FFFF |

|

1 |

P1.0 |

|

|

|

простран- |

простран- |

|

2 |

P1.1 |

|

|

29 |

|

3 |

|

PSEN |

||||

ство |

ство |

|

4 |

P1.2 |

|

|

|

|

P1.3 |

|

|

30 |

|||

|

|

|

5 |

P1.4 |

|

ALE |

|

|

|

|

6 |

|

|

||

|

|

|

P1.5 |

|

|

|

|

|

|

|

7 |

|

|

|

|

0000 |

ХХХХ+1 |

|

P1.6 |

|

|

|

|

|

8 |

|

|

|

|||

|

P1.7 |

|

|

|

|||

|

|

|

|

|

|||

|

|

|

10 |

P3.0 |

RxD |

P2.0 |

21 |

|

|

|

11 |

22 |

|||

|

|

|

P3.1 |

TxD |

P2.1 |

||

|

|

|

12 |

23 |

|||

|

|

|

P3.2 INT0 |

P2.2 |

|||

Единое адресное пространство |

|

13 |

24 |

||||

|

P3.3 INT1 |

P2.3 |

|||||

|

14 |

25 |

|||||

при EA=1. Если EA=0, то исполь- |

|

P3.4 |

T0 |

P2.4 |

|||

|

15 |

26 |

|||||

|

P3.5 |

T1 |

P2.5 |

||||

зуется только внешняя память с |

|

16 |

P3.6 |

WR |

P2.6 |

27 |

|

|

17 |

28 |

|||||

|

P3.7 |

RD |

P2.7 |

||||

адресами от 0000 до FFFF. |

DD1 – 89C51 |

|

|

||||

|

|

|

|

40 |

|||

|

|

R1,R2 – С2-33 0.125Вт 8.2 кОм ±10% |

|

|

+5B |

||

|

|

С1, С2 – К10-17-1а 33пкФ±20% |

|

|

|

20 |

|

|

|

|

|

|

GND |

||

|

|

С3– К10-17-1а 10мкФ±20% |

|

|

|

||

|

|

|

|

|

|

|

|

Структура внутренней памяти данных

|

|

R7 |

07 |

R6 |

06 |

R5 |

05 |

R4 |

04 |

R3 |

03 |

R2 |

02 |

R1 |

01 |

Банк 0 РегистрыR0 R0-R7 |

00-07 |

Адресное

пространство

Банк регистров общего назначения 0

Структура внутренней памяти данных

FF

|

|

2F |

… |

|

|

|

|

22 |

|

|

|

|

|

21 |

|

|

20 |

|

|

18-1F |

Банк 3 Регистры R0-R7 |

||

Банк 2 Регистры R0-R7 |

10-17 |

|

Банк 1 Регистры R0-R7 |

08-0F |

|

Банк 0 Регистры R0-R7 |

00-07 |

|

Память с битовым доступом

Структура памяти битового доступа

7F |

7E |

7D |

7C |

7B |

7A |

79 |

78 |

|

|

|

|

|

|

|

|

…

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

|

|

|

|

|

|

|

|

0F |

0E |

0D |

0C |

0B |

0A |

09 |

08 |

|

|

|

|

|

|

|

|

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

|

|

|

|

|

|

|

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

|

|

Номер бита |

|

|

||

2F

22

21

20

Адрес ячейки

Абсолютный адрес бита

:

1.Как номер бита относительно адреса ячейки памяти Например 21h.3

2.Как абсолютный адрес бита Например 0Bh

21h.3 = 0Bh

Структура внутренней памяти данных

Память с битовым доступом

Банк 3 Регистры R0-R7

Банк 2 Регистры R0-R7

Банк 1 Регистры R0-R7

Банк 0 Регистры R0-R7

FF

Используется обычная байтовая адресация

доступом

30

2F

20

18-1F

10-17

08-0F

00-07

Структура внутренней памяти данных

Память с байтовым доступом

Память с битовым доступом

Банк 3 Регистры R0-R7

Банк 2 Регистры R0-R7

Банк 1 Регистры R0-R7

Банк 0 Регистры R0-R7

FF

Зона регистров специального назначения

80

7F

30

2F

20

18-1F

10-17

08-0F

00-07

Структура внутренней памяти данных

B

A

PSW

IP

P3

IE

P2

SCON

P1

TCON

P0

Память с байтовым доступом

Память с битовым доступом

Банк 3 Регистры R0-R7

Банк 2 Регистры R0-R7

Банк 1 Регистры R0-R7

Банк 0 Регистры R0-R7

FF

F0

E0

D0

B8

B0

A8

A0

98

90

88

80

7F

30

2F

20

18-1F

10-17

08-0F

00-07

Кроме того, еще регистры

SBUF, TMOD, TH0, TL0, TH1, TL1