- •Понятие о микропроцессорах и

- •Понятие о микропроцессорах и микроконтроллерах

- •Понятие о микропроцессорах и микроконтроллерах

- •Шинная организация. Характеристики шин.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

- •Шинная организация. Характеристики шин для микроконтроллеров семейства MCS-51.

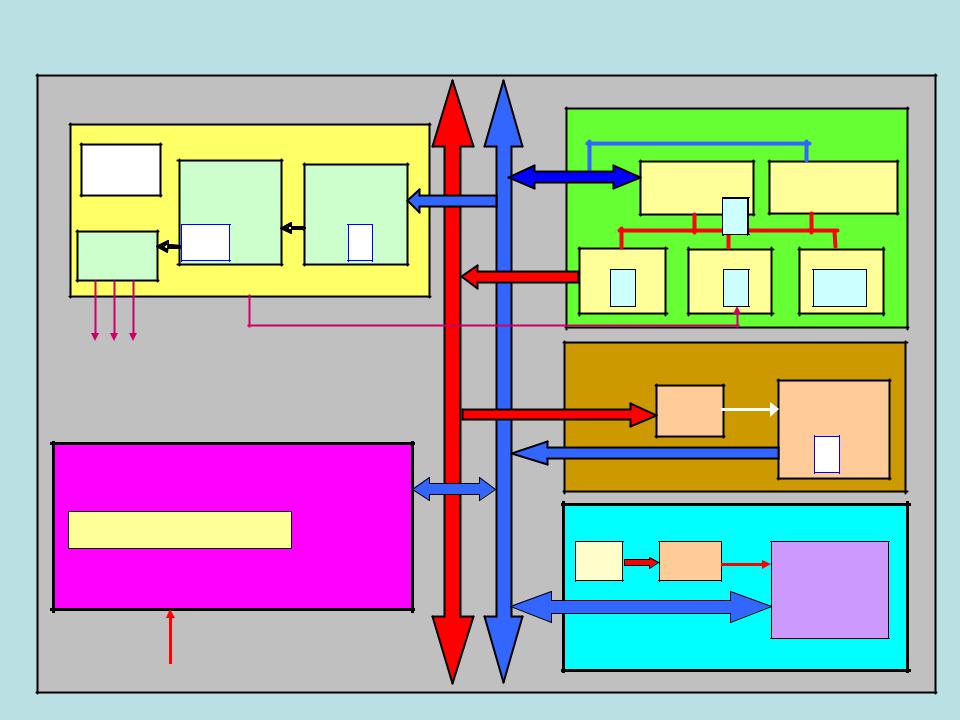

- •Структура микроконтроллера семейства MCS-51

- •Структура микроконтроллера семейства MCS-51

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Назначение блоков микроконтроллера

- •Блок управления

- •Функции блока управления:

- •Функции блока управления:

- •Структура блока счетчика команд (СК)

- •Режимы работы блока счетчика команд

- •Процедура чтения и выполнения команды:

- •Арифметико-логическое устройство

- •Арифметико-логическое устройство

- •Принцип работы арифметико-логического

- •Принцип работы арифметико-логического

- •Принцип работы арифметико-логического

- •Порты микроконтроллера

- •Порты микроконтроллера

- •Порты микроконтроллера

- •Структура разряда порта P0

- •Структура разряда порта P0

- •Организация памяти

- •Классификация памяти микроконтроллера

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

- •Структура памяти битового доступа

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

- •Структура внутренней памяти данных

- •Подключение внешней памяти

- •Подключение внешней памяти программ

- •Подключение внешней памяти данных

- •Подключение внешней памяти программ и данных

- •Блок таймеров / счетчиков

- •Блок таймеров / счетчиков

- •Пример.Организация временных отметок

- •Пример.Организация временных отметок

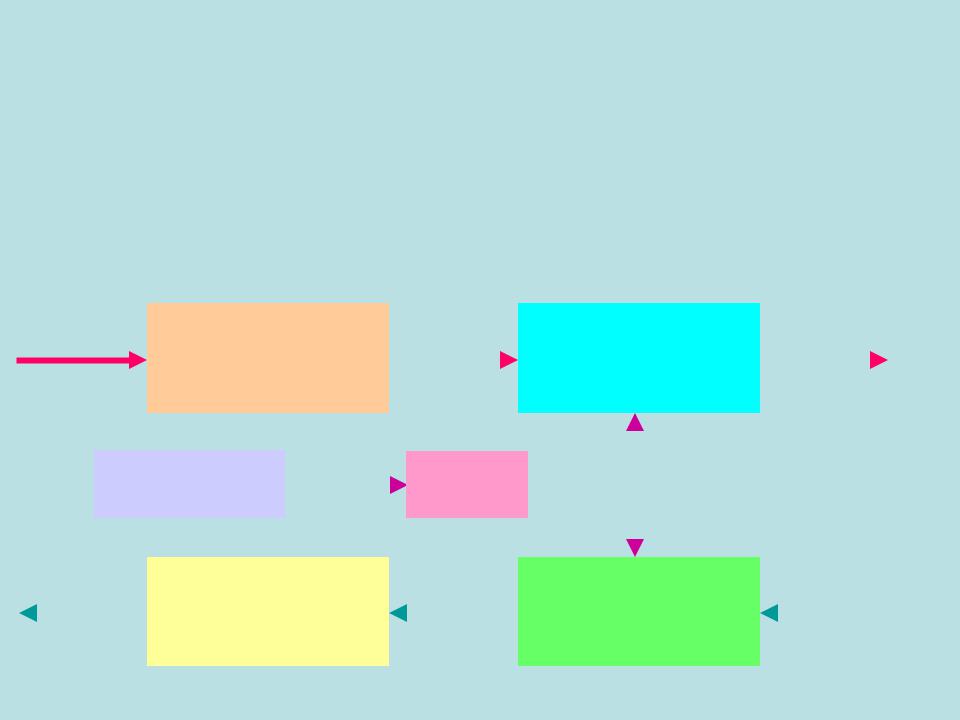

- •Система прерываний

- •Система прерываний

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Блок прерываний микроконтроллера MCS-51

- •Структура блока прерываний микроконтроллера MCS-51

- •Настройка блока прерываний. Программирование типа запросов прерывания от

- •Настройка блока прерываний. Разрешение прерывания от

- •Настройка блока прерываний. Программирование приоритетов разрешенных прерываний. Таймер 0 и последовательный канал с

- •Прохождение запросов прерывания при поступлении по одному

- •Прохождение запросов прерывания разного уровня приоритета при одновременном поступлении

- •Прохождение запросов прерывания при одновременном поступлении двух запросов одного уровня приоритета

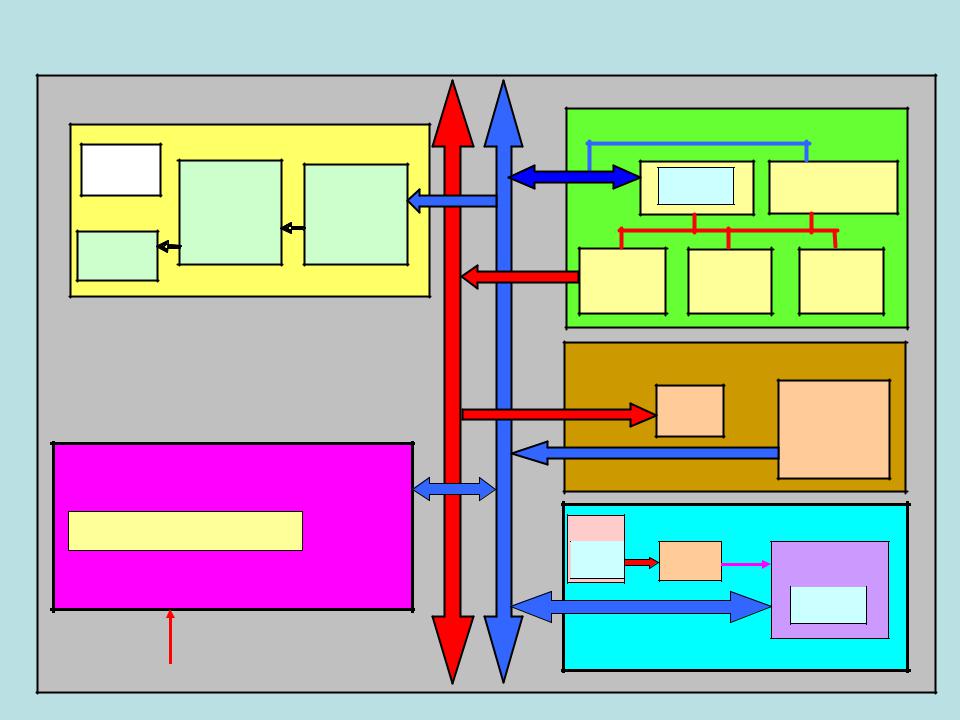

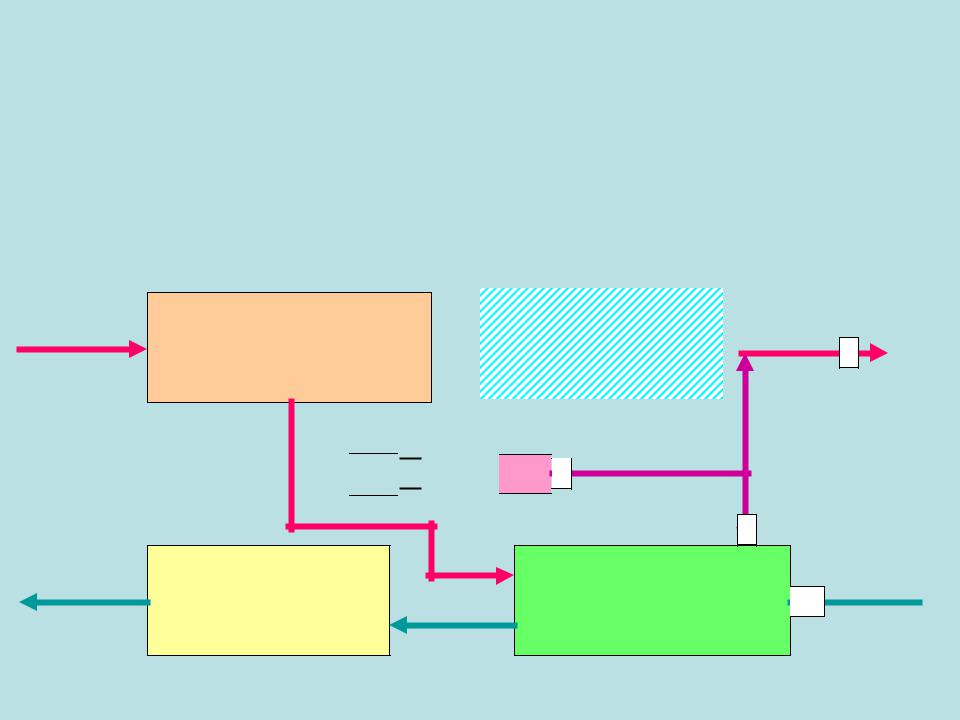

- •Процедура обработки прерывания (нет запроса)

- •Процедура обработки прерывания (поступление запроса)

- •Процедура обработки прерывания (запись содержимого счетчика

- •Процедура обработки прерывания (модификация адреса)

- •Процедура обработки прерывания (выполнение программы

- •Процедура обработки прерывания (восстановление сохраненного в

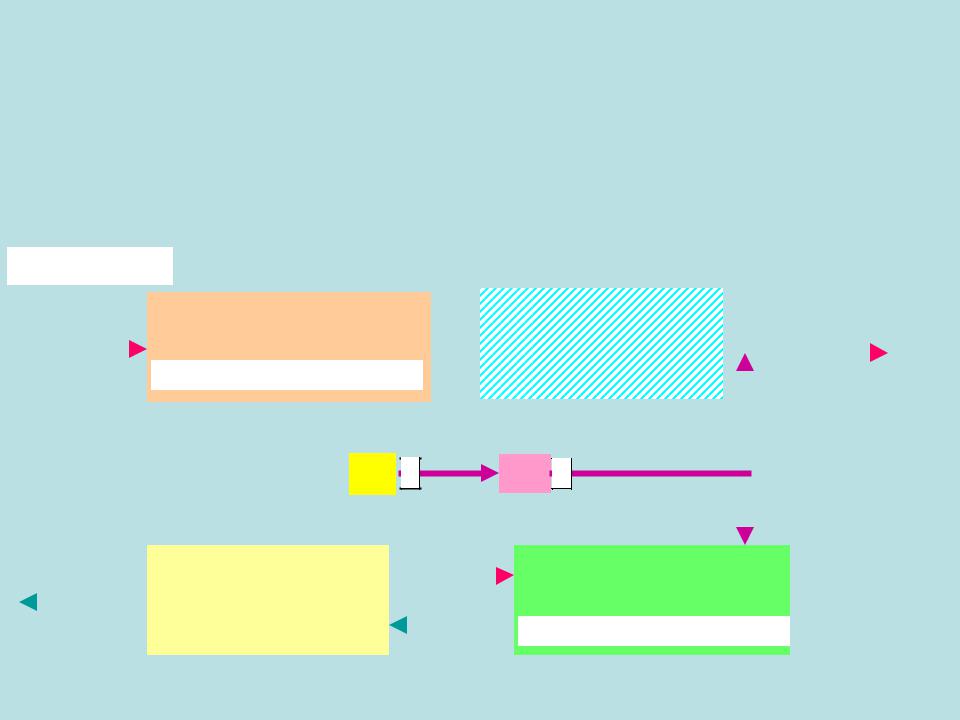

- •Блок последовательного канала (интерфейса)

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

- •Блок последовательного канала

Процедура обработки прерывания (выполнение программы |

||||||

|

|

обработки прерывания) |

|

|

|

|

|

|

ША |

ШД |

|

|

|

|

Блок управления |

Блок счетчика команд |

||||

ГТИ |

|

|

Буфер |

Указатель |

||

Дешиф- |

Регистр |

|

|

|||

|

|

|

||||

|

ратор |

команд |

|

|

А |

|

ПЛМ |

Д24 |

Д |

РА |

СК |

А+1+ |

|

|

|

|

||||

|

Сигнал |

А |

|

А |

||

|

|

|

|

|

||

Управл. |

управления |

|

Память программ |

|||

|

|

|

||||

сигналы |

|

|

|

|

ДШ |

Ячейки |

|

|

|

|

|

||

|

|

|

|

|

|

памяти |

Блок прерываний |

|

|

|

Д |

||

Запрет прерывания |

|

|

|

Память данных |

||

|

|

|

SP |

|

ДШ |

Ячейки |

|

|

|

|

|

|

памяти |

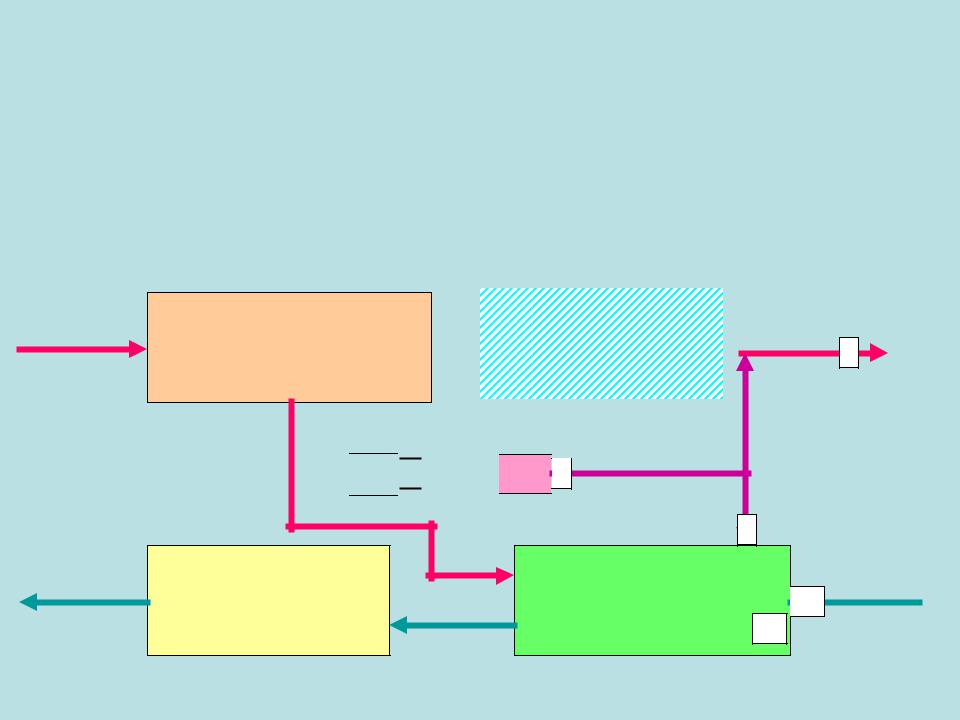

Процедура обработки прерывания (восстановление сохраненного в |

|||||

|

стеке адреса в счетчик команд по команде RETI) |

||||

|

|

ША |

ШД |

|

|

|

Блок управления |

Блок счетчика команд |

|||

ГТИ |

|

|

Указатель |

||

Дешиф- |

Регистр |

|

А+1 |

||

|

|

||||

|

ратор |

команд |

|

|

|

ПЛМ |

|

|

РА |

СК |

+ |

|

|

|

|||

|

|

|

Память программ |

||

|

|

|

|

ДШ |

Ячейки |

Блок прерываний |

|

|

памяти |

||

|

|

|

|||

Запрет прерывания |

|

SP |

Память данных |

||

|

|

|

А+2 |

ДШ |

Ячейки |

|

|

|

|

|

памяти |

|

|

|

|

|

А+1ст |

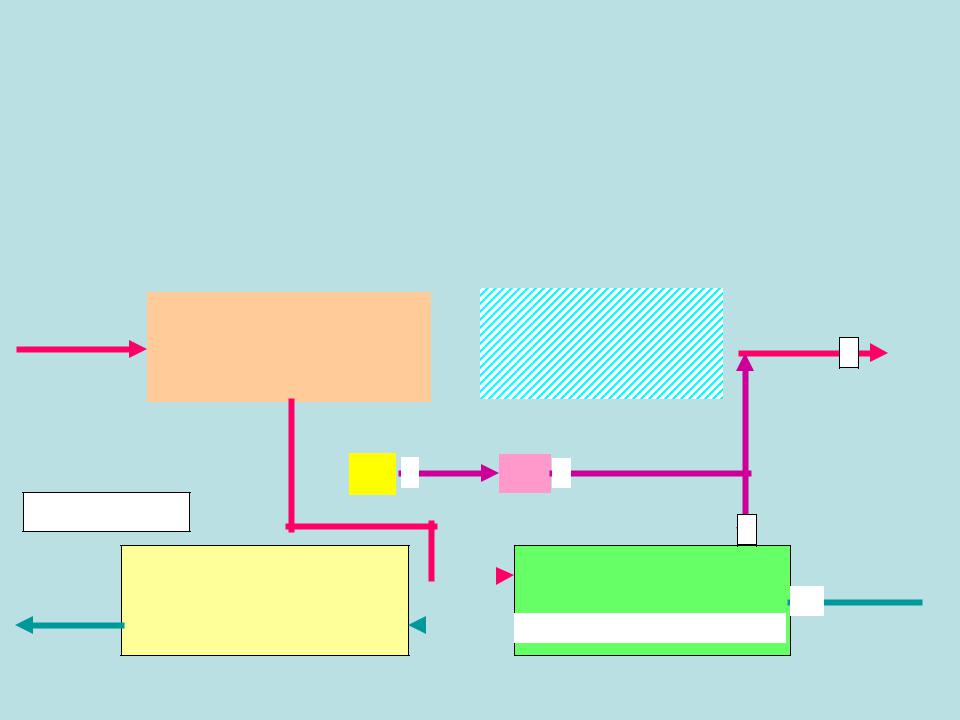

Блок последовательного канала (интерфейса)

•Блок последовательного интерфейса (ПИ) предназначен для организации ввода-вывода последовательных потоков информации с возможностью дуплексного включения (возможность одновременного приема и передачи данных). ПИ может работать в четырех режимах.

Общая структура каналов приема передачи

MOV SBUF,A

Буферный регистр |

|

|

Сдвиговый регистр |

TхD ( Р3.1) |

|

передатчика SBUF |

|

|

передатчика |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Импульсы |

|

|

Делитель |

|

|

|

|

|

|

|||

|

|

синхронизации |

|

|

|

частоты |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

MOV A,SBUF |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

Буферный регистр |

|

|

Сдвиговый регистр |

|

RхD ( Р3.0) |

||||||

|

|

|

приемника SBUF |

|

|

приемника |

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок последовательного канала

•Режим 0. Информация выдается и принимается через вход приемника RxD. Через выход передатчика ТхD выдаются импульсы синхронизации, стробирующие каждый передаваемый или принимаемый бит информации. Формат посылки – 8 бит. Частота приема и передачи – fBQ/12.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Передача |

|

|

|

||||||||

MOV SBUF,A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр |

|

Сдвиговый регистр |

|

|

TхD ( Р3.1) |

||||||||||||||||||||||||||

|

|

|

|

|

передатчика SBUF |

|

передатчика |

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fBQ |

1 |

|

|

|

:12 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр |

|

|

|

|

|

|

|

|

|

Сдвиговый регистр |

RхD ( Р3.0) |

||||||||||||||||||||

|

|

|

|

|

приемника SBUF |

|

|

|

|

|

|

|

|

|

приемника |

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок последовательного канала

• Режим 0. Передача

MOV SBUF,A |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр |

|

Сдвиговый регистр |

|

|

|

|

передатчика SBUF |

|

передатчика |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fBQ |

|

|

|

:12 |

|

|

|

1 |

|

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр приемника SBUF

1 |

Сдвиговый регистр приемника

D7

D7  D6 D5 D4 D3 D2 D1

D6 D5 D4 D3 D2 D1

TхD ( Р3.1)

1

RхD ( Р3.0)

D0

Блок последовательного канала

• Режим 0. Передача

MOV SBUF,A |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр |

|

Сдвиговый регистр |

|

|

|

|

передатчика SBUF |

|

передатчика |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fBQ |

|

|

|

:12 |

|

|

|

1 |

|

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Буферный регистр приемника SBUF

1 |

Сдвиговый регистр приемника

D7

D7  D6 D5 D4 D3 D2

D6 D5 D4 D3 D2

TхD ( Р3.1)

1

RхD ( Р3.0)

D1

Блок последовательного канала

• Режим 0. Прием

Буферный регистр передатчика SBUF

fBQ

1

1

Буферный регистр приемника SBUF

Сдвиговый регистр |

|

TхD ( Р3.1) |

|

передатчика |

|

1 |

|

|

|

|

|

|

|

|

|

:12

:12

0

0

1 |

Сдвиговый регистр приемника

RхD ( Р3.0)

D0

Блок последовательного канала

• Режим 0. Прием

Буферный регистр передатчика SBUF

fBQ

1

1

Буферный регистр приемника SBUF

Сдвиговый регистр |

|

TхD ( Р3.1) |

|

передатчика |

|

1 |

|

|

|

|

|

|

|

|

|

:12

:12

0

0

1 |

Сдвиговый регистр приемника

D0

RхD ( Р3.0)

D1

Блок последовательного канала

• Режим 0. Прием

Буферный регистр передатчика SBUF

fBQ

1

1

Буферный регистр приемника SBUF

Сдвиговый регистр |

|

TхD ( Р3.1) |

|

передатчика |

|

1 |

|

|

|

|

|

|

|

|

|

:12

:12

0

0

1 |

Сдвиговый регистр приемника

D1  D0

D0

RхD ( Р3.0)

D2

Блок последовательного канала

• Режим 0. Прием

|

|

Сдвиговый регистр |

|

|

|

Буферный регистр |

|

|

TхD ( Р3.1) |

||

передатчика SBUF |

|

передатчика |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fBQ |

|

|

|

:12 |

|

|

|

1 |

|

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MOV A,SBUF |

1 |

|

Буферный регистр |

|

|

Сдвиговый регистр |

|

RхD ( Р3.0) |

||||||||

приемника SBUF |

|

|

приемника |

|

|

||||||||

|

|

D7 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|