- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Содержание

- •Тема1. Формы представления информации 10

- •Тема 2. Логические основы построения элементов 16

- •Тема 3. Схемотехника комбинационных узлов 29

- •Тема 4. Схемотехника цифровых элементов 70

- •Тема 5. Схемотехника цифровых узлов 108

- •Тема 6. Интегрированные системы элементов 138

- •Тема 7. Схемотехника аналоговых узлов 179

- •Тема 8. Схемотехника обслуживающих элементов 208

- •Тема 14. Структуры микропроцессорных систем 293

- •Тема 15. Схемы поддержки мп на системных платах 340

- •Тема 16. Некоторые вопросы развития архитектуры эвм 357

- •Тема 17. Risk – процессоры 387

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы 399

- •Список литературы 450 Тема1. Формы представления информации Лекция 1. Основные понятия

- •Тема 2. Логические основы построения элементов Лекция 2.

- •2.1. Основные понятия, определения и законы Булевой алгебры

- •Формы задания Булевой функции

- •2.2. Простейшие модели логических элементов и система их параметров

- •2.3. Типы выходных каскадов цифровых элементов

- •2.4. Системы (серии) логических элементов и их основные характеристики

- •2.5 Контрольные вопросы

- •Тема 3. Схемотехника комбинационных узлов Лекция 3

- •3.1 Общие сведения

- •3.2. Шифраторы, дешифраторы и преобразователи кодов: назначения, виды, функционирование, принципы построения

- •3.3. Синтез кс на основе дешифраторов

- •3.4. Мультиплексоры и демультиплексоры

- •3.5. Шинные формирователи

- •3.6 Синтез кс на основе мультиплексоров

- •3.7. Компараторы

- •3.8 Сумматоры

- •3.9. Арифметико-логические устройства

- •3.10. Матричные умножители

- •3.11 Постановка и методы решения задач синтеза комбинационных узлов

- •3.11.1 Синтез комбинационных узлов

- •3.11.2 Основные факторы, которые должны быть учтены при построении принципиальных схем

- •3.11.2.1 Питающие напряжения ис

- •3.11.2.2 Уровни логических сигналов

- •3.11.2.3 Нагрузочная способность

- •3.11.2.4 Коэффициент объединения по входу

- •3.11.2.5 Быстродействие

- •3.11.2.6 Помехоустойчивость

- •3.11.2.7 Рассеиваемая мощность

- •3.11.2.8. Использование элементов, имеющих выходы с третьим состоянием или с открытым коллектором

- •3.12 Критерии оценки качества технической реализации кс

- •3.13 Контрольные вопросы

- •Тема 4. Схемотехника цифровых элементов Лекция 4

- •4.1 Последовательностные цифровые схемы

- •4.2. Схемотехника триггерных устройств

- •4.3. Асинхронные триггеры

- •4.4. Синхронные триггеры

- •Rs триггер с синхронизацией по уровню

- •Синхронный rs триггер с синхронизацией по фронту

- •4.5 Методы построения триггеров одного типа на базе триггеров другого типа

- •Проектирование триггеров на основе rs-триггера

- •Метод преобразования характеристических уравнений

- •Метод сравнения характеристических уравнений

- •Использование jk-триггера

- •4.6 Регистры и регистровые файлы

- •4.6.1 Регистры памяти

- •4.6.2 Сдвигающие регистры

- •4.6.3 Универсальные регистры

- •4.7 Счётчики

- •4.7.1 Счетчики с непосредственными связями и последовательным переносом

- •4.7.2 Счетчики с параллельным переносом

- •4.7.3 Реверсивный счетчик с последовательным переносом

- •4.7.4 Двоично-кодированные счётчики с произвольным модулем

- •Построение счетчика методом модификации межразрядных связей

- •Построение счетчика методом управления сбросом

- •4.8 Распределители тактов

- •4.8.1 Распределители импульсов и распределители уровней

- •4.8.2 Кольцевой регистр сдвига

- •4.8.3 Счётчик Джонсона

- •4.9 Контрольные вопросы

- •Тема 5. Схемотехника цифровых узлов Лекция 5

- •5.1 Цифровые автоматы и их разновидности

- •5.2 Абстрактный и структурный автоматы

- •5.3. Способы описания и задания автоматов

- •5.4. Связь между моделями Мура и Мили

- •5.5. Минимизация числа внутренних состояний полностью определенных автоматов

- •5.6. Принцип микропрограммного управления. Понятия об операционном и управляющем автоматах

- •Операционные элементы

- •5.7. Граф - схемы алгоритмов (гса) и их разновидности. Способы задания гса, требования к ним

- •5.8. Абстрактный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.8.1. Синтез автомата Мили

- •5.8.2. Синтез автомата Мура

- •5.9. Структурный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.9.1. Структурный синтез автомата Мили

- •5.9.2. Структурный синтез автомата Мура

- •5.10. Синтез автомата Мура на базе регистра сдвига

- •5.11. Контрольные вопросы

- •Тема 6. Интегрированные системы элементов Лекция 6. Программируемые логические устройства

- •6.1 Основные физические принципы программирования плм и плис

- •6.1.1 Метод плавких перемычек

- •6.1.2 Метод наращиваемых перемычек

- •6.1.3 Устройства, программируемые фотошаблоном

- •6.1.4 Стираемые программируемые постоянные запоминающие устройства

- •6.1.5. Электрически стираемые программируемые постоянные запоминающие устройства

- •6.1.6. Flash - технология

- •6.1.7. Статическое оперативное запоминающее устройство

- •6.1.8. Сравнительная таблица технологий программирования

- •6.2 Простые и сложные плу

- •6.2.1 Ппзу

- •6.2.2 Программируемые логические матрицы

- •6.2.3. Программируемые матрицы pal и gal

- •6.2.4 Дополнительные программируемые опции

- •6.2.5 Сложные плу

- •6.3. Контрольные вопросы

- •Лекция 7. Программируемые логические интегральные схемы

- •7.1 Мелко-, средне- и крупномодульные архитектуры

- •7.2 Логические блоки на мультиплексорах и таблицах соответствия

- •7.3 Таблицы соответствия, распределённое озу, сдвиговые регистры

- •7.4 Конфигурируемые логические блоки, блоки логических символов, секции

- •7.5 Секции и логические ячейки

- •7.6 Конфигурируемые логические блоки clb и блоки логических массивов lab

- •7.7. Контрольные вопросы

- •Лекция 8

- •8.1 Дополнительные встроенные функции

- •8.1.1 Схемы ускоренного переноса

- •8.1.2 Встроенные блоки озу

- •8.1.3 Встроенные умножители, сумматоры и блоки умножения с накоплением

- •8.1.4 Аппаратные и программные встроенные микропроцессорные ядра

- •8.2 Дерево синхронизации и диспетчеры синхронизации

- •8.2.1 Дерево синхронизации

- •8.2.2 Диспетчер синхронизации

- •8.3. Системы с перестраиваемой архитектурой

- •8.4. Программируемый пользователем массив узлов

- •8.4.1. Технология picoArray компании picoChip

- •8.4.2 Технология адаптивных вычислительных машин компании QuickSilver

- •8.5. Контрольные вопросы

- •Тема 7. Схемотехника аналоговых узлов Лекция 9. Операционные усилители

- •9.1. Идеальный операционный усилитель

- •9.2. Основные схемы включения операционного усилителя

- •9.2.1. Дифференциальное включение

- •9.2.2. Инвертирующее включение

- •9.2.3 Неинвертирующее включение

- •9.3 Функциональные устройства на операционных усилителях

- •9.3.1 Схема масштабирования

- •9.3.2 Схема суммирования

- •9.3.3 Схема интегрирования

- •9.3.4 Схема дифференцирования

- •9.3.5 Источники напряжения, управляемые током

- •9.3.6 Источники тока, управляемые напряжением

- •9.4 Активные электрические фильтры на оу

- •9.5 Схемы нелинейного преобразования на оу

- •9.6 Генераторы сигналов на оу

- •9.7. Контрольные вопросы

- •Лекция 10

- •10.1. Изолирующие усилители

- •10.2. Аналоговые компараторы

- •10.3. Источники опорного напряжения

- •10.4. Аналоговые коммутаторы

- •10.5. Оптореле

- •10.6. Устройства выборки-хранения

- •10.7. Цифроаналоговые преобразователи

- •10.8. Аналого-цифровые преобразователи

- •10.9. Контрольные вопросы

- •Тема 8. Схемотехника обслуживающих элементов Лекция 11

- •11.1 Сопряжение цифровых микросхем, изготовленных по разным технологиям, и сопряжение с интерфейсами

- •11.2 Управление входами ттл и кмоп

- •11.3 Дискретное управление нагрузкой от элементов ттл и кмоп

- •11.4 Передача цифровых сигналов на небольшие расстояния

- •11.5 Контрольные вопросы

- •Тема 9. Источники питания. Схемотехника комбинаторных узлов Лекция 12

- •12.1. Схемотехника линейных стабилизаторов напряжения

- •12.2 Импульсные стабилизаторы напряжения

- •12.3 Инверторные схемы

- •12.4 Контрольные вопросы

- •Тема10. Цифровые компьютеры Лекция 13

- •13.1. Принципы действия цифровых компьютеров

- •13.2. Понятие о системе программного (математического) обеспечения эвм

- •13.3. Большие эвм общего назначения

- •13.3.1. Каналы

- •13.3.2. Интерфейс

- •13.4. Малые эвм

- •13.5. Контрольные вопросы

- •Тема 11. Запоминающие устройства Лекция 14

- •14.1 Структура памяти эвм

- •14.2 Способы организации памяти

- •14.2.1 Адресная память

- •14.2.2 Ассоциативная память

- •14.2.3 Стековая память (магазинная)

- •14.3. Структуры адресных зу

- •14.3.1. Зу типа 2d

- •14.3.2. Зу типа 3d

- •14.3.3. Зу типа 2d-m

- •14.4 Постоянные зу (пзу, ппзу)

- •14.5. Флэш-память

- •14.6. Контрольные вопросы

- •Тема 12. Процессоры Лекция 15

- •15.1 Операционные устройства (алу)

- •15.2 Управляющие устройства

- •15.2.1. Уу с жёсткой логикой

- •15.2.2 Уу с хранимой в памяти логикой

- •15.2.2.1. Выборка и выполнение мк

- •15.2.2.2. Кодирование мк

- •15.2.2.3. Синхронизация мк

- •15.3. Контрольные вопросы

- •Тема 13. Универсальные микропроцессоры Лекция 16. Архитектура процессора кр580вм80

- •16.1. Регистры данных

- •16.2. Арифметико-логическое устройство

- •16.3. Регистр признаков

- •16.4. Блок управления

- •16.5. Буферы

- •16.6. Мп с точки зрения программиста

- •16.7. Форматы данных в кр580вм80

- •16.8. Форматы команд в кр580вм80

- •16.9. Способы адресации

- •16.10. Контрольные вопросы

- •Лекция 17. Система команд кр580вм80

- •17.1. Пересылки однобайтовые

- •17.2. Пересылки двухбайтовые

- •17.3. Операции в аккумуляторе

- •17.4. Операции в рон и памяти

- •17.5. Команды управления

- •17.6. Контрольные вопросы

- •Тема 14. Структуры микропроцессорных систем Лекция 18. Общие принципы

- •18.1. Системный интерфейс микро-эвм. Цикл шины

- •18.2. Промежуточный интерфейс

- •18.3. Принципы организации ввода/вывода информации в микропроцессорную систему

- •18.4. Контрольные вопросы

- •Лекция 19. Принципы организации систем прерывания программ

- •19.1. Характеристики систем прерывания

- •19.2. Возможные структуры систем прерывания

- •19.3. Организация перехода к прерывающей программе

- •19.3.1. Реализация фиксированных приоритетов

- •19.3.2. Реализация программно-управляемых приоритетов

- •19.4. Контрольные вопросы

- •Лекция 20. Принципы организации систем прямого доступа в память

- •20.1. Способы организации доступа к системной магистрали

- •20.2. Возможные структуры систем пдп

- •20.3. Организация обмена в режиме пдп

- •20.3.1. Инициализация средств пдп

- •20.3.2. Радиальная структура ( Slave dma)

- •20.3.3. Радиальная структура (Bus master dma)

- •20.3.4. Цепочечная структура ( Bus master dma)

- •20.3.5. Принципы организации арбитража магистрали

- •20.4. Микропроцессорная система на основе мп кр580вм80а

- •20.5. Контрольные вопросы

- •Тема 15. Схемы поддержки мп на системных платах Лекция 21

- •21.1. Эволюция шинной архитектуры ibm pc

- •21.1.1. Локальная системная шина

- •21.1.2. Шина расширения

- •21.1.2.1. Шина расширения isa

- •21.1.2.2. Шина расширения mca

- •21.1.2.3. Шина расширения eisa

- •21.1.3. Локальные шины расширения

- •21.1.3.1. Локальная шина vesa (vlb)

- •21.1.3.2. Локальная шина pci

- •21.2. Современные схемы поддержки мп на системных платах

- •21.2.1. Чипсет GeForce 9300/9400 фирмы nvidia

- •21.2.3. Чипсет Intel z68 для платформы Socket 1155

- •21.3. Контрольные вопросы

- •Тема 16. Некоторые вопросы развития архитектуры эвм Лекция 22

- •22.1. Теги и дескрипторы. Самоопределяемые данные

- •22.2. Методы оптимизации обмена процессор-память

- •22.2.1. Конвейер команд

- •22.2.2. Расслоение памяти

- •22.2.3. Буферизация памяти

- •22.3. Динамическое распределение памяти. Виртуальная память

- •22.3.1. Виртуальная память

- •22.3.2. Сегментно-страничная организация памяти

- •22.4. Контрольные вопросы

- •Лекция 23. Защита памяти

- •23.1. Защита отдельных ячеек памяти

- •23.2. Метод граничных регистров

- •23.3. Метод ключей защиты

- •23.4. Алгоритмы управления многоуровневой памятью

- •23.5. Контрольные вопросы

- •Тема 17. Risk – процессоры Лекция 24

- •24.1. Общая характеристика risk - процессоров

- •24.2. Arm архитектура

- •24.2.1. Дополнительные технологии

- •24.2.2. Ядро arm7tdmi

- •24.2.3. Семейство arm10 Tumb

- •24.3. Контрольные вопросы

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы Лекция 25

- •25.1. Смена приоритетов в области высокопроизводительных вычислений

- •25.2. Сферы применения многоядерных процессоров и многопроцессорных вычислительных систем

- •25.3. Классификация архитектур вычислительных систем по степени параллелизма обработки данных

- •25.4. Архитектуры smp, mpp и numa

- •25.5. Организация когерентности многоуровневой иерархической памяти

- •25.6. Pvp архитектура

- •25.7. Контрольные вопросы

- •Лекция 26. Кластерная архитектура

- •26.1. Архитектура связи в кластерных системах

- •26.2. Коммутаторы для многопроцессорных вычислительных систем.

- •26.2.1. Простые коммутаторы

- •26.2.2. Составные коммутаторы

- •26.2.2.1. Коммутатор Клоза

- •26.3. Контрольные вопросы

- •Лекция 27. Высокопроизводительные многоядерные процессоры для встраиваемых приложений

- •27.1. Процессоры Tile-64/64Pro компании Tilera

- •27.4. Мультипроцессор Cell

- •27.4.1. Общая структура процессора Cell

- •27.4.2. Структура процессорного элемента Power (ppe)

- •27.4.3. Структура spe — "синергичного" процессорного элемента

- •27.5. Альтернативная технология построения многоядерных систем на кристалле — atac

- •27.5.1. Основные идеи архитектуры atac

- •27.5.2. Ключевые элементы технологии атас

- •27.5.3. Структура межъядерных связей

- •27.5.4. Передача данных и согласование кэш-памяти

- •27.6. Контрольные вопросы

- •Список литературы

26.3. Контрольные вопросы

1. Кластерная архитектура.

2. Архитектура связи в кластерных системах.

3. Типы простых коммутаторов для многопроцессорных вычислительных систем.

4. Составные коммутаторы для многопроцессорных вычислительных систем.

5. Коммутатор Клоза.

6. Баньян-сети.

7. Граф межмодульных связей Convex Exemplar SPP1000.

8. Структурный модуль МВС-100.

9. Варианты объединения структурных модулей МВС-100.

10. Структура 128-процессорной системы МВС-1000, 4 базовых блока.

Лекция 27. Высокопроизводительные многоядерные процессоры для встраиваемых приложений

27.1. Процессоры Tile-64/64Pro компании Tilera

Процессоры Tile64 рассчитаны на применение в высокопроизводительном сетевом оборудовании, беспроводных телекоммуникационных системах, а также серверах для потоковой обработки видеоданных. Позволяют использовать во встраиваемых приложениях мощные вычислительные ресурсы при достаточно низких энергозатратах.

Круг целевых задач для данных процессоров следующий.

Процессоры способны работать в сетях с уровнем трафика порядка 10-20 Гб/с, обеспечивая поддержку следующих сервисов:

обнаружение/предотвращение вторжений (IDS/IPS);

общее управление рисками (UTM);

анализ пакетов 4-7 уровней;

мониторинг сети;

планирование качества обслуживания (QoS).

Мультимедиа-приложения, прежде всего включают цифровую обработку данных, легко замещая несколько цифровых сигнальных процессоров (ЦПС) или FPGA:

кодирование/декодирование видео;

потоковое и IP-видео (IPTV);

диагностика проблем;

пост-обработка видеоданных.

Применение в области беспроводных коммуникаций включает работу в существующих сетях GSM/CDMA и в сетях следующего поколения WiMAX & LTE. Прежде всего, это:

базовые приемо-передающие станции (BTS);

контроллеры базовых станций (BSC);

шлюзы кампусной зоны (GGSN, SGSN, media gateway).

Процессор Tile64 может быть оптимизирован для выполнения определенных задач. Теоретически Tile64 будет обеспечивать десятикратный прирост производительности по сравнению с серверным процессором Intel Xeon при значительно меньшем энергопотреблении.

Tile64Pro является процессором общего назначения с MIMD-архитектурой. Каждое ядро может работать и под управлением собственной операционной системы, и под управлением многопроцессорной системы типа SMP Linux, соответственно, одновременно процессор может поддерживать различные приложения, к примеру, обработку видеокадров, шифрование данных и обработку стека сетевых протоколов.

Виртуальная память и технология Tilera's Multicore Hardwall позволяет осуществлять защиту данных на уровне ядра, как для общей памяти, так и для потоков и сообщений пользовательского уровня.

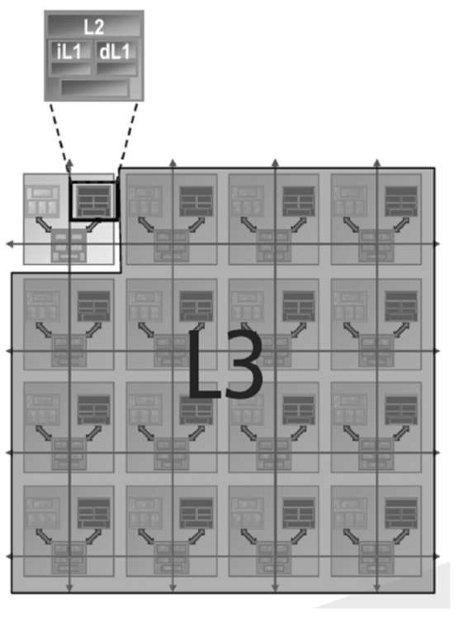

Процессор содержит 64 идентичных вычислительных ячейки (tile), организованных в двумерный массив 8х8 (рис.27.1, 27.2). Ячейка является базовым блоком процессора и состоит из комбинации коммутатора и RISC-ядра общего назначения. Каждое ядро представляет собой полноценный RISC-процессор, работающий на частотах от 600 МГц до 1 ГГц, и содержит кэши первого и второго уровней (L1, L2 cache).

Рис.27.1. Ячейка процессора Tile64

Рис.27.2. Структура процессора Tile64

Ядро имеет все основные возможности обычного процессора, такие как:

полный доступ к памяти и портам ввода-вывода;

виртуальная память и защита данных (MMU/TLB);

иерархический кэш с отдельными уровнями L1-I и L1-D;

многоуровневая система прерываний;

трехканальный конвейер VLIW, позволяющий выбирать 3 инструкции за цикл.

Каждое из ядер процессора Tile64 имеет собственную кэш-память первого и второго уровней (рис.27.3).

Рис.27.3. Организация кэш-памяти

Ядра оптимизированы для обеспечения наивысшей производительности при минимальном потреблении энергии. При работах на частотах между 500 и 1000 МГц энергопотребление составляет 170-300 мВт в расчете на ядро для типичных приложений. Соответственно, суммарное энергопотребление процессора составляет около 20 Вт.

Распределенный по ядрам когерентный кэш обеспечивает малое время задержки и большую емкость. Подсистема кэша состоит из высокопроизводительной двухуровневой неблокирующей иерархии кэшей. Двухуровневое решение изолирует кэш первого уровня (L1-инструкций и L1-данных) от лишних операций обращения к памяти, сохраняя решение быстрым и энергоэффективным. Аппаратная предварительная выборка инструкций для кэша инструкций L1-I уменьшает частоту промахов кэша. Программируемый блок прямого доступа в память позволяет осуществлять объемные передачи данных. Архитектура процессора разработана таким образом, что отдельному ядру доступен распределенный по другим ядрам кэш. Такая организация когерентного кэша предусматривает аппаратный контроль за доступом к общей распределенной памяти, это и позволяет ядру иметь доступ к набору локальных кэшей всех остальных ядер, работая как кэш третьего уровня.

Организованный данным образом кэш устраняет узкое место при доступе в глобальную внешнюю память — снижает частоту обращений.

Система когерентности кэшей позволяет получить доступ к странице памяти, кэшированной одним из ядер, и к остальным ядрам процессора при помощи операций чтения/записи (аналогично обращению к собственному кэшу ядра). Фактически ядро, кэшируя данные для себя, кэширует их для всех остальных ядер, независимо от их потребности в этих данных, что повышает производительность процессора в целом.

Технология Multicore Hardwall позволяет пользователю выделить одно или несколько ядер в относительно независимую процессорную группу, исключая коммуникации между выделенной группой и остальными ядрами, не включенными в группу. Если пакет данных пересекает установленную границу группы, вызывается прерывание и управление передается гипервизору — небольшой программе исполнительного уровня для отслеживания и управления системными ресурсами. Это обеспечивает защиту данных приложения в многозадачной среде. Технология Multicore Hardwall защищает множественные приложения и операционные системы от непредвиденных взаимодействий и случайных ошибок (рис.27.4).

Рис.27.4. Выделение независимых групп процессорных ядер

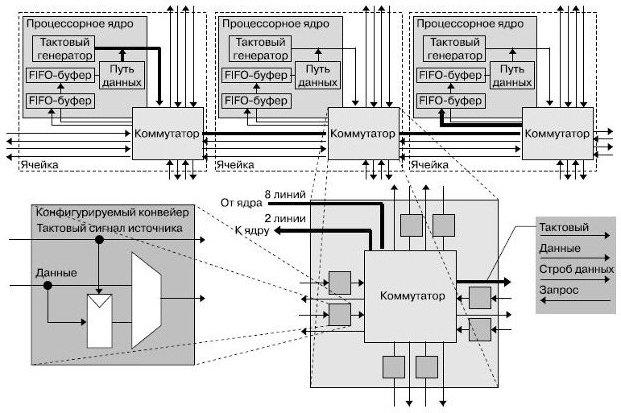

Сеть iMesh обеспечивает высокоскоростную передачу данных, необходимую для устранения узкого места системы и поддержки масштабирования приложений. iMesh состоит из пяти отдельных подсетей. Две подсети управляются полностью аппаратно и используются для передачи данных между ядрами и памятью при промахах кэша или при прямом доступе в память. Три оставшиеся подсети доступны для приложений, позволяют осуществлять взаимодействие между ядрами и между ядрами и устройствами ввода-вывода. Для доступа к аппаратуре используется некоторое количество абстракций, например, потоковые каналы, аналогичные сокетам, или интерфейс передачи сообщений. Сеть iMesh позволяет передавать данные без остановки приложений, выполняющихся на ядрах. Это позволяет осуществлять обмен данными между ядрами и осуществлять контроль и маршрутизацию для каждого сетевого соединения, включая буферизацию и контроль потока по всей сети (рис.27.5).

Рис.27.5. Коммутатор сети iMesh

Коммутатор, расположенный возле ядра, является неблокируемым и подключает ядро к внутрикристальной сети Tilera's iMesh™, которая позволяет каждому отдельному ядру взаимодействовать с находящимися поблизости ядрами. Скорость передачи данных по сети iMesh может достигать 27 Тбит/с.

Сеть реализована по топологии "толстого дерева" (Fat Tree).

Средства разработки включают в себя среду Tilera's Multicore Development Environment™ (MDE), имеющую в своем составе стандартные средства параллельного программирования для многоядерных систем.

Среда Tilera's MDE содержит:

стандартную интегрированную среду разработки, основанную на Eclipse;

компилятор ANSI C/C++;

симулятор;

систему отладки и анализа производительности;

широкие возможности интерфейса командной строки;

полную поддержку системы SMP Linux;

библиотеку iLib для повышения эффективности межъядерных коммуникаций;

отладочные платы PCIe.

Библиотека iLib предоставляет программные интерфейсы, которые позволяют разработчикам:

масштабировать прикладные программы от одного ядра до множества ядер;

абстрагировать межъядерную передачу данных в виде потоков или передач сообщений;

эффективно управлять ресурсами процессора.

27.2. 96-GFLOPS процессор CSX700 компании ClearSpeed Technology

Архитектура процессора CSX700 была разработана для решения проблемы размеров, веса и потребляемой мощности (Size, Weight and Power (SWAP)), которая, как правило, доминирует во встраиваемых высокопроизводительных приложениях. Путем интегрирования процессоров, системных интерфейсов и встроенной памяти с коррекцией ошибок, CSX700 представляет собой экономичное, надежное и производительное решение, отвечающее требованиям современных приложений.

Процессор представляет собой архитектуру с массовым параллелизмом данных и высокой степенью эффективности и надежности. Архитектура нацелена на интеллектуальную обработку сигналов и обработку изображений во временной и частотной областях.

Кристалл CSX700 содержит 192 высокопроизводительных процессорных ядра, встроенную буферную память размером 256 Кбайт (два банка по 128 Кбайт), кэш данных и кэш команд, ECC защиту внутренней и внешней памяти, встроенный контроллер прямого доступа в память. Для обеспечения накристальной и межкристальной сети используется технология ClearConnect NoC (рис.27.6).

Рис.27.6. Структура процессора CSX700

Интерфейс внешней памяти имеет 72 бита для контроля и коррекции данных (Error Checking and Correction — ECC). Используется память 64-бит DDR2 SDRAM объемом до 4 Гбайт. Процессор имеет 64- разрядное адресное пространство, которое отображается в 48-разрядное физическое. Порты CCBR0 и CCBR1 предназначены для образования мультикристальных систем, а также могут служить для подключения ПЛИС.

Процессор состоит из двух относительно независимых модулей (ядер) MTAP, содержащих кэши инструкций, данных, блоки управления процессорными элементами, и набор из 96 вычислительных ядер — процессорных элементов (PE) (рис.27.8). Поддерживает одновременное выполнение восьми потоков.

Рис.27.8. Структура MTAP-блока

На каждом такте процессор извлекает команду, декодирует ее и направляет в исполнительные блоки mono или poly либо на контроллер ввода-вывода. Набор команд традиционен для RISC-процессоров — это трехадресные команды. Кроме того, процессор выполняет команды перехода и управляет переключением потоков. Команды выполняются над операндами mono или poly, причем некоторые из них реализуются только в каком-то одном блоке (например, команды переходов — лишь в mono). Каждое ядро имеет двойной блок вычислений с плавающей точкой (сложение, умножение, деление, вычисление квадратного корня, поддерживаются числа одинарной и двойной точности), 6 Кбайт высокопроизводительной оперативной памяти, 128-байтный регистровый файл. Поддерживается 64-битное виртуальное адресное пространство и 48-битное реальное.

Технические характеристики процессора:

тактовая частота ядер — 250 МГц;

96 ГФлоп двойной или одинарной точности;

поддерживает 75 ГФлопс двойной DGEMM;

производительность целочисленных операций — 48 ГMAC/с (умножений с накоплением в секунду);

рассеиваемая мощность — 9 Вт;

пропускная способность внутренних шин памяти — 192 Гбайт/с;

две внешних шины памяти — 4 Гбайт/с;

скорость обмена данными между отдельными процессорами — 4 Гбайт/с;

интерфейсы PCIe, 2х DDR2 DRAM (64 бита).

Внутрикристальная магистраль позволяет одновременно выполнять несколько обменов, например, обеспечивает доступ процессора к внутренней памяти. Кроме того, она дает возможность вести передачу данных из внешней памяти на порты CCBR0 или CCBR1 с использованием канала DMA.

Ядра синхронно исполняют один поток команд в режиме SIMD. Данные, которые должны обрабатываться параллельно, снабжены описателем poly.

Процессор поддерживает для каждого потока его контекст. Если PE- ядра выполняют длительный ввод-вывод, то процессор должен переключиться на другой поток. При этом потоки имеют приоритеты, и готовый поток с более высоким приоритетом прерывает выполнение потока с более низким. Потоки синхронизируются друг с другом и контроллерами ввода-вывода через аппаратные семафоры.

Семафоры представляют собой специальные регистры, значения которых увеличиваются или уменьшаются с помощью неделимых атомарных команд — соответственно, signal и wait. Если wait выполняется над семафором с нулевым значением, то выполнение команды приостанавливается до тех пор, пока не будет исполнена команда signal над этим семафором в другом треде или устройстве. Операции над семафорами способны выполнять и аппаратные блоки, например, контроллеры ввода-вывода.

Каждое ядро PE может выполнять или не выполнять команды в зависимости от значения разрешающих битов. Если все эти биты составляют "1", то команда выполняется. Если же хотя бы один из таких битов равен "0", большинство команд не выполняются (за исключением, например, команд изменения состояния разрешающих битов). Регистр разрешающих битов трактуется как стек: биты заходят в него через вершину.

Условное выполнение команд в PE поддерживается poly-командами перехода: if, else, endif и др. Они управляют значениями битов разрешения. Например, при выполнении команды if сравнения двух операндов во всех PE происходит следующее: в тех PE, где есть совпадение, в вершину стека будет помещена "1", а в тех, где обнаружено несовпадение, в вершину стека помещается "0". Соответственно, эти PE будут или не будут выполнять последующие команды — вплоть до команды endif, которая "вытолкнет" из стека значение, занесенное командой if. Стек имеет фиксированный размер, поэтому необходимо следить за его переполнением.

Команды чтения и записи из локальной памяти PE в регистры также могут выполняться или нет в зависимости от значения разрешающего бита. Для безусловного выполнения обмена между памятью и регистрами введены специальные команды forced load и forced store.

Канал ввода-вывода PE включает в себя контроллер и один или несколько каналов прямого доступа. Контроллер интерпретирует команды ввода-вывода и взаимодействует с тредами посредством семафоров. Обмен между локальной памятью PE и внешними устройствами выполняется путем программируемого ввода-вывода или с использованием каналов прямого доступа в локальную память. Каждый процессор может читать свою часть данных или выполнять общее чтение — с "нарезкой" одинаковых блоков для каждого процессора.

Процессорные элементы (PE) способны осуществлять обмен с "соседями" справа и слева. На каждом такте PE может выполнить передачу из своего регистра в регистр правого или левого "соседа" и получить одновременно справа и слева данные в свои регистры. Используются команды сдвига вправо и влево, а также передачи "соседу". Если PE имеет бит разрешения "0", то соседний процессор не может изменить состояние его регистров.

Разработанный для низкопотребляющих систем, данный процессор сочетает управление тактовой частотой, обычное для встраиваемых систем, с относительно низкой тактовой частотой. Управление частотой позволяет регулировать производительность приложений при работе в условиях определенного энергопотребления и теплового окружения.

CSX700 поддерживается профессиональной средой разработки (SDK) на основе технологии Eclipse с визуальными средствами отладки приложений, базирующейся на оптимизированном компиляторе ANSI C с расширениями для параллельного программирования. В дополнение к стандартной библиотеке С идет набор оптимизированных библиотек с такими функциями, как БПФ, BLAS, LAPACK и др.

27.3. 167-ядерная вычислительная платформа — AsAP-II

167-ядерная вычислительная платформа (далее — процессор), разработанная в Калифорнийском университете в Дэвисе, реализована в кремнии фирмой STMicroelectronics по 65-нм технологическому циклу. Данный процессор предназначен прежде всего для цифровой обработки сигналов, коммуникационных функций, мультимедийных приложений. Процессор содержит 164 программируемых ядра с динамическим управлением напряжением питания и тактовой частотой, три специализированных процессора, три буфера разделяемой памяти по 16 Кбайт. Все компоненты процессора тактируются собственными независимыми генераторами и соединены специальной внутрикристальной сетью. Структурная схема процессора представлена нарис.27.9. Каждое из ядер имеет 16-разрядные шины данных, 40-битный аккумулятор, независимый тактовый генератор с возможностью останова.

Каждое ядро имеет память команд в 128 35-битных слов, 128 слов 16-разрядной памяти данных, два 16-разрядных FIFO-буфера по 64 слова, одновыходной шестиуровневый конвейер RISC. RISC-ядра поддерживают более 60 базовых инструкций, включая байтовое сложение/вычитание, вычисление минимума/максимума и абсолютных значений, переходы, возвраты из подпрограмм, инструкции условного выполнения, циклы, блок с плавающей точкой. Задача вычисления квадратного корня (CORDIC) выполняется за 216 циклов .

Процессор БПФ может динамически переключаться между вычислением прямого и обратного преобразования Фурье с количеством отсчетов от 16 до 4096 путем вычисления комплексной 4- или 2-точечной "бабочки" за цикл.

Конфигурируемый Витерби-процессор содержит 8 ACS-модулей и может осуществлять декодирование кодов вплоть до длины 10.

Процессор детектора движения поддерживает несколько фиксированных и программируемых поисковых алгоритмов, отвечающих алгоритму H.264, выполняет более 14 миллиардов операций (SADs) в секунду на частоте 880 МГц.

Ядра процессора обмениваются данными посредством конфигурируемых связей между соседними процессорами и длинных связей. Связи являются циклически переключаемыми и статически конфигурируемыми, что хорошо согласуется с технологией локальной синхронизации, используемой в процессоре.

Рис.27.9. Структурная схема 167-ядерного вычислительного массива

Структура связей включает два входа вычислительного ядра и одиночный выход, который динамически подключается к восьми выходам ячейки. Каждая связь содержит 16-разрядную шину данных, сигнал синхронизации источника, разрешающий сигнал (стробирующий) и сигнал запроса на смену направления, используемый для контроля потока. Ограниченные только искажениями тактового сигнала, связи могут быть сконфигурированы для передачи данных сквозь процессор в выбранном выделенном канале без привлечения промежуточных процессоров и безотносительно их текущих напряжений питания и тактовых частот (рис.27.10). Данные могут быть помещены в конвейер в каждой ячейке для достижения полной скорости при передачи на длинные расстояния или передаваться напрямую, если дистанция мала или тактовая частота источника данных мала . Такие меры снижают общую задержку передачи данных.

Рис.27.10. Пример межъядерных соединений

Для уменьшения рассеяния энергии, когда ядра не полностью загружены, ядра могут менять собственное напряжение питания и тактовую частоту. Ядра меняют напряжение питания, подключая свои питающие выводы (VddCore) к одной из двух глобальных шин питания. Также возможно отключение линий VddCore неиспользуемых процессоров от питающих глобальных шин (уменьшая таким образом потребление ядра более чем в 100 раз).

Энергопотребление отдельного ядра при полной загрузке на частоте 1,07 ГГц и питании 1,2 В составляет около 48,4 мВт. При напряжении питания 0.675В ядра работают на частоте 66 МГц и потребляют 0,61 мВт. Таким образом, в зависимости от режима энергопотребление процессора в целом составляет от 101 мВт до 7,93 Вт.

По результатам тестирования, 9-процессорный JPEG-кодер, работающий при напряжениях питания 1,3 В и 0,8 В, достигает примерно 8% экономии энергии по сравнению с тем же кодером, работающим исключительно при питании 1,3 В. Приемник, полностью совместимый со стандартом IEEE 802.11a/g, реализован с использованием 39 процессорных ядер (при этом задействованы только связи между соседними ячейками), плюс специализированные процессоры БПФ и Витерби. Применяя длинные связи, приемник можно реализовать на 27 ядрах — почти на треть меньше. При симуляции последняя версия приемника рассеивает примерно 75 мВт при работе на частоте 690 МГц и скорости данных 54 Мб/с в режиме реального времени (включая 2,7 мВт для БПФ-процессора и 5,5 мВт для Витерби).