- •Лабораторна робота №1 Тема: Розвиток комп'ютерної архітектури

- •Таблиця 1.1. Основні етапи розвитку комп'ютерів

- •Таблиця 1.2. Перші моделі серії івм-360

- •Лабораторна робота №2 Тема: Типова архітектура еом.

- •Таблиця 2.1. Інтерпретація команд перетворення з різною кількістю адрес в адресній частині

- •Лабораторна робота №3 Тема: Формати команд. Адресовий простір еом

- •Лабораторна робота №4 Тема: Етапи виконання команди. Типи і структура даних. Взаємодія основних пристроїв еом.

- •Лабораторна робота №5 Тема: Структури універсальних, функціонально-орієнтованих і спеціалізованих процесорів. Мікропроцесори

- •Таблиця 3.1. Еволюція мікропроцесорів фірми Intel. Вироби 1970-х років.

- •Таблиця 3.2. Еволюція мікропроцесорів фірми Intel. Вироби 1980-х років.

- •Таблиця 3.3. Еволюція мікропроцесорів фірми Intel. Вироби 1990-х років.

- •Лабораторна робота №6 Тема: Арифметико-логічні пристрої

- •Лабораторна робота №7 Тема: Принцип мікропрограмного управління. Реалізація різних етапів виконання команд

- •Таблиця 15.2 Мікрокоманди пристрою керування гіпотетичного процесора Уілкса

- •Лабораторна робота №8 Тема: Організація даних на магнітному диску. Внутрішня пам’ять

- •Таблиця 6.1. Характеристики пзпмд

- •Лабораторна робота №9 Тема: Ієрархічна структура пам'яті. Віртуальна пам’ять.

- •Таблиця 6.3. Основні функції api для керування віртуальною пам'яттю в системі Windows nt

- •Лабораторна робота №10

- •Листінг 7.1. Приклад програмованого вводу-виводу

- •Лабораторна робота № 12 Тема: Класи переривань

- •Лабораторна робота №12 Тема: Переривання. Дії апаратного та програмного забезпечення

- •Дії апаратного забезпечення:

- •Дії програмного забезпечення:

- •Лабораторна робота № 13 Тема: Фаза переривання основного циклу

- •Лабораторна робота №14 Тема: Організація прямого доступу до пам’яті

- •Лабораторна робота № 15 Тема: Арбітраж шини

- •Лабораторна робота № 16 Тема: Персональні еом, їх різновидності

- •Лабораторна робота № 17 Тема:Робота еом у мультипрограмному режимі

- •Лабораторна робота № 18 Тема:Системи колективного користування з розподілом та без розподілу часу. Системи реального часу

Таблиця 15.2 Мікрокоманди пристрою керування гіпотетичного процесора Уілкса

|

|

Сигнали керування АЛП |

Сигнали пересилки поміж регістрами |

Прапори умов |

Наступна мікрокоманда | ||

|

|

|

|

Установка |

Використання |

0 |

1 |

|

0 |

|

|

F→G, F→E |

|

1 |

|

|

1 |

|

|

(G + ‘ 1 ’)→F |

|

2 |

|

|

2 |

|

|

Пам’ять→G |

|

3 |

|

|

3 |

|

|

G→E |

|

4 |

|

|

4 |

|

|

E→дешифратор |

|

|

|

|

A 5 |

C→D |

|

|

|

16 |

|

|

S 6 |

C→D |

|

|

|

17 |

|

|

N 7 |

Пам’ять→B |

|

|

|

0 |

|

|

V 8 |

Пам’ять→A |

|

|

|

27 |

|

|

T 9 |

C→Пам’ять |

|

|

|

25 |

|

|

U 10 |

C→Пам’ять |

|

|

|

0 |

|

|

R 11 |

B→D |

E→G |

|

|

19 |

|

|

L 12 |

C→D |

E→G |

|

|

22 |

|

|

G 13 |

|

E→G |

(1)Cs |

|

18 |

|

|

I 14 |

Пвв→Пам’ять |

|

|

|

0 |

|

|

O 15 |

Пам’ять→ПВив |

|

|

|

0 |

|

|

16 |

(D+Пам’ять)→C |

|

|

|

0 |

|

|

17 |

(D-Пам’ять)→C |

|

|

|

0 |

|

|

18 |

|

|

|

1 |

0 |

1 |

|

19 |

D→B (R)* |

(G - ‘1 ’)→E |

|

|

20 |

|

|

20 |

C→D |

|

(1)Es |

|

21 |

|

|

21 |

D→C(R) |

|

|

1 |

11 |

0 |

|

22 |

D→C(L) ** |

(G – ‘ 1 ’)→E |

|

|

23 |

|

|

23 |

B→D |

|

(1)Es |

|

24 |

|

|

24 |

D→B(L) |

|

|

1 |

12 |

0 |

|

25 |

‘ 0 ’→B |

|

|

|

0 |

|

|

26 |

B→C |

|

|

|

0 |

|

|

27 |

‘ 0 ’→C |

‘ 18 ’→E |

|

|

28 |

|

|

28 |

B→D |

E→G |

(1)B1 |

|

29 |

|

|

29 |

D→B(R) |

(G – ‘ 1 ’)→E |

|

|

30 |

|

|

30 |

C→D(R) |

|

(2)Es |

1 |

31 |

32 |

|

31 |

D→C |

|

|

2 |

28 |

33 |

|

32 |

(D+A)→C |

|

|

2 |

28 |

33 |

|

33 |

B→D |

|

(1)B1 |

|

34 |

|

|

34 |

D→B(R) |

|

|

|

35 |

|

|

35 |

C→D(R) |

|

|

1 |

36 |

37 |

|

36 |

D→C |

|

|

|

0 |

|

|

37 |

(D-A)→C |

|

|

|

0 |

|

— Зрушення вправо. Схема АЛП побудована таким чином, що при зрушенні вправо молодший розряд регістра З пересилається в старший розряд регістра В, а старший (знаковий) розряд регістра З дублюється.

— Зрушення вліво. Схема АЛП побудована таким чином, що при зрушенні вліво старший розряд регістра В пересилається в молодший розряд регістра С.

Умовні позначки: ПВв — пристрій вводу; ПВив — пристрій виводу

При символічному представленні мікрокоманд у табл. 5.2 запис С->D означає, що виходи регістра С підключаються до входів регістра D; запис (D+A)—>С означає, що виходи регістра D підключаються до одним входів суматора, виходи регістра А — до інших входів суматора, а вихід суматора — до входів регістра С; число в парних лапках (наприклад, '18') — константа, що підключається до входів молодших розрядів зазначеного регістра.

У першому стовпчику таблиці представлені адреси мікрокоманд (номера рядків у матриці). Деякі адреси відповідають машинним командам, зазначеним ліворуч від адреси. Так, якщо поле коду операції в регістрі IR відповідає команді додавання (команді А), то виконується мікрокоманда за адресою 5. У наступних двох колонках представлені мікрооперації, виконувані в АЛП й у пристрої керування. Кожному символьному вираженню відповідає свій набір керуючих сигналів — розрядів мікрокоманди. Четвертий і п'ятий стовпчики мають відношення до установки й опитування двох прапорів. Наприклад, символічний запис (2)Es у четвертому стовпчику означає, що прапор 2 встановлюється у відповідності до значення знакового розряду регістра Е. Якщо в п'ятому стовпчику зазначений номер прапора, то в шостому і сьомому стовпчиках вказуються адреси двох альтернативних мікрокоманд, що повинні виконуватися наступними. Перша виконується, якщо прапор не встановлений, а друга — якщо встановлений. Якщо в п'ятому стовпчику прапор не зазначений, то в шостому представлена єдина адреса наступної мікрокоманди.

Мікрокоманди з 0-й по 4-у реалізують фазу витягу машинної команди. Мікрокоманда 4 підключає виходи коду команди до входів дешифратора, що формує адресу першої мікрокоманди відповідної мікропрограми.

Переваги і недоліки мікропрограмування

Основне достоїнство мікропрограмного підходу до організації пристрою керування — спрощення і формалізація процесу його розробки. У результаті розробка дешевшає і вона пов’язана з меншою кількістю помилок. Пристрій керування з твердою логікою повинен містити у своєму складі складні комбінаційні логічні схеми формування сигналів керування відповідно до коду виконуваної команди і номеру такту, а також з обліком, якщо це необхідно, стану керуючих регістрів.

Принциповий недолік мікропрограмних пристроїв керування в порівнянні з пристроями з твердою логікою — менша швидкодія при реалізації на тій же елементній базі. Незважаючи на це, мікропрограмування є домінуючим підходом при створенні пристроїв керування сучасних CISC-процесорів з великим набором команд. У RISC-процесорах, що мають більш простий набір команд, частіше використовується тверда логіка керування. Нижче ми більш докладно розглянемо сучасні методи організації мікропрограмного керування.

Реалізація різних етапів виконання команд

В попередніх темах вже описувалося, як взагалі протікає основний цикл обробки машинної команди (мал. 5.6). Нагадуємо, що цикл включає три основних фази (або підцикла).

• Фаза витягу. Зчитування чергової команди з пам'яті в процесор.

• Фаза виконання. Розшифровка коду операції і виконання відповідних дій.

• Фаза переривання. Якщо переривання дозволені і мається запит переривання, збереження поточного стану процесу й обслуговування переривання.

Познайомившись з особливостями організації процесора, ми можемо зараз внести в цю спрощену схему циклу деякі уточнення — нові фази.

Фаза непрямої адресації

В процесі виконання команди процесору можуть знадобитися операнди (один чи два), що знаходяться в пам'яті. Витяг кожного операнда вимагає звертання до пам'яті. Якщо в специфікації операнда зазначений режим непрямої адресації, то крім звертання до пам'яті за значенням операнда, буде потрібно ще одне звертання до пам'яті за адресою операнда.

Можна вважати, що витяг непрямо заданої адреси— це ще одна фаза циклу обробки команди. Схема циклу з урахуванням варіанта непрямої адресації показана на мал. 5.7. При обробці більшості команд у циклі фактично реалізуються тільки дві фази — витягу і виконання. Після того як команда витягнута, перевіряється, чи не заданий у ній в тому чи іншому виді непрямий режим адресації. Якщо справа обстоїть саме так, у цикл включається фаза витягу непрямої адреси. Після фази виконання і перед початком наступного циклу може включатися фаза переривання, якщо надійшов запит переривання.

Іншу схему наочного представлення процесів, що відбуваються під час циклу обробки, ви бачите на мал. 5.8. Після того як команда буде витягнута, потрібно розшифрувати специфікації операндів. Потім з пам'яті витягаються операнди, і ця процедура може включати фазу витягу непрямої адреси. Аналогічна процедура виконується при збереженні результату в пам'яті.

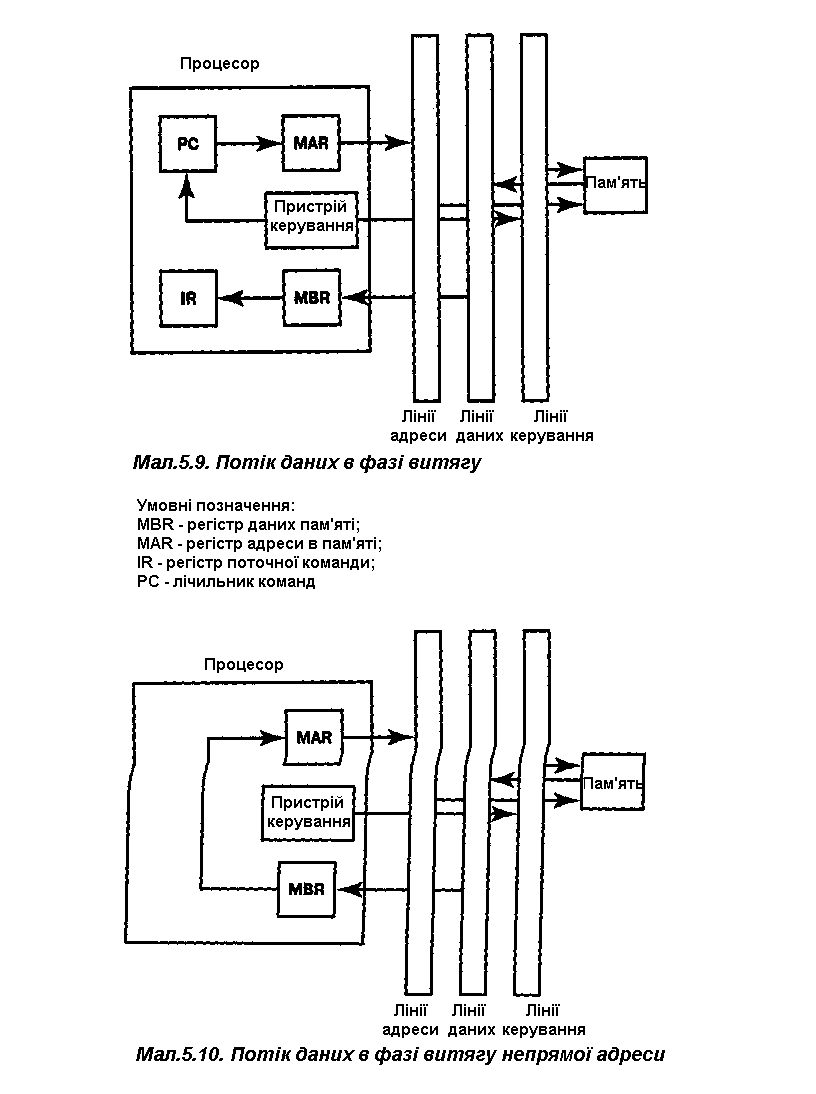

Потік даних

Конкретна послідовність подій в продовження циклу обробки команди залежить від обраної схеми процесора. Але, застосовуючи універсальну термінологію, можна незалежно від його конкретної схеми позначити, що ж повинно відбуватися в процесорі. Будемо вважати, що процесор використовує регістр адреси в пам'яті (MAR), регістр даних пам'яті (MBR), лічильник команд (PC) і регістр команди (IR).

У фазі витягу команда зчитується з пам'яті. На мал. 5.9 показано, як циркулюють в цей час дані між компонентами процесора. Лічильник команд містить адресу чергової команди. Ця адреса передається в MAR і виставляється на лінії адреси магістралі. Пристрій керування супроводжує адресу сигналом читання на лініях керування. Витягнута з пам'яті інформація виставляється на лінії даних і копіюється в MBR, а з нього в IR. Тим часом код у PC збільшується на довжину витягнутої команди, і, таким чином, лічильник команд підготовлюється до нового циклу.

Після завершення фази витягу пристрій керування аналізує вміст IR і визначає, чи не міститься в специфікації операндів вказівки на непряму адресацію. Якщо задана непряма адресація, настає черга фази витягу непрямої адреси. Як показано на мал. 5.10, це досить проста фаза. Молодші N розрядів MBR, у яких міститься посилання на адресу, передаються в MAR. Потім пристрій керування виставляє на лінії керування сигнал читання і шукана адреса операнда фіксується в MBR.

Операції, які виконуються у фазі витягу команди і непрямої адреси, прості і легко прогнозуються. Цього не можна сказати про операції фази виконання команди, оскільки вони залежать як від вмісту коду команди в регістрі IR, так і від результатів виконання попередньої команди (а іноді і декількох попередніх команд). У цій фазі може виконуватися передача даних між регістрами або читання запису у пам'ять або модуль вводу-виводу, і/або виконання арифметичних чи логічних операцій за участю АЛП.

Остання

фаза циклу — фаза

переривання — також

досить проста і передбачувана (мал.

5.11). Якщо мається запит переривання й

обробка переривань дозволена, зберігається

поточний вміст лічильника команд, що

дозволяє надалі відновити виконання

перерваної програми з тієї ж крапки.

Для цього вміст PC передається в регістр

MBR, щоб його можна було записати в пам'ять.

Адреса осередку, яка виділена з цією

метою в пам'яті, "знає" пристрій

керування і передає його в регістр MAR.

Найчастіше для збереження вмісту

лічильника команд використовується

системний стек і, таким чином, ця адреса

міститься в регістрі покажчика стека.

У PC замість поточної адреси перерваної

програми завантажується початкова

адреса підпрограми обробки переривання.

У результаті наступний

цикл почнеться

з витягу першої команди підпрограми

о бробки

переривання.

бробки

переривання.

Контрольні питання:

Мікропрограмна організація пристрою керування.

Горизонтальна мікрокоманда.

Вертикальна мікрокоманда.

Організація керуючої пам’яті.

Структура мікропрограмного пристрою керування.

Деталізована схема мікропрограмного пристрою керування.

Пристрій керування Уілкса.

Гіпотетичний комп’ютер Уілкса.