5.Классификация по временным характеристикам.

По временным характеристикам АЛУ делятся на:

-

синхронные- в синхронных АЛУ каждая операция выполняется за один такт.

-

асинхронные- не тактируемые АЛУ, обеспечивающие высокое быстродействие, так как выполняются на комбинационных схемах.

6.Классификация по структуре устройства управления:

-

АЛУ с жесткой логикой устройства управления;

-

АЛУ с микропрограммным управлением.

Основные функции алу

Современные АЛУ выполняют:

-

функции двоичной арифметики для данных в формате с фиксированной точкой;

-

функции двоичной арифметики для данных в формате с плавающей точкой;

-

функции арифметики двоично-десятичного представления данных;

-

логические операций (в том числе сдвиги арифметические и логические);

-

операции пересылки данных;

-

работу с символьными данными;

-

работу с графическими данными.

Основные характеристики алу

Основные характеристики АЛУ можно разделить на количественные и качественные.

Количественные характеристики

Количественные характеристики определяют скорость выполнения операций, время выполнения одной операции, точность представления данных, количество выполняемых операций.

Среднюю скорость выполнения операций Vср в АЛУ можно определить как отношение N(T)- количества операций, выполненных за отрезок времени Т к данному отрезку времени:

Vср = N(T)/T

Среднее время, которое АЛУ тратит на выполнение операции равно: Tср = 1/Vср

Точность представления данных в АЛУ зависит от разрядной сетки АЛУ и выбранного формата данных.

Качественные характеристики АЛУ:

К качественным характеристикам АЛУ относятся:

-

структурные особенности АЛУ;

-

форматы представления данных (с фиксированной или плавающей точкой);

-

способы кодирования данных.

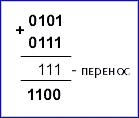

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.Сумматор является простейшим цифровым устройством. Это узел ЭВМ, выполняющий арифметическое суммирование кодов чисел, т.е. он предназначен для сложения двух чисел, заданных в двоичном коде. Сравним суммирование десятичных и двоичных чисел:

|

|

|

Правила сложения двоичных и десятичных чисел одинаковы:

-

сложение производиться поразрядно – от младшего разряда к старшему;

-

в младшем разряде вычисляется сумма младших разрядов слагаемых Аi и Вi. Эта сумма в данной системе счисления может быть записана однозначным числом S1 либо двухзначным числом P1S1. Функция P называется переносом;

-

во всех последующих разрядах находиться сумма данных разрядов слагаемых Ai и Bi, причем при Pi-1=1 к этой сумме добавляется единица (в числовых примерах, приведенных выше, этот случай выделен жирным шрифтом, результат сложения в i-м разряде записывается в виде однозначного Si или двухзначного PiSi числа.

Таким образом, в каждом разряде необходимо найти сумму Ai, Bi и Pi-1 (если Pi-1=1), т.е. определить Si и Pi. По числу входов различают полусумматоры, одноразрядные сумматоры (ОС) и многоразрядные сумматоры.

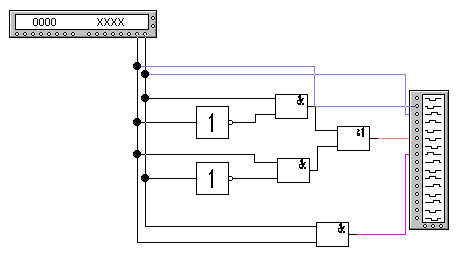

Рисунок 3.2.3.1 - Схема полусумматора

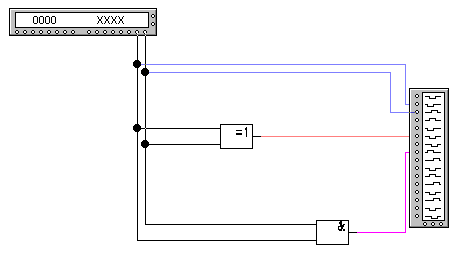

Рисунок 3.2.3.2 - Схема полусумматора с использованием стандартной схемы сложения по модулю 2

Полусумматорами называются устройства с двумя входами и двумя выходами, на которых вырабатываются сигналы суммы и переноса. Полусумматор реализует лишь часть задачи суммирования, так как не учитывает входной величины – переноса из соседнего младшего разряда в данных(см. рисунки 3.2.3.1 и 3.2.3.2). В таблице 3.2.3.1 приведена таблица истинности полусумматора. На рисунке 3.2.3.3 приведена временная диаграма работы полуссуматора.

|

Xi |

Yi |

Si |

PI+1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Таблица 3.2.3.1 - Таблица истинности полусумматора

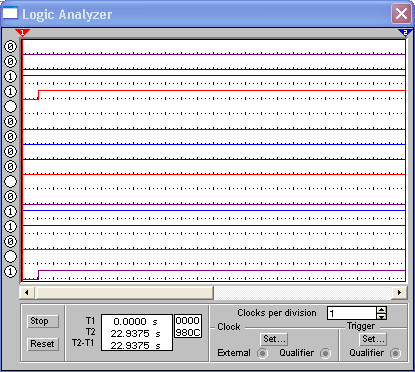

Рисунок 3.2.3.3 - Диаграмма работы полусумматора

Логические уравнения: S=x^*y+x*y^ P=x*y

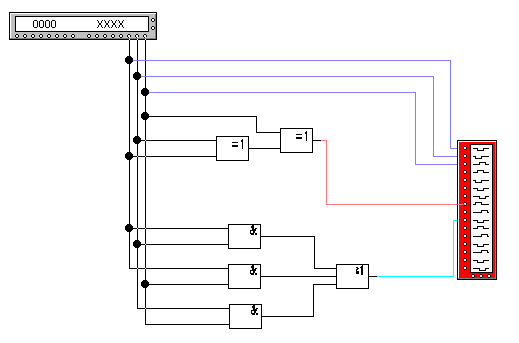

Одноразрядный двоичный сумматор состоит из двух комбинационных схем: одна формирования Si, вторая для определения Pi. (см. рисунки 3.2.3.4 и 3.2.3.5).Многоразрядный сумматор строится на основе одноразрядных в соответствии с правилами сложения.

Рисунок 3.2.3.4 - Схема однорязрядного двоичного сумматора

Рисунок 3.2.3.5 - Диаграмма работы однорязрядного двоичного сумматора

Одноразрядные сумматоры имеют три входа и обеспечивает сложение разрядов слагаемых и переносом из предыдущего разряда. (см. таблицу 3.2.3.2).

|

Xi |

Yi |

Pi |

Si |

Pi+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Таблица 3.2.3.2 - Таблица истинности сумматора

Логические уравнения S=y1+y2+y3+y4 Y1=x1^*x2^*x3 Y2=x1^*x2*x3^ Y3=x2^*x3^*x1 Y4=x1*x2*x3 Pi+1=y1+y2+y3+y4 Y1=x1^*x2*x3 Y2=x1*x2^*x3 Y3=x1*x2*x3^ Y4=x1*x2*x3

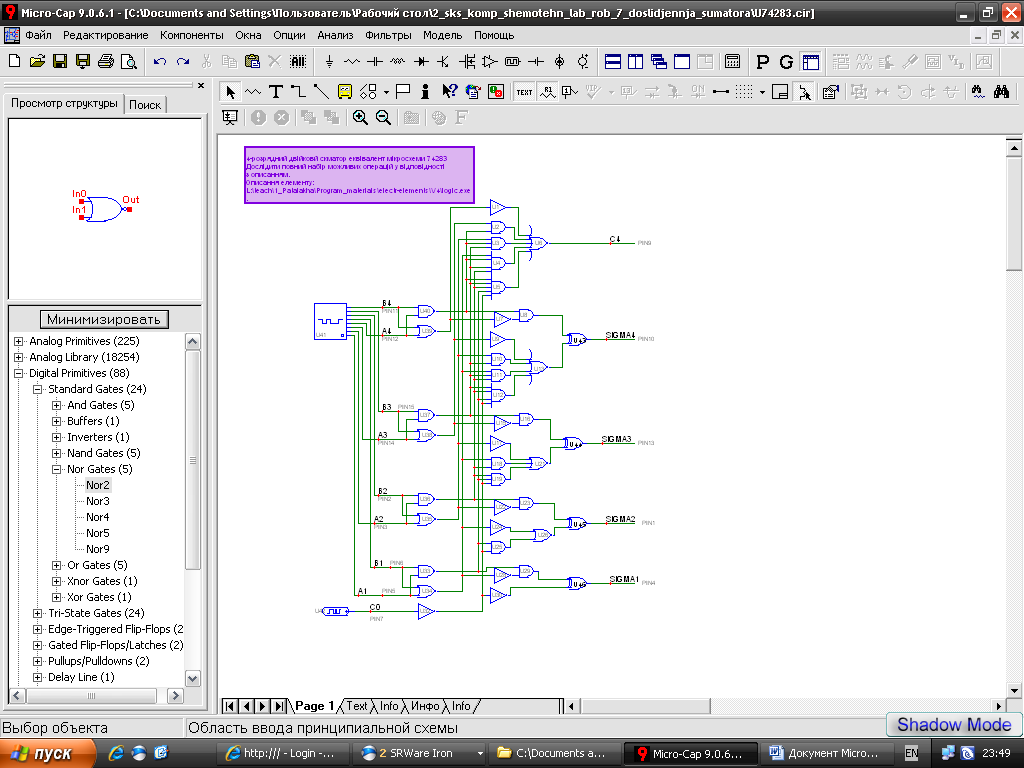

Минимизируя данные уравнения по формулам алгебры логики, построим сумматор в Electronics Workbench.

В зависимости от характера ввода-вывода кодов и организации переносов многоразрядные сумматоры бывают последовательного и параллельного принципа действия.

В последовательном сумматоре сложение кодов осуществляется, поразрядно начиная с младшего разряда с помощью комбинационного сумматора на три входа. Образующийся в данном разряде перенос Рj+1 задерживается на время tэд и поступает на вход Pj сумматора в момент поступления следующего разряда слагаемых. Таким образом, последовательно разряд за разрядом производиться сложение кодов чисел. Достоинством последовательного сумматора является простота аппаратурной реализации, а недостатком - достаточно большое время суммирования (см. рисунок 3.2.3.6). На рисунке 3.2.3.7 приведена временная диаграмма, иллюстрирующая работу последовательного сумматора.

Рисунок 3.2.3.6 - Схема последовательного сумматора

Рисунок 3.2.3.7 - Диаграмма работы последовательного сумматора

В параллельном сумматоре достигается более высокое быстродействие. Суммируемые коды поступают на входы сумматора одновременно по всем разрядам. Для этого в каждом разряде используется комбинационный сумматор на три входа, на выходах которого образуются значения суммы Sj данного разряда и переноса Pj+1 в старший разряд. В процессе распространения сигнала переноса устанавливается окончательное значение суммы в каждом разряде. Очевидно, что в течение этого времени на входах сумматора присутствуют сигналы Xi, Yi, соответствующие суммируемым кодам. Максимальное по времени суммирование получается в том случае, когда перенос, возникший в первом разряде, распространяется по всем разрядом (например, при сложении кодов 11..11 и 00..01). В параллельном сумматоре обычно применяются различные способы ускорения переноса (параллельный перенос, групповой и т. п.) На, приведена временная диаграмма, илылюстрирующая работу последовательного сумматора.

Задание №1:

Исследовать 4-розрядный двоичный сумматор.

Задание №2:

В текстово -графическом виде представить АЛУ.

Вывод: При выполнении данного индивидуального задания было исследовано 4-розрядный двоичный сумматор, АЛУ, как важнейший узел ЭВМ. Отчет содержит основные теоретические сведенья об этих устройствах, схему, анализ переходных процессов.

Список использованной литературы

-

http://window.edu.ru/library/pdf2txt/729/21729/4942/page6

-

http://course-cst.narod.ru/lec_page21.html

-

http://naf-st.ru/articles/digit/alu/

Міністерство освіти і науки України

Державний вищий навчальний заклад

Український державний хіміко-технологічний університет

Кафедра СКС