- •4). Перетворення чисел з різних систем числення.

- •5. Rs-тригери.

- •Таблиці переходів

- •Схемна реалізація

- •6. Інтегруючі і диференціюючі ланки.

- •7. Основні логічні операції алгебри логіки.

- •8. Jk- та t-тригери.

- •Т-тригер асинхронний

- •T-тригер синхронний

- •9. Базисні елементи. Базис або-ні.

- •10. Мінімізація логічних функцій.

- •11.Тригер Шмідта.

- •12. Базисні елементи. Базис "і-ні".

- •13. Карти Карно.

- •14. D-триггери .

- •15. Елемент "виключне або".

- •17. Лічильники. Лічильник з послідовним перенесенням.

- •18. Лічильники. Реверсивний лічильник.

- •19. Двійково-десяткові лічильники.

- •20. Шифратори і дешифратори.

18. Лічильники. Реверсивний лічильник.

Двійкові реверсивні лічильники мають переходи у двох напрямках: в прямому(при

лічбі підсумовуючих сигналів U ) і в зворотному( при переліку віднімальних сигналів

U ). Поточне значення різниці підрахованих імпульсів визначається із співвідношення

Розрізняють одноканальні та двоканальні реверсивні лічильники. В одноканальних

реверсивних лічильниках підсумовуючі U і віднімальні U сигнали почергово надходять

на спільний лічильний вхід, а напрямок лічби задається напрямком ланцюгів між

розрядних перенесень або позик. Для перемикання міжрозрядних зв’язків у

одноканальному реверсивному лічильнику потрібні додаткові керуючі сигнали.

Двоканальні реверсивні лічильники мають два лічильних входи: один для

підсумовуючих імпульсів U , другий – для віднімальнихU . Перемикання ланцюгів

міжрозрядних зв’язків здійснюється автоматично лічильними сигналами: для переносів –

імпульсами U , для позики – імпульсами U . Схема одно канального трирозрядного

двійкового реверсивного лічильника показана на рис.23.7. Між розрядні зв’язки

комутуються за допомогою логічних елементів І-АБО.

Для задання напрямку лічби використовують додатковий RS-тригер: з його

прямого виходу знімається сигнал керування додаванням Y Д (вмикає ланцюги

перенесення), а з інверсного виходу – сигнал керування відніманням Y В (вмикає ланцюги

позики). На виходах елементів І-АБО (які називаються „схеми реверса”) виробляється

сигнал T i для лічильних входів старших розрядів:

Таким чином, якщо керуючий RS-тригер знаходиться в стані „1”, то лічильник реалізує режим прямої лічби вхідних імпульсів (тобто підсумовування), в іншому випадку – забезпечує режим зворотної лічби (віднімання). В обох режимах роботи тригери перемикаються асинхронно.

19. Двійково-десяткові лічильники.

Двійково-десяткові лічильники реалізують лічбу імпульсів у десятковій системі числення, причому кожна десяткова цифра від нуля до дев’яти кодується чотири- розрядним двійковим кодом (тетрадою). Ці лічильники часто називають десятковими або декадними, оскільки вони працюють з модулем лічби, кратним десяти (10, 100, 1000 і т.д.).

Багаторозрядний двійково-десятковий

лічильник будується на основі регулярного

ланцюга декад, при цьому перша (молодша)

декада має вагу ![]() , друга -

, друга -![]() ,

третя

,

третя![]() -

і т.д.

-

і т.д.

Декада будується на основі чотирирозрядного двійкового лічильника, в якому вилучається надлишкове число станів. Вилучення зайвих шести станів у декаді досягається багатьма способами:

- попереднім записуванням числа 6 (двійковий код 0110); після лічби дев’ятого імпульсу вихідний код дорівнює 1111 і десятковий сигнал повертає лічильник у початковий стан 0110, отже, тут результат лічби фіксується двійковим кодом з надлишком 6;

- блокування переносів: лічба імпульсів до дев’яти здійснюється у двійковому коді, після чого вмикаються логічні зв’язки блокування перенесень; з надходженням десятого імпульсу лічильник закінчує цикл роботи і повертається в початковий нульовий стан;

- введення обернених зв’язків, які забезпечують лічбу в двійковому коді й примусовим перемиканням лічильника в нульовий початковий стан після надходження десятого імпульсу.

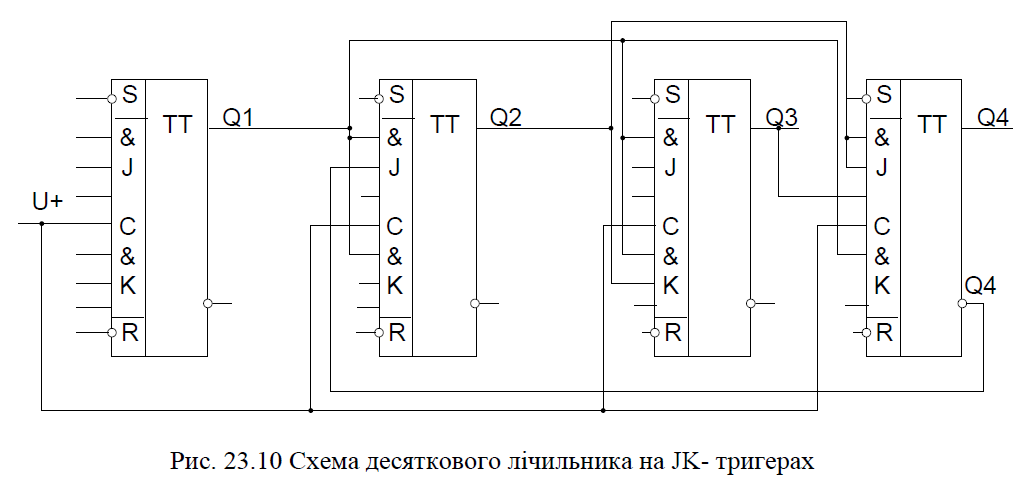

Схема синхронного десяткового лічильника з блокуванням перенесень показана на

рис.23.10. У цій схемі С-входи використовуються

як лічильні. З надходженням десятого

імпульсу на С-вхід молодшого розряду

JK-тригера обнуляються перший і четвертий

розряди і сигналом з виходу ![]() блокують

перемикання другого і третього розряду.

блокують

перемикання другого і третього розряду.