- •Введение

- •Одномашинные СОД

- •Многомашинные СОД

- •Многопроцессорные СОД

- •Специализированные СОД

- •Технические средства вычислительных систем

- •Интерфейсы

- •Программное обеспечение вычислительных систем

- •Способы организации параллельной обработки информации

- •Мультипрограммная обработка

- •Классификация вычислительных систем параллельной обработки

- •Системы класса ОКОД

- •Системы класса МКОД

- •Системы класса ОКМД

- •Системы класса МКМД

- •Многомашинные вычислительные системы

- •Прямосвязанные вычислительные системы

- •Саттелитные вычислительные системы

- •Многопроцессорные вычислительные системы

- •Вычислительные системы с общей шиной

- •Вычислительные системы с перекрестной коммутацией

- •Вычислительные системы с многовходовыми ОЗУ

- •Первая группа разработок

- •Вторая группа разработок

- •Третья группа разработок

- •Однородные системы и среды

- •Матричные вычислительные системы

- •Вычислительная система ILLIAC-IV

- •Вычислительная система ПС-2000

- •Ассоциативные вычислительные системы

- •Считывание данных из ЗМ

- •Запись данных в ЗМ

- •Функционально распределенные вычислительные системы

- •Учебно-методическое обеспечение дисциплины

- •Литература основная:

- •Литература дополнительная:

ром, а программно, т.е. как писали американцы, вследствие громоздкости системы и недостаточной гибкости и эффективности. На самом деле из-за не- готовности ни науки, ни промышленности.

Вычислительная система ILLIAC-IV

Идеи системы SOLOMON получили развитие в вычислительной сис- теме ILLIAC-IV, разработанной Иллинойским университетом США (рис. 31).

Рис. 31

УП – процессор управления ЦУП – центральный управляющий процессор

По первоначальному проекту система ILLIAC-IV должна была вклю- чать в свой состав 256 ПЭ, разбитых на 4 группы или квадранта по 64 ПЭ (рис. 31). Каждый квадрант должен был управляться специальным процессо- ром управления (УП). Управление всей системой, содержащей также внеш- нюю память и оборудование ввода-вывода, предполагалось от центрального управляющего процессора (ЦУП). Из-за возникших технологических труд- ностей при создании интегральных схем и ОЗУ, а также из-за удорожания всего проекта более чем в два раза, реализовать полностью этот замысел не удалось. В результате с опозданием на два года система была создана, но в урезанном составе: одного квадранта, одного УП, без коммутатора, но общее управление системой было исполнено в запланированном виде. Предполага- лось ранее получить производительность примерно 1 млрд операций в се- кунду, однако реализовали 200 млн операций в секунду. На тот период (сере- дина 70-х) это считалось очень приличным достижением. Квадрант образует матрицу ПЭ 8х8, при этом схема связей между ПЭ похожа на схему системы SOLOMON, но связь с внешней средой в отличие от той имеют все ПЭ без исключения.

43

Таким образом, реально действующая система состояла из двух частей: центральной с устройством управления и одного квадранта из 64 ПЭ, а также из подсистемы ввода-вывода. Каждый ПЭ состоит из собственного процессо- ра и ОЗУ. ОЗУ выполнена на интегральных схемах. В каждом ПЭ имеется регистр управления, аналогичный регистру моды в системе SOLOMON. Но в системе ILLIAC-IV этот регистр имеет не 4, а 8 разрядов. В зависимости от содержания этого регистра ПЭ выполняет или не выполняет операции. В ла-

зерной памяти информация записывается на тонкой металлической пленке путем прожигания микроотверстий лазерным лучом. Емкость ее 1200 млрд бит.

Указанная производительность системы ILLIAC-IV достигается только на определенных типах задач, таких, например, как операции над матрицами, быстрое преобразование Фурье, линейное программирование и т.п. Именно это ограничение оказалось важнейшим недостатком системы ILLIAC-IV.

Вычислительная система ПС-2000

В конце 70-х годов в СССР в классе вычислительных систем ОКМД была создана и серийно выпускалась «вычислительная система ПС-2000» общей производительностью 200 млн операций в секунду. Она также может быть отнесена к матричным системам, несколько похожа на ILLIAC-IV, но в

отличие от нее обладает указанной производительностью на любом классе задач, что существенно.

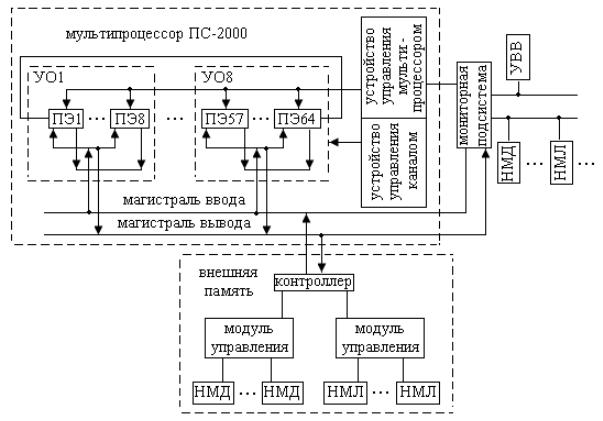

Укрупненная структурная схема вычислительной системы ПС-2000 изображена на рис. 32.

Рис. 32

44

НМД – накопитель на магнитных дисках НМЛ – накопитель на магнитной ленте УО – устройство обработки

Центральная часть системы- мультипроцессор, состоящий из решаю- щего поля и устройства управления мультипроцессором. Решающее поле строится из одного, двух, четырех или восьми устройств обработки (УО), в каждом из которых восемь ПЭ.

Таким образом, мультипроцессор может содержать 8, 16, 32 или 64 ПЭ. Покупателю ПС-2000 предоставлялось право выбрать и заказать модифика-

цию данной вычислительной системы с интересующим количеством ПЭ из вышеуказанных групп. Каждый ПЭ имеет свое ОЗУ, а устройство управле- ния – свой ПЭ, ОЗУ которого используется как блок микропрограммного управления емкостью 16384 микрокоманды. Это позволяет реализовать на микропрограммном уровне любую необходимую систему операций.

Ввод-вывод данных в ОЗУ ПЭ производится через канал прямого дос- тупа, состоящий из магистралей ввода и вывода. Операция ввода-вывода инициируется модиторной подсистемой и выполняется под управлением уст- ройства управления мультипроцессора, при этом обработка, ввод и вывод данных могут выполняться одновременно.

ПЭ решающего поля связаны регулярным каналом, по которому пере- даются данные. Конфигурация регулярного канала перестраивается под управлением программы, образуя одно кольцо из 64 ПЭ (как на рис. 32) или несколько одинаковых колец 8 по 8, 4 по 16 или 2 по 32 ПЭ.

Мониторная подсистема управляет загрузкой мультипрограмм в муль- типроцессор, контролирует его работу и обеспечивает связь с пользователем.

Для хранения больших объемов данных, служит ВЗУ, состоящее из микропрограммируемого контроллера, НМД и НМЛ. Накопители подключа- ются к контроллеру через модули управления.

Вычислительный процесс в системе ПС-2000 слагается из трех состав- ляющих:

1.Процесса в мониторной подсистеме

2.Выполнения программы

3.Ввода-вывода данных

Процесс в мониторной подсистеме является основным, т.к. инициирует остальные процессы и синхронизирует их.

Ассоциативные вычислительные системы

Они также относятся к матричным и характеризуются большим числом ПЭ, способным одновременно по единой команде устройства управления вести обработку различных потоков данных.

Но эти системы существенно отличаются от других матричных систем формированием потоков данных. В обычных матричных системах использу- ются запоминающие устройства (ЗУ) с адресной выборкой или записью ин- формации, которые затрачивают больше времени на запись и считывание слов данных, т.к. при считывании или записи каждого слова опрашиваются

45

все ячейки куба памяти. В ассоциативных вычислительных системах исполь- зуют ассоциативные ЗУ, характеризующиеся тем, что данные определяются не по адресу, а по их содержанию. Это позволяет затрачивать на запись и считывание существенно меньше времени. Реализуется это следующим обра- зом (рис. 33).

Рис. 33

УУ – устройство управления РАП – регистр ассоциативных признаков РМ – регистр маски

Т – содержание разряда регистра, равное нулю или единице Запоминающий массив содержит число ячеек, равное «n», а каждая

ячейка содержит «m» разрядов.

Считывание данных из ЗМ

Реализуется оно следующим образом. В РАП из ЗУ передается код признака данных, который может иметь произвольное число разрядов от 2 до «m». Если этот код используется полностью, он без изменения передается в устройство сравнения, если же используется часть этого кода, тогда ненуж- ные разряды маскируются с использованием регистра маски. Перед началом считывания данных из ЗМ все разряды регистра индикаторов адреса устанав- ливаются в состояние «единица». После этого производится параллельное считывание первого разряда со всех ячеек ЗМ и параллельная передача со- держания первых разрядов всех ячеек в устройство сравнения, где они срав- ниваются с содержимым первого разряда РАП. Если в каких-то ячейках нет сравнения, то соответствующие им разряды регистра индикаторов адреса сбрасываются в состояние «ноль», а в случае сравнения остаются в состоя-

46