ВТиИТ лекции

.pdf

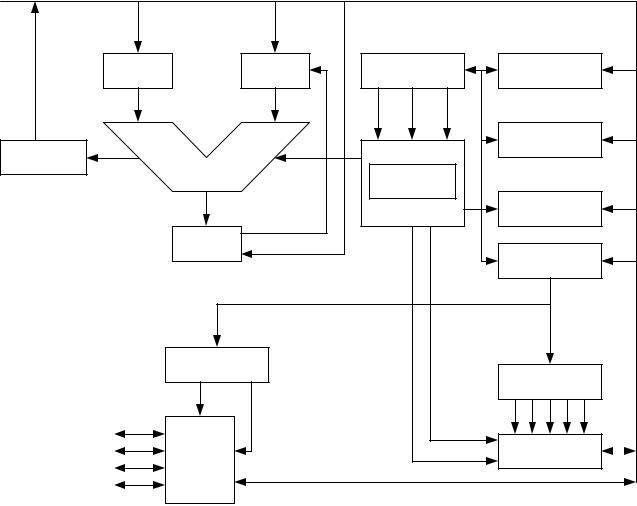

С жесткой логикой

RG команд

ДШК

ADD SUBS

|

|

|

|

КС |

|

|

ДШ |

|

|

СУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Si |

|

|

|

|

|

|

|

ГТИ |

||||||

|

|

|

|

|

|

|

||||||||

|

|

|

Такт |

|

|

Такт |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vi

ДШК – дешифратор команд КС – комбинационная схема

Повышается быстродействие (т.к. нет ячейки памяти), но жесткая структура. ГТИ задает последовательность выполнения команд путем выработки на дешифратор тактов последовательности тактовых сигналов. ДШ определяет часть комбинационной схемы, на которую поступает управляющий сигнал от дешифратора тактов.

|

|

АЛУ |

|

n |

|

|

|

|

n |

|

|

|

RG А Прямой |

|

|

|

n |

|

RG В |

|

|

|

|

|

RG А Инверсный |

|

n |

|

|

|

|

|

n |

|

|

RG Признаков |

|

|

|

|

|

n |

n |

Si в АЛУ |

|

|

|

|

Аккумулятор |

n |

|

|

|

||

|

|

|

Операнды помещаются в регистры А и В. Основой является сумматор. Аккумулятор – регистр, хранящий значение результата. Инверсный регистр А используется при операциях вычитания.

В RG признаков – помещаются признаки выполнения операций (результат >0, <0, =0, перенос (С) единицы из старшего разряда, промежуточный перенос, переполнение).

|

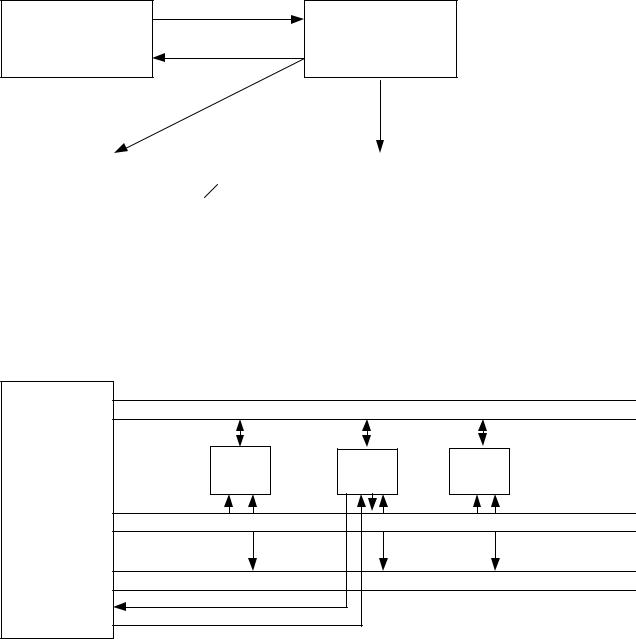

Общая структура процессора |

|

|

|||

|

|

Регистры процессора |

|

|

||

|

|

|

|

|

ШД |

|

RG A |

|

RG B |

RG Команд |

Счетчик |

|

|

|

команд |

|

||||

|

|

|

|

|

||

RG |

|

|

|

Указатель |

|

|

|

|

УУ |

стека |

|

||

Состояний |

|

|

|

|

||

|

|

КС, МПЗУ |

|

|

||

|

|

|

|

|

||

|

|

|

|

Р.О.Н. |

|

|

|

AК |

|

|

RG Адрес |

|

|

|

|

|

|

|

||

|

|

|

|

памяти |

|

|

|

|

ША |

|

|

|

|

|

|

|

ШУ |

ША |

|

|

|

ДШ портов |

|

ДШ адреса |

|

||

|

|

|

|

|

||

линии |

Порты |

|

запись |

Запоминающее |

ШД |

|

ШД |

чтение |

|||||

ввода/ |

ввода/ |

устройство |

|

|||

|

|

|||||

вывода |

вывода |

|

|

|

|

|

Аккумулятор (АК): Используется при операциях с АЛУ, при действиях над данными в аккумуляторе, при пересылке данных (порт ввода, вывода, память).

Регистр команд: Хранит текущую выполняемую команду Регистр признаков (состояний): Содержит признаки результатов вычислений АЛУ (см. выше).

Регистр адреса памяти: Содержит адрес в области памяти, которая будет использоваться. Данные поступают из счетчика команд, или другого регистра произвольно или в результате вычислений (содержимое Сч.К+смещение).

Счетчик команд: Содержит адрес команды, которая должна быть выполнена в следующий момент. При старте системы в Сч.К. записывают начальный адрес программы (где находится первая команда программы) Потом этот адрес посылается в регистр адреса памяти. Команда из памяти по этому адресу считывается в Рг.команд. После декодирования команды содержимое Сч.К. увеличивают на 1, т.е. в Сч.К. будет находится адрес следующей команды. Указатель стека: Стек – область памяти, которая организована по принципу LIFO (последний зашел, первый вышел). Доступ к ячейкам стека выполняется с помощью указателя стека. Указатель стека указывает на первую свободную ячейку.

Регистр состояния (признаков): Содержит признаки результата вычислений АЛУ. Регистры общего назначения (РОН): Используются при выполнении программ, доступны при программировании, могут образовывать регистровые пары.

Команды процессора

Команда сообщает процессору, какую операцию необходимо выполнить и где находятся данные для операции.

Любая команда состоит из двух частей: код операции (КОП) + адрес.

Команды представляются в двоичном виде (неудобно для программиста) => используют мнемоническую запись (JMP, MOV, ADD, INC …)

Способы адресации:

Неявная адресация.

Данные находятся не в основной памяти (регистры общего назначения). Адреса источника и приемника входят в саму команду.

Пример: MOV C, D (перемещение данных из регистра D в регистр С). 1-байтовая команда.

Непосредственная адресация.

Данные находятся в теле команды. 1Б – код операции; 2Б – данные; 3Б – данные.

Не требуется адрес памяти, где находятся данные

Прямая адресация.

1Б – код операции;

2Б – адрес;

3Б – адрес.

В байтах 2 и 3 находится адрес памяти, по которому находятся обрабатываемые данные.

Косвенная адресация.

КОП+РОН 1-байтовая команда, в РОН находится адрес данных в памяти. Перед использованием в РОН заносят адрес.

Типы команд

1.Команды передачи данных

–команды обмена данными между регистрами внутри процессора (регистровые пересылки)

MOV r1,r2 – перенести данные из регистра r1 в r2

–команды обмена процессора с памятью

ST (store) – сохранить в память (STA A,M – сохранить данные из аккумулятора в ячейку памяти по адресу М)

LD (load) – считать данные из памяти в регистр (LDD r,M – считать данные из ячейки памяти по адресу М в регистр r)

LDA r,данные – занести данные в регистр r

–команды обмена процессора с периферийными устройствами (имеющими свое адресное пространство)

IN, OUT

2.Команда обработки данных

–арифметические команды

Сложение

ADD r (сложить данные из аккумулятора с данными из регистра r и поместить результат в аккумулятор: A + r → A)

ADD M (сложить данные из аккумулятора с данными из ячейки памяти по адресу М и поместить результат в аккумулятор: A + M → A)

Вычитание

SUB r (A – r → A) SUB M (A – M → A)

Инкремент INC r (r + 1 → r) Декремент DEC r (r – 1 → r)

–логические команды – выполняются над аккумулятором и регистром Логическое И AND r (A & r → A)

Логическое ИЛИ OR r (A + r → A) Сравнение CMP r

–команды сдвига

Циклический сдвиг аккумулятора влево – RAL, вправо – RAR

3.Команды управления

–команды перехода

безусловный переход по адресу: JMP М (М – адрес)

условный переход по адресу (анализируется регистр признаков): JZ M – переход, если в регистре признаков есть индикация 0 JNZ M – переход, если в регистре признаков нет индикации 0 JN M – переход, если в регистре признаков есть индикация < 0 JNN M – переход, если в регистре признаков есть индикация > 0

– вызов подпрограмм

безусловный вызов подпрограммы по адресу: CAL М (М – адрес)

условный вызов подпрограммы по адресу (анализируется регистр признаков): CZ M – вызов подпрограммы по адресу, если в регистре признаков есть индикация 0

CNZ M – вызов подпрограммы по адресу, если в регистре признаков нет индикации 0

выход из подпрограммы: RET

Режимы работы процессора

Программный режим

Процессор является активным устройством, управляющий всеми основными блоками, реализуется машинный цикл, который состоит из 2-х частей:

–выборка. Из счетчика команд берется адрес команды, заносится в регистр адреса памяти, из памяти считывается команда и заносится в регистр команды, после этого счетчик команд увеличивает свое значение на единицу.

–выполнение команд. Из регистра команд команда попадает на дешифратор команд устройства выполнения, вырабатывается сигнал управления для АЛУ.

Режим обращения к подпрограммам |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

стек |

|

|

А1 |

|

B1 |

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

А2 |

|

B2 |

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

||

|

|

А3 |

|

B3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

C3 |

Указатель |

|

|

|

|||

|

|

… |

|

... |

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Аi CALL |

|

Bi CALL |

|

|

стека |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

Ai+1 |

|

B i+1 |

|

… |

|

|

|

|

|

|

|

|

|

|

|

|

|

Вi+1 |

|||

|

|

… |

|

… |

|

|

|

|

|

||

|

|

|

|

Return |

|

|

|

|

|

||

|

|

|

|

Return |

|

|

|

|

|

Аi+1 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Сч.К |

Аi+1 |

Сч.К |

Вi+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Программа – это последовательность команд. Пусть при выполнении программы А произошел вызов (CALL) подпрограммы В. При этом в специальную область памяти, называемую стеком, заносится содержимое счетчика команд (Сч.К.), значения РОН, Рг.Признаков на момент выполнения вызова подпрограммы В. Далее выполняется

подпрограмма В. Если при выполнении подпрограммы В была вызвана подпрограмма С, то в стек также заносится содержимое счетчика команд (Сч.К.), значения РОН, Рг.Признаков на момент выполнения вызова подпрограммы С. После выполнения подпрограммы С по команде Return происходит считывание содержимого счетчика команд (Сч.К.), значения РОН, Рг.Признаков для восстановления состояния системы для выполнения подпрограммы В. Аналогично происходит и при возвращении в программу А. Указатель стека используется для перемещений между ячейками стека.

Работа с прерываниями

При запросе от внешнего устройства (прерывания) процессор заканчивает выполнение текущей команды и выполняет действие, аппаратно реализованного вызова подпрограммы обслуживания прерывания (также записывается в стек счетчика команд, регистр общего назначения) в счетчик команд записывается команда подпрограммы обработки прерывания (подпрограмма работы с устройством, вызвавшим прерывание).

Различают прерывания по важности. В тексте программы существуют участки запрета прерываний, после этого участка вставляется команда разрешения прерывания (маскирование прерываний). Однако, есть так называемые не маскируемые прерывания – их нельзя запретить. Сигналы от них поступают на специальные входы процессора. Прерывания могут приходить от разных устройств – необходимо определять, от какого устройства пришло прерывание. Используют три основных способа:

–векторный способ Процессор имеет число входов для приема прерывания = числу устройств. При поступлении на определенный вход прерывания вызывается подпрограмма обработки прерывания от этого устройства. Каждое прерывание имеет свой вектор, по вектору определяют начальный адрес подпрограммы обработки прерываний. Недостатком является большое число входов.

–радиальный используется внешнее устройство – контроллер, который осуществляет распределение приоритетов прерываний от устройств.

|

Шина данных |

|

|

|

CPU |

|

IRQ |

|

|

IRQ |

Контроль |

|

||

ВУ |

ВУ |

|||

прерываний |

||||

|

|

|

||

|

|

IRQ |

|

Контроллер выставляет запрос CPU и выставляет вектор прерываний (адрес подпрограммы) на шину данных. Процессор избавляется от лишней работы, меньше число выводов, возможно наращивать.

– режим опроса. Все устройства соединяются одной шиной с входом прерывания процессора, и при выставлении прерываний запускается программа опроса всех возможных источников прерываний. После определения источника запроса прерывания, запускается программа обработки прерывания. Более медленный способ, но можно гибко реализовать программно.

Режим прямого доступа к памяти

Программно-управляемая пересылка данных (между устройством ввода/вывода, памятью) выполняется через аккумулятор чередованием команд записи из порта в аккумулятор и из аккумулятора в память. Вызывает большие накладные расходы, выполняется очень медленно. Используется режим прямого доступа к памяти, реализуется с помощью контроллера.

Данные напрямую передаются в ОЗУ посредством контроллера прямого доступа. Во время режима ПДП процессор лишен возможности обращения к памяти.

Возможно

программирование

Микропроцессор

Состояние

Контроллер прямого доступа

|

|

|

|

|

|

е |

|

|

|

|

|

и |

|

|

|

|

|

н |

|

|

|

|

|

|

е |

|

|

|

|

|

л |

|

|

|

|

|

в |

|

|

|

|

|

а |

|

|

|

|

|

р |

|

|

|

|

|

|

п |

|

|

|

|

|

|

У |

|

|

|

|

|

|

Управление

ОЗУ |

|

Данные |

Устройство |

|

|

ввода/вывода |

|

|

|

|

|

|

|

|

|

Обмен данными между устройствами может быть реализован в следующих режимах:

1.Блочная передача. В этом режиме процессор останавливается на все время передачи блока данных и ожидает, пока устройства обмениваются информацией. Устройства выполняют монопольный захват шины данных.

2.Мультиплексный режим (режим одиночных передач) – обмен данными происходит в промежутках, когда шина данных не используется процессором (например, в машинном цикле есть этап декодирования команды, когда системные шины не используются).

|

Шина данных |

|

ОЗУ |

КПДП |

ВУ |

ЦП |

|

Шина адреса |

|

|

|

|

Шина управления |

|

Захват шин |

|

|

Подтверждение захвата шин |

|

|

Обмен информацией между ВУ и ОЗУ выполняется с помощью КПДП – контроллера прямого доступа к памяти.

Контроллер прямого доступа к памяти (КПДП) включает в себя следующие регистры:

1.Регистр состояния, в котором указывается: тип режима передачи (блочный/мультиплексный), готовность к передаче, окончание передачи данных, наличие запросов(прерываний) от ВУ на передачу данных)

2.Регистр начального адреса (содержит адрес, с которого следует записывать данные в устройство-приемник)

3.Регистр – счетчик пересылок, содержит число байт подлежащих пересылке

Режим прямого доступа осуществляется следующим образом:

Перед обменом из ВУ процессор считывает начальный адрес и объем данных, которые необходимо передать в ОЗУ, эти данные записываются соответственно в регистр начального адреса и в счетчик пересылок КПДП.

КПДП выставляет сигнал «захват шин». Процессор отключается от системных шин (переводит выводы микросхемы в Z-состояние) и выставляет сигнал «подтверждение о захвате шин». После этого осуществляется обмен данными между внешним устройством (ВУ) и ОЗУ под управлением КПДП. КПДП последовательно подает на адресную шину памяти микропроцессорной системы адреса и вырабатывает сигналы управления чтением и

записи. При пересылке каждого байта осуществляется уменьшение значения счетчика на единицу. Как только содержимое регистра-счетчика пересылок будет равен 0, во ВУ выдается сообщение, что пересылка закончена, КПДП снимает сигнал «захват шин», а процессор снимает сигнал «подтверждение захвата шин».

Слово состояния процессора – это информация о прерываниях на процессоре и текущем значении регистра признаков.

Интерфейсы ЭВМ

Интерфейс – это совокупность алгоритмов обмена и технических средств, обеспечивающих обмен информацией между устройствами.

Выделяют различные уровни интерфейса А – внутрисистемный интерфейс – обеспечивает взаимодействие компонент ядра (очень

высокое быстродействие, реализуется не стандартно); В – системный интерфейс – сопряжение элементов ядра и элементов подсистемы ввода/вывода;

С – интерфейс ввода/вывода обеспечивает согласованность между контроллером ввода/вывода и процессором ввода/вывода;

D – периферийный интерфейс сопряжение контроллеров ввода/вывода с внешними устройствами.

Процессор ввода/вывода выполняет обработку и обмен данными с контроллерами ввода/вывода.

Контроллер ввода/вывода управляет отдельными блоками (внешними устройствами).

ЯДРО

CPU |

CPU |

А |

ОЗУ |

ОЗУ |

КЭШ |

А

В

Процессор ввод/вывод

Контроллер ввод/вывод

|

|

|

|

|

|

С |

|

D |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контроллеры |

|

Контроллеры |

Внешнее |

Внешнее |

|||||||

|

|

|

устройство |

|

устройство |

|||||||

|

ввода/вывода |

|

ввода/вывода |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Внешнее |

Внешнее |

Внешнее |

СИСТЕМА ВВОДА/ВЫВОДА |

|||||||||

устройство |

|

устройство |

|

устройство |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Периферийные интерфейсы

Классификация

по типу сигнала

–дискретные;

–аналоговые (для контроля данных);

–перестраиваемые (аналоговые + цифровые)

по направлению передачи сигнала

–однонаправленные порты (ввод, вывод);

–двунаправленные;

–порты с альтернативной функцией.

по алгоритму обмена

–с программно-управляемым вводом, выводом (установка и считывание определяется ходом вычислительного процесса);

–стробированием (каждая операция подтверждает импульсом (стробом));

–с полным квитированием (вводят специальные служебные импульсы)

Параллельный интерфейс

ША

Буфер |

Дешифратор |

|

адреса |

||

|

ШД

Чтение УВВ

Запись УВВ Регистр состояния

Прерывание

Внутренняя шина данных

Внутренняя шина данных

Выходные

данные

Выходной

буфер

Выходные данные готовы Данные приняты

Входные

данные

Входной

буфер

Входные данные готовы

Данные приняты

Вывод данных: |

Получение данных: |

|

Входные |

|

данные |

ШД |

Входные |

|

|

|

данные готовы |

Запись УВВ |

Прерывания |

|

|

Выходные |

|

данные |

|

|

ШД |

Выходные |

|

данные готовы |

|

|

Чтение УВВ |

Данные |

|

приняты |

Данные |

|

|

|

приняты |

Пока стоит «данные приняты» «устройство ввода/вывода» не имеет право передавать данные. |

|

Характеристики

Физическая реализация – разъем Количество контактов – 36

Количество подключаемых устройств – 1 (если нет сложных схем дешифрации) Количество разрядов данных – 8 – вывод, 4 - ввод Скорость вывода данных – 80-120 Кбайт/с (зависит от быстродействия приемника и передатчика)

Скорость ввода данных – 40-60 Кбайт/с Длина кабеля - до 2м.

Недостатки данного интерфейса делает неудобным его использование в профессиональных измерительных системах, исключения составляют простые блоки с невысокой скоростью обмена, которые специально разработаны для простого подключения к любому стандартному компьютеру.

Особенности

Является стандартным интерфейсом принтера в персональных компьютерах и был разработан специально для этой цели. Поэтому для подключения измерительных и управляющих приборов данный интерфейс неудобен из-за специфичности (см.

разрядность),

Существуют модификации этого интерфейса, более удобные для подключения различных периферийных устройств:

1.двунаправленный "Bitronics" с возможностью ввода восьмиразрядных чисел и, следовательно, увеличенной вдвое скоростью ввода данных

2.расширенный интерфейс - "EPP" (Enhanced Parallel Port) и интерфейс с расширенными функциями "ECP" (Extended Capabilities Port), включающий в себя возможности EPP плюс поддержку прямого доступа к памяти, оба этих варианта параллельного порта имеют скорость обмена информации теоретически увеличенной до 2 Мбайт/с однако требуют специальных кабелей

Последовательный интерфейс

Число стоповых

Fint

битов |

|

нечетность,четность |

|

битовЧисло |

|

данных |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Буфер передачи |

|||||||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок |

TxD |

Регистр сдвига передачи |

|

управления |

|

Генератор |

|

|

RxD |

|

Регистр сдвига приема |

Регистр |

|

состояния |

|

|

Буфер приемник |

четностиОшибка |

Данныеготовы |

передатчикаБуферпуст |

кадрированияОшибка |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Стоповые |

|

|

|

|

Стартовый |

|

|

|

|

|

биты |

|

|

|

|

|

|

|

|

контроль |

||||

|

|

|

|

бит |

|

|

|

|

|||

|

|

|

|

|

|

|

|

четности |

|||

|

|

|

|

|

|

|

|

|

|||

Режимы работы:

1.Синхронный режим (передача и прием бит тактируется импульсами синхронизации). Информация передается и принимается через вход RxD. Через выход передатчика TxD выдаются синхроимпульсы, стробирующие принимаемые или выдаваемые биты. Формат посылки - 8 бит. Скорость приема и передачи задается из ряда тактовых частот.

2.Асинхронный режим. Информация передается через выход TxD, а принимается через RxD. Формат посылки - 11 бит (стартовый - "0", 8 информационных бит, программируемый 9-й бит и стоповые биты - "1"). 9-й бит используется как бит контроля информации по четности/нечетности или в многопроцессорных системах для

идентификации адреса приемника переданного кадра.