ВТиИТ лекции

.pdfВТ и ИТ

Вычислительная техника и информационные технологии.

Содержание

1.Логические элементы в цифровых устройствах……………………………………….3

1)Триггеры………………………………………………………………………….5

a)Асинхронный RSтриггер…………….…………………………..5

b)RS –триггер, синхронизируемый по уровню…………………..6

c)RS –триггер на ИЛИ-НЕ…………………………………………7

d)RS –триггер синхронизируемый по фронту……………………8

e)D –триггер………………………………………………………...9

f)D-триггер синхронизируемый по фронту на MS-схеме……………...10

g)Т-триггер…………………………………………………………10

h)Т-триггер на RSпо MS-схеме…………………………………...11

i)JK-триггер……………………………………………………………….11

j)JK-триггер на MS-схеме………………………………………………..11

2)Цифровые устройства комбинационного типа……………………………….12

a)Мультиплексор………………………………………………….13

b)Демультиплексор………………………………………………..14

c)Мультиплексор –Демультиплексор……………………………14

d)Шифратор (комбинатор)………………………………………..15

e)Дешифратор (декомбинатор)…………………………………...15

f)Счетчики………………………………………………………...16

3)Регистры………………………………………………………………………...20

a)Параллельные регистры………………………………………...22

b)Последовательные регистры…………………………………...23

c)Универсальный регистр………………………………………...24

d)Сумматор………………………………………………………...25

e)Цифровой компаратор…………………………………………..27

2.Цифро-аналоговые (ЦАП) и аналого-цифровые (АЦП) преобразователи…………28

1)Цифро-аналоговые преобразователи………………………………………….29

2)Аналого-цифровые преобразователи………………………………………….32

3)АЦП последовательных приближений………………………………………..33

4)АЦП поразрядного взвешивания……………………………………………...33

5)АЦП с двойным интегрированием…………………………………………….35

6)Сигма-дельта АЦП……………………………………………………………...36

3.Память в вычислительных системах…………………………………………………..39

1)Основные параметры памяти…………………………………………………..39

2)Структуры запоминающих устройств………………………………………...40

4.Программируемые логические матрицы, программируемые логические интегральные схемы……………………………………………………………………47

1)Программируемые логические матрицы……………………………………...47

2)Программируемые логические микросхемы………………………………….52

5.Теория автоматов……………………………………………………………………….55

1)Способы задания функции работы автомата…………………………………55

2)Типы реализации автоматов…………………………………………………...56

6.Архитектура ЭВМ………………………………………………………………………57

1)Принципыпрограммного управления…………………………………………57

2)Классификация процессоров…………………………………………………..57

3)Однопроцессорные ЭВМ………………………………………………………59

7.Структура процессора………………………………………………………………….60

1)Устройство управления………………………………………………………...60

2)АЛУ……………………………………………………………………………...61

3)Общая структура процессора. Регистры процессора…..…………………….62

4)Команды процессора…………………………………………………………...63

5)Режимы работы процессора……………………………………………………64

8.Интерфейсы ЭВМ……………………………………………………………………....68

1)Периферийныеинтерфейсы…………………………………………………….68

2)Параллельный интерфейс……………………………………………………...69

3)Последовательный интерфейс…………………………………………………70

4)Периферийные интерфейсы (продолжение)………………………………….72

5)Системные интерфейсы и интерфейсы ввода/вывода………………………..78

6)Способы увеличения быстродействия процессоров…………………………81

7)Конвейерное устройство……………………………………………………….81

8)Суперскалярная архитектура…………………………………………………..82

9)Блок перестановки команд……………………………………………………..82

10)Предсказание переходов……………………………………………………….83

11)Спекулятивное исполнение команд…………………………………………...83

9.Микроконтроллеры……………………………………………………………………..85

1)Общие особенности управляющих микроконтроллеров…………………….85

2)Четырехразрядные микроконтроллеры……………………………………….85

3)Управляющие восьмиразрядные микроконтроллеры семейства MCS-51 фирмы Intel и совместимые с ними……………………………………………86

4)Шестнадцатиразрядные микроконтроллеры………………………………….87

a)Однокристальные микроконтроллеры Intel MCS-96…………87

b)Структура микроконтроллера………………………………….87

c)Периферийные устройства……………………………………..89

5)Характеристики микроконтроллеров подсемейств…………………………..92

10.Цифровая обработка сигналов..………………………………………………………..94

1)Общие принципы цифровой обработки сигналов……………………………94

2)Алгоритмы цифровой обработки сигналов…………………………………...94

11.Цифровые процессоры обработки сигналов………………………………………….97

12.Литература………………………………………………………………………………99

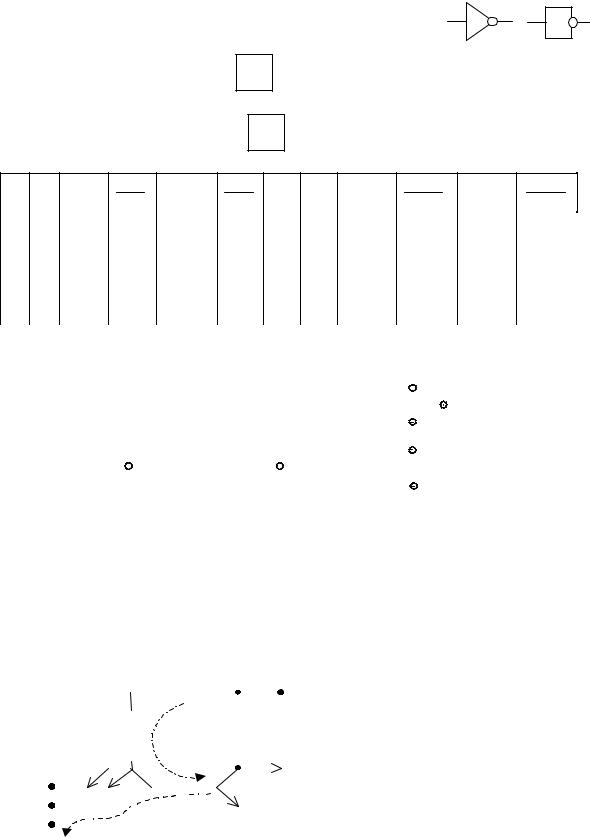

Логические элементы в цифровых устройствах

Транзисторный ключ выполняет операцию логического НЕ. (на входе “1”, а на выходе ”0”)

Логическое умножение “И” &

Логическое сложение “ИЛИ” 1

ИИЛИ

A |

|

B |

A*B |

|

|

A*B |

A+B |

A+B |

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

A* |

|

|

A* |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

B |

|

|

B |

|

|

|

|

B |

|

|

|

|

|

|

A |

A |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

B |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

1 |

2 |

|

|

|

|

|

3 |

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

7 |

|

|

8 |

|

9 |

|

|

|

10 |

|

|

11 |

|

|

|

|

|

12 |

|

|

|

||||||||||||||||||||||||||||

0 |

0 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

1 |

|

|

1 |

|

1 |

|

|

|

0 |

|

|

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|

|

||||||||||||||||||||||||

0 |

1 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

1 |

|

|

0 |

|

0 |

|

|

|

1 |

|

|

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|

|

||||||||||||||||||||||||

1 |

0 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

0 |

|

|

1 |

|

0 |

|

|

|

1 |

|

|

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|

|

||||||||||||||||||||||||

1 |

1 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

0 |

|

|

0 |

|

0 |

|

|

|

1 |

|

|

|

0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Прямая логика |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Обратная логика. |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Y=A*B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y=A+B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

A*B |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Y=A*B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y=A+B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A+B |

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Теоремы Моргана |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

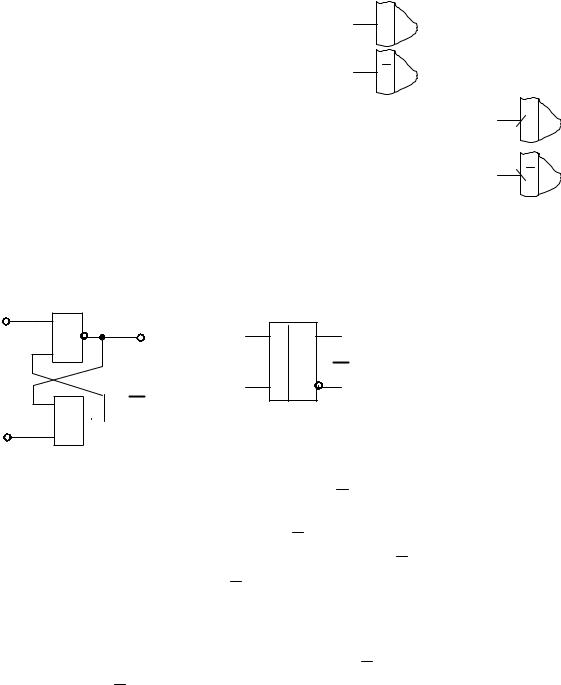

Выполняют преобразование из одного базиса в другой |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||

|

A*B=A+B |

|

|

|

|

A+B=A*B |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Можно реализовать любую функцию, только имея |

|||||||||||||||||||||||||||||||||||||||||||||

|

A*B=A+B |

|

|

A+B=A*B |

“ИЛИ-НЕ” и ”И-НЕ”. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Интегральная транзисторно-транзисторная логика (ТТЛ). |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Реализация “И-НЕ” |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1многоэмиттерный транзи- |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+Eп |

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

стор (существует только в интеграль- |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rб |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rк |

|

|

|

|

|

|

|

|

|

|

|

|

|

ном исполнении). |

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

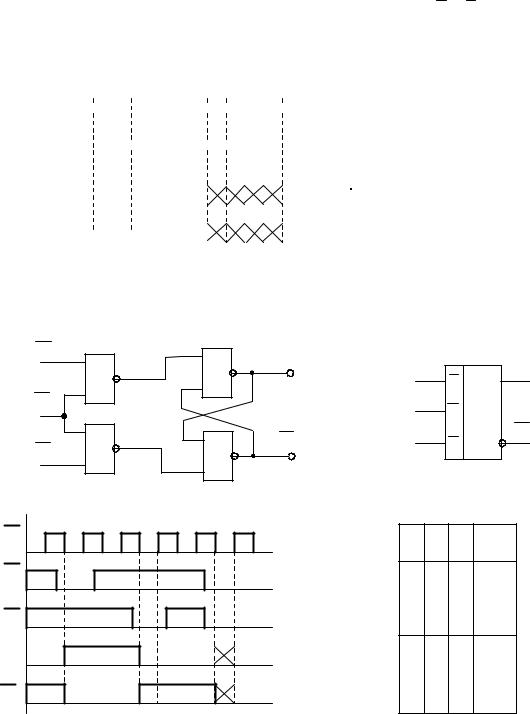

Если на оба входа VT1 подать ”+” |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвых |

|

(логическая “1”), то коллектор VT1 |

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1 |

|

смещается в прямом направлении, а |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

эмиттер в обратном. Протекает ток i1, |

||||||||||||||||||||||||||||||||||||||||||||||||||

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

на базу VT2 поступает положительный |

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

потенциал VT2 открывается, а на |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

выходе 0. Если хотя бы один вход за- |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

землить (логический “0”), то эммитер- |

|||||||||||||||||||||||||||||

ный переход VT1 смещается в прямом направлении. VT1 открывается и ток i2 течет из базы VT2, закрывая его. На выходе VT2 появляется высокий потенциал (логическая “1”). Работа схемы соответствует функции “И-НЕ”.

Реализация “ИЛИ-НЕ” |

|

|

|

|

|

|

+Eп |

R1 |

R2 |

R3 |

R4 |

A |

|

VT1 |

|

VT01 |

|

|

|

B |

VT02 |

|

Uвых |

|

VT2 |

||

|

|

||

|

|

VT3 |

|

|

|

|

|

Транзисторы VT1 и VT2 включены параллельно. Если A=B=0 (заземлены), то VT01 и VT02 открыты, а VT1 и VT2 закрыты на базе VT3 отрицательный потенциал, VT3 тоже закрыт на выходе логическая 1.

Если на любой из входов подать “+” (логическая единица), то соответствующий VT (VT01 или VT02) открывается, тогда открывается VT1 или VT2 и на базу VT3 поступает положительный потенциал VT3 открывается и на выходе 0. Схема выполняет функцию ”ИЛИ-НЕ”

2

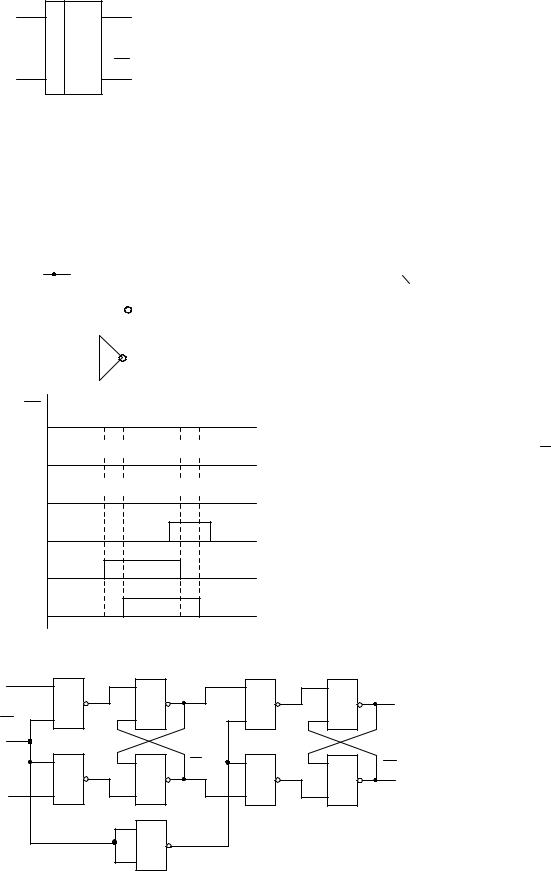

Триггеры

Одно из наиболее распространенных импульсных устройств, относящийся к базовым элементам цифровой техники - это триггер.

Триггером называют устройство, обладающие двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала.

Сигнал управления подается по определенному алгоритму, который определяет работу триггера. Типы триггеров RS, D, T, JK.

Классификация:

1)По алгоритму функционирования - RS, D, T, JK.

2)По способу синхронизации

а) Асинхронные |

|

|

|

б) Синхронизируемые |

C |

|

|

По уровню: |

синхронизируемые ”1” |

|

|

|

синхронизируемые ”0” |

C |

|

|

|

|

|

По фронту: |

синхронизируемые положительным фронтом |

C |

|

|

синхронизируемые отрицательным фронтом |

C |

|

|

|

|

|

Асинхронный RS триггер.

Являются основным элементом триггеров всех типов, т. к. выполняют функцию бистабильной ячейки. Реализуется на двух элементах “ИЛИ-НЕ”.

R

1 |

Q |

T |

Q |

|

R |

Q

S

1 Q S

Допустим, что на входах R и S сигналы равны ”0” (R=0, S=0), а на прямом выходе Q

сигнал равен “1” (Q=1).Тогда на инверсном выходе Q сигнал равен “0”так как на одном из входов (соединенном с Q) сигнал равен “1”. Очевидно, при R=0, S=0 возможно и вто-

рое устойчивое состояние, при котором Q=0, Q =1. Нетрудно видеть, что при S=1, R=0

триггер оказывается в первом устойчивом состоянии (Q=1, Q=0), а при S=0, R=1 – во

втором устойчивом состоянии (Q=0, Q=1). Комбинация S=1, R=1 ( ) запрещенное состояние, выходному сигналу верить нельзя.

Рассмотренный триггер называется RS –триггером. Вход S называется устойчивым (от англ. setустанавливать), а вход R–входом сброса (от англ. reset–вновь устанавливать).

При S=1 триггер устанавливается в состояние ”1” (Q=1, Q =0), при R=1 – сбрасывается в

состояние ”0” ( Q=0, Q=1).

3

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

S |

R |

Qn |

Qn+1 |

хранение |

||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

R |

|

|

|

|

|

|

|

|

|

|

информации |

||||||

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

||||

Q |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

установка0 |

||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

установка1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Q |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

запрещенный |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

* |

режим |

Аналогично работает RSтриггер на элементах И-НЕ с той разницей, что он должен иметь инверсные входы, т. е. В состояние “1” при S=0 и сбрасывается в состояние ”0” при R=0. Запрещенная комбинация входных сигналов для этой схемы - ”0”, “0”.

S |

Q |

|

|

|

|

|

& |

Q |

|

|

|

|

|

|

S T |

|

|

|

|

|

|

R |

Q |

|

|

|

|

& |

|

|

|

|

|

|

Q |

|

|

|

|

|

|

R |

|

|

|

|

|

|

S |

|

S |

R |

Qn |

Qn+1 |

запрещенный |

|

|

0 |

0 |

0 |

* |

|

R |

|

0 |

0 |

1 |

* |

режим |

|

0 |

1 |

0 |

1 |

установка1 |

|

|

|

|||||

Q |

|

0 |

1 |

1 |

1 |

|

|

|

|||||

|

1 |

0 |

0 |

0 |

установка0 |

|

|

|

|||||

Q |

|

1 |

0 |

1 |

0 |

|

|

|

|||||

|

1 |

1 |

0 |

0 |

хранение |

|

|

|

|||||

|

|

1 |

1 |

1 |

1 |

информации |

Рассмотренный RSтриггер относится к асинхронным, так как переход из одного состояния в другое происходит в темпе поступления сигналов на информационные (R,S) входы и не связан с тактовыми сигналами.

|

|

|

RS – триггер, синхронизируемый по уровню. |

||

S |

& |

S |

& |

Q |

S T Q |

|

|

|

|||

C |

|

|

|

|

C |

|

& |

R |

& |

Q |

Q |

R |

R |

||||

|

|

|

|

|

|

4

В синхронных триггерах помимо информационных имеется вход тактовых (синхронизирующих) сигналов и переключения триггера происходит только при наличии тактового сигнала.

Отличие от асинхронного триггера наличие двух дополнительных элементов И-НЕ,

благодаря которым управляющие сигналы проходят на входы R и S только при воздействии на синхронизирующий вход сигнала “1” (C=1).

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

S |

R |

Qn+1 |

режимы |

||||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

n |

хранение |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

Q |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

информации |

|||

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

Qn |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

0 |

1 |

0 |

|

установка 0 |

|||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

установка 1 |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

* |

|

запрещенный |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

режим |

RS – триггер на ИЛИ-НЕ.

S |

1 |

1 |

Q |

|

R T |

Q |

|

С |

|

|

|

|

|||

|

|

|

|

C |

|

|

|

|

1 |

|

|

|

|

Q |

|

R |

1 |

Q |

|

S |

|

||

|

|

|

|

||||

|

|

|

|

|

|

|

|

C |

|

|

C |

S |

R |

Qn+1 |

|

|

|

|

|

||||

S |

|

|

0 |

0 |

0 |

* |

|

|

|

|

0 |

1 |

1 |

|

|

R |

|

|

|

1 |

0 |

0 |

|

|

|

|

1 |

1 |

Qn |

|

|

Q |

|

|

|

0 |

0 |

Qn |

|

|

|

1 |

0 |

1 |

|

||

Q |

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

5

RS – триггер синхронизируемый по фронту.

R T Q  C

C

Q

S

Таблица состояний аналогична таблице RS-триггера, синхронизированного по уровню.

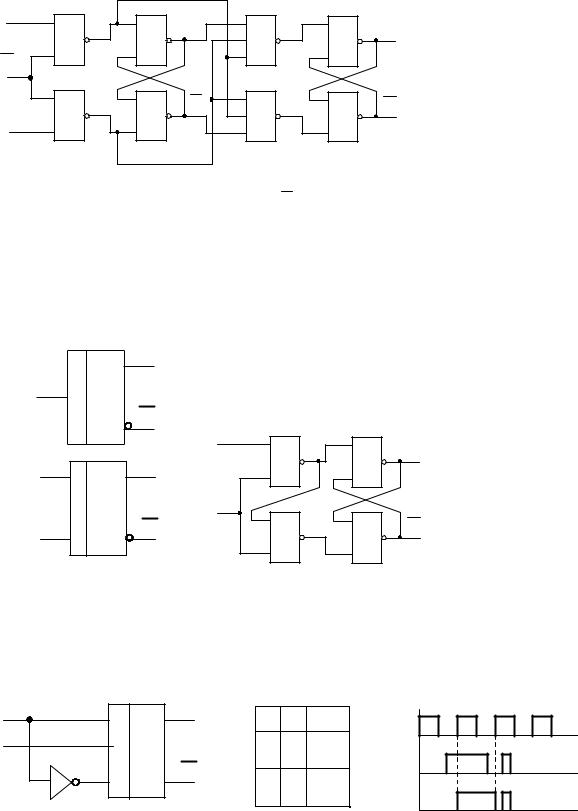

Реализуется при помощи схемы MS (Master-Slave – начальникподчиненный):

1.С инвертором

2.С запрещающими связями

Содержит два синхронизируемых по уровню RS триггера, один из которых управляется импульсом синхронизации, а второй – паузой.

|

MS-схема с инвертором |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

M |

|

S |

Q |

|

|

|

|

|

|

|

|

|

||||||||||

S |

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

Q |

||||||||||

|

|

|

S |

|

T |

|

S |

T |

|

|

R |

TT |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

C |

|

|

C |

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

||||||

|

R |

|

|

|

R |

|

|

|

|

|

Q |

1 |

|

R |

|

|

Q |

|

|

S |

|

|

Q |

|

||||

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

C

C

C

S

S

R

Q1

Q

М- триггер запускается под действием С и управляется S и R, а S-триггер подтверждает состояние M-триггера с приходом импульса С, т.е. происходит перезапись информации из М-триггера в S-триггер по заднему фронту синхронизации.

S |

M |

|

& |

||

|

||

C |

DD 1 |

|

|

||

|

& |

|

R |

DD 2 |

|

|

|

|

|

S |

|

& |

Q1 |

& |

& |

Q |

DD 3 |

|

DD 5 |

DD 7 |

|

& |

Q1 |

& |

& |

Q |

DD 4 |

|

DD 6 |

DD 8 |

|

& |

|

|

|

|

DD 9 |

|

|

|

|

6

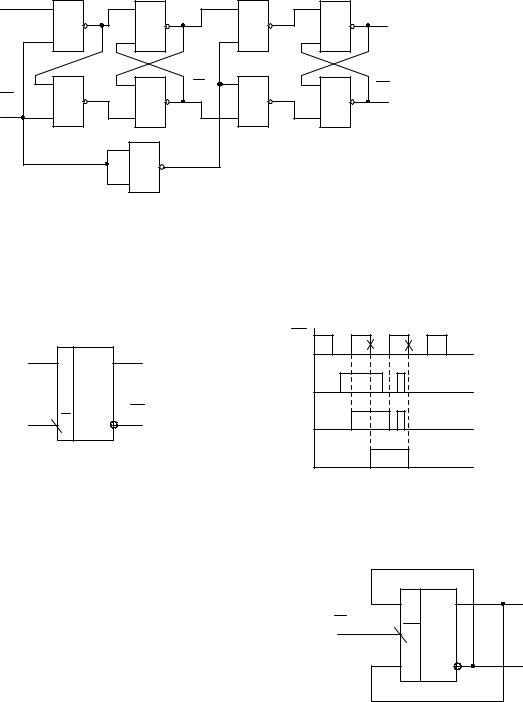

В реальных схемах исключают инвертор. Инверсию схемы можно взять на схемах DD1 и DD2 тогда такой триггер будет с запрещающими связями.

S |

& |

& |

Q1 |

& |

& |

Q |

|

||||||

C |

DD 1 |

DD 3 |

|

DD 5 |

DD 7 |

|

|

|

|

|

|

|

|

R |

& |

& |

Q1 |

& |

& |

Q |

DD 2 |

DD 4 |

|

DD 6 |

DD 8 |

|

|

|

|

|

Если сигнал S заканчивается раньше, чем С , то (т.е. на входе S DD1 или R DD2 формируется 0), Тогда на выходах DD1(DD2) формируется 1, которая отпирает схемы DD5, DD6, обеспечивая переброс DD7, DD8.

D – триггер

Для приема информации по одному входу используется D-триггер.

T |

Q |

Асинхронный D-триггер не используют, а используют синхро- |

||

|

низируемый по уровню или по фронту. |

|||

D- |

|

триггер на И-НЕ –упрощают, в качестве инвертора использу- |

||

D |

|

ется DD1. |

|

|

|

Q |

|

|

|

|

D |

|

|

|

|

|

|

Q |

|

|

Q |

& |

& |

|

D T |

DD 1 |

DD 3 |

|

|

|

|

|||

|

|

C |

|

|

С |

Q |

& |

& |

Q |

|

|

|

||

|

DD 2 |

DD 4 |

|

|

|

|

|

||

D-триггер переходит в состояние “1” (Q=1), если в момент синхронизирующего сигнала (С=1) на его информационном входе сигнал ”1” (D=1). В этом состоянии триггер остается и после окончания сигнала на входе D до прихода очередного синхронизирующего сигнала, возвращающего триггер в состояние “0”. Таким образом, D-триггер “задерживает” поступившую на его вход информацию на время, равное периоду синхронизирующих сигналов. D-триггер можно получить из RS-триггера.

D |

S T |

Q |

C |

D |

Qn+1 |

C |

C |

C |

|

0 |

0 |

Qn |

|

|

|

0 |

1 |

|

D |

|

|

|

Q |

|

|||

|

R |

1 |

0 |

0 |

|

|

|

|

|

1 |

1 |

1 |

Q |

Недостаток: Если на вход D пройдет помеха, то она появится и на выходе.

7

D-триггер синхронизируемый по фронту на MS-схеме

D |

|

Q1 |

& |

& |

|

& |

& |

Q |

|||

DD 1 |

DD 3 |

|

DD 5 |

DD 7 |

|

& |

& |

Q1 |

& |

& |

Q |

C |

|

|

|

|

|

DD 2 |

DD 4 |

|

DD 6 |

DD 8 |

|

|

& |

|

|

|

|

|

DD 9 |

|

|

|

|

М-триггер реализован по схеме D-триггера с синхронизацией по уровню. S- триггер - обычная схема с инвертором (DD9), либо по схеме с запрещающими связями. Перезапись информации из D->S происходит по заднему фронту импульса синхронизации. D-триггер синхронизированный по фронту и по уровню называют триггером задержки – запись происходит по импульсу синхронизации, т.е. это либо регистр памяти, либо регистр сдвига.

D TT |

Q |

C |

|

D |

|||

|

|

||

С |

Q |

Q1 |

|

|

|

Q |

Т-триггер

В режиме двоичного счета при наличии импульса управления меняет свое состояние на обратное. Может быть реализован на любом другом триггере с использованием внутренних обратных связей.

Т |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

|

|

T |

S |

TT |

C |

|

|

|

|

|

|

R |

|

8