- •Основы электроники

- •1. Полупроводниковые выпрямительные диоды и стабилитроны

- •2. Выпрямители и фильтры.

- •3. Биполярные транзисторы

- •4. Тиристоры

- •5. Полевые транзисторы

- •6. Биполярные транзисторы с изолированным затвором (igbt)

- •7. Операционные усилители

- •8. Элементы цифровой электроники

- •9. Микропроцессоры и микроЭвм

- •Литература

8. Элементы цифровой электроники

Общая характеристика

Цифровое представление информации позволяет передавать и обрабатывать ее без искажений. Оно оказывается наиболее рациональным для компьютеров, измерительных приборов, сигналов управления и т.д. В настоящее время цифровые устройства применяются все шире, вытесняя аналоговые устройства, то есть такие, которые используют непрерывные сигналы.

Цифровые микросхемы выпускаются на основе различных полупроводниковых элементов. Наиболее распространены микросхемы двух технологий - ТТЛ (транзисторно-транзисторная логика) и КМОП (комплементарные МОП-структуры). ТТЛ реализуется на биполярных транзисторах, КМОП - на полевых. Микросхемы ТТЛ и КМОП работают на основе транзисторных усилителей, которые переключаются между режимами отсечки и насыщения. В некоторых случаях для повышения быстродействия насыщения не допускают, используя режим, близкий к насыщению.

Микросхемы ТТЛ обладают большим быстродействием, но меньшей помехоустойчивостью, и они потребляют больше энергии в сравнении с микросхемами КМОП. В больших интегральных схемах(БИС) преобладают КМОП-структуры, так как размещение на одном кристалле большого количества биполярных транзисторов приведет к его перегреву.При работе с микросхемами КМОП нужно обеспечить отсутствие статического электричества, так как оно может их испортить.

В цифровой форме информация обычно имеет вид последовательности двоичных (логических) чисел 0 и 1. В электронных устройствах нуль чаще всего кодируется низким уровнем напряжения (например, для микросхем ТТЛ от -0,5 до +0,4 В), а единица - высоким уровнем (для ТТЛ от +2,4 до +5,5 В). Такая кодировка называется положительной логикой. Если нулю соответствует высокий уровень напряжения, а единице - низкий, то это называетсяотрицательной логикой.

Суть цифровой электроники состоит в том, чтобы в соответствии с входными цифровыми сигналами вырабатывать выходные цифровые сигналы. Эти задачи разделяются на два класса: комбинационныеипоследовательные.

Комбинационные задачи решаются схемами, у которых выходные сигналы соответствуют входным сигналам в настоящий момент времени. Комбинационные схемы реализуют различные функции математической логики.

Последовательные задачи представляют более широкий класс. Выходные сигналы последовательных схем зависят не только от входных сигналов в настоящий момент времени, но и от входных сигналов в предшествующие моменты времени. Иначе говоря, последовательные схемы - это схемы с памятью. Последовательные схемы могут быть собраны на основе элементов комбинационной логики.

Цифровые устройства могут работать в асинхронномилисинхронномрежиме. В асинхронном режиме командой к изменению состояния выходов элемента цифровой схемы служит изменение входных сигналов этого элемента. Переключение одних элементов может не совпадать по времени с переключением других элементов цепи. В синхронном режиме изменение выходов всех элементов происходит одновременно в момент прихода тактового импульса. Для работы элемента цифровой схемы в синхронном режиме необходимо, чтобы он имел специальный вход для приема тактовых импульсов.

Рассмотрим примеры элементов цифровой электроники.

Элементы И-НЕ, ИЛИ-НЕ

|

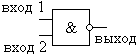

Рис. 8.1. Обозначение элемента И-НЕ на схеме. |

|

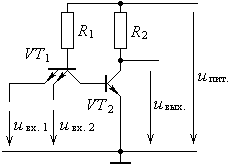

Рис. 8.2. Устройство элемента И-НЕ на базе ТТЛ |

Устройство элемента И-НЕ на базе ТТЛ показано на рис. 8.2. Логическую функцию И выполняет многоэмиттерный транзистор VT1. Когда на всех входах имеются сигналы логической единицы, то все эмиттерные переходы входного транзистораVТ1оказываются закрытыми. В этом состоянии транзисторVТ1включенинверсно(то есть, эмиттер и коллектор как бы поменялись местами). Ток через резисторR1и переход база-коллектор транзистораVТ1поступает в базу транзистораVТ2и насыщает его. На выходе устанавливается низкое напряжение. Если хотя бы на одном входе оказывается сигнал логического нуля, то соответствующий переход база-эмиттер транзистораVT1открывается, и ток черезR1направляется в этот переход, а не в переход база-коллекторVT1. Из-за этого ток базы транзистораVТ2прекращается, транзисторVT2закрывается, на его выходе устанавливается высокое напряжение.

Элементы И-НЕ бывают не только с двумя, но и с несколькими входами. Все они выдают на выходе отрицание логического произведения всех своих входов.

|

х1 |

х2 |

|

|

х1 |

х2 |

|

|

0 |

0 |

1 |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

|

1 |

1 |

0 |

|

Табл. 8.1. Таблица истинности функции И-НЕ |

|

Табл. 8.2. Таблица истинности функции ИЛИ-НЕ | ||||

|

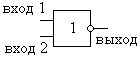

Рис. 8.3. Обозначение эле- мента ИЛИ-НЕ на схеме. |

Однако, даже с помощью только одной функции И-НЕ можно реализовать все функции математической логики. То же относится и к функции ИЛИ-НЕ. Поэтому элементы И‑НЕ и ИЛИ-НЕ чаще других применяются при конструировании электронных логических устройств.

Триггеры

|

S |

R |

Q |

|

0 |

0 |

сохраняется прежнее состояние |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

запрещено |

|

Табл. 8.3. Таблица состояний RS-триггера. | ||

|

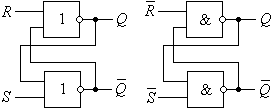

Рис. 8.4. Устройство RS-триггеров. |

Рис. 8.5. Обозначение RS-триггера. |

Простейший RS-триггерсостоит из двух элементов ИЛИ-НЕ (рис. 8.4 слева), либо И-НЕ (рис. 8.4 справа), охваченных обратными связями. Условное обозначениеRS-триггера показано на рис. 8.5. Черта над буквой или выражением означает знак логического отрицания.

Триггер имеет два входа: S(Set - установка) иR (Reset

- сброс), и два выхода:Qи![]() ,

сигналы которых инверсны друг другу.

,

сигналы которых инверсны друг другу.

|

|

|

Q |

|

0 |

0 |

запрещено |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

сохраняется прежнее состояние |

|

Табл. 8.4. Таблица состояний RS-триггера с инверсными входами. | ||

![]() .

.

Так как 1 + х = 1, то

![]() .

На выходеQполучится сигнал

.

На выходеQполучится сигнал

![]() .

.

При обратных входных сигналах (S= 0,R= 1) получаются обратные выходные сигналы. Если оба входных сигнала одинаковы:S =R = 0, то выходные сигналы остаются такими, какими они были:

![]() ;

;

![]() .

.

Если сигналы R = S =

1, то оба выходных сигнала одинаковы:![]() .

После инверсии входных сигналов, когда

они станут

.

После инверсии входных сигналов, когда

они станут![]() ,

триггер с одинаковой вероятностью может

перейти в любое состояние. Из-за этой

неопределенности сигналыR = S = 1

запрещены. СостоянияRS-триггера,

собранного из логических элементов

ИЛИ-НЕ, приведены в табл. 8.3.

,

триггер с одинаковой вероятностью может

перейти в любое состояние. Из-за этой

неопределенности сигналыR = S = 1

запрещены. СостоянияRS-триггера,

собранного из логических элементов

ИЛИ-НЕ, приведены в табл. 8.3.

Аналогично работает RS-триггер из логических элементов И-НЕ (рис. 8.4 справа), только он управляется инвертированными сигналами. Состояния такого триггера приведены в табл. 8.4.

|

J |

K |

Q |

|

0 |

0 |

сохраняется прежнее состояние |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

Устанавливается состояние, инвер- сное предыдущему |

|

Табл. 8.5. Таблица состояний JK-триггера. | ||

|

Рис. 8.6. Обозначение JK-триггера. |

RS-триггеры работают в асинхронном режиме,JK‑триггеры - в синхронном режиме. КромеRS- иJK-триггеров, существуют также триггеры других типов. В общем же, схемы последовательной логики очень разнообразны.