Синхронный rs триггер

Схема RS триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS триггер и триггер Шмитта) эти триггеры получили название асинхронных.

4.1.1.1 Синхронный RS – триггер

Триггеры, записывающие сигналы только при наличии синхронизирующего сигнала называются синхронными. Принципиальная схема синхронного RS-триггера приведена на рисунке 4.6.

Рисунок 4.6

- Схема синхронного RS триггера,

построенного на элементах "И-НЕ"

Рисунок 4.6

- Схема синхронного RS триггера,

построенного на элементах "И-НЕ"

В таблице 4.1 приведена таблица истинности синхронного RS триггера. Принцип работы RS триггера не изменился, добавилось дополнительное условие: синхронизация момента срабатывания схемы. В этой таблице символ 'x' означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 4.1

Таблица - истинности синхронного RS триггера.

|

С |

R |

S |

Q(t) |

Q(t+) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 | |

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 | |

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

1 |

0 |

1 |

1 |

1 | |

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

1 |

0 |

1 |

0 | |

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

Как мы уже показали выше, RS триггеры могут быть реализованы на различных логических элементах. При этом их логика работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные RS триггеры обычно изображаются в виде условно-графических обозначений. Условно-графическое обозначение синхронного RS триггера приведено на рисунке 4.7.

Рисунок 4.7

- Условно-графическое обозначение

синхронного RS триггера

Рисунок 4.7

- Условно-графическое обозначение

синхронного RS триггера

4.1.2 D-триггер

D-триггер(от английского Delay–задержка) имеет один

информационный (D – Data – данные)

и один тактируемый (С – Clock – тактовая

последовательность) вход. Такой триггер

можно получить из RS-триггера,подав на

R-вход инвертированный сигнал с S-входа

(рисунок 4.8, а). Уловное обозначение

D-триггера со статическим управлением

показано на рисунке 4.8, б.

Из временных диаграмм, приведенных на рисунке 4.8, в, можно увидеть, что при С = 1 триггер работает как повторитель (Q = D), а при переходе сигнала на входе С от логической единицы к логическому нулю триггер запирается и переходит в режим хранения (защелкивает информацию со входа D). В отличие от RS-триггера, D-триггер не имеет запрещенного состояния.

Статический синхронный триггер реагирует на входные сигналы в течение всего времени, пока тактовый сигнал С равен единице. Часто, однако, требуется триггер, в котором считываемая информация не передавалась бы непосредственно на выход, а появлялась там только тогда, когда все схемы уже заперты. Этим свойством обладают триггеры с динамическим управлением.

4.1.2.1 D-триггер с динамическим управлением

Тактируемый фронтом тактового импульса, можно выполнить по двухступенчатой схеме, показанной на рисунке 4.9, а. При С=0 триггер первой ступени повторяет сигнал D, но триггер второй ступени защелкнут (находится в режиме хранения). При переходе к С = 1 первый триггер защелкивает на своем выходе информацию со входа D, а второй повторяет ее на своем выходе. Таким образом, двухступенчатый триггер по фронту тактового импульса защелкивает на своем выходе уровень сигнала со входа D и сохраняет его до следующего фронта. Триггеры с динамическим управлением необходимы для построения счетчиков и регистров сдвига. Из двух вариантов УГО динамического входа, приведенных на рисунке 4.9, б и в, в дальнейшем будем использовать вариант б, меняя направление косой черты для обозначения входа при тактировании по срезу импульса.

4.1.3 Т-триггер

Т-триггер (от английского Toggle – опрокидываться, кувыркаться). Он имеет только тактовый вход Т и меняет свое состояние на противоположное по фронту или срезу каждого нового тактового импульса (рисунок 4.10). На рисунке показано УГО Т-триггера и как можно выполнить Т-триггер на базе RS- или D-триггеров с динамическим управлением. Каждый раз по фронту сигнала Т изменяется уровень напряжения на выходе Q. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на его тактовом входе. Это свойство Т-триггера используется при построении двоичных счетчиков, а Т-триггер называют также счетным триггером.

Рисунок 4.10 – Cчетный триггер и временные диаграммы его работы

4.1.4 JK-триггер

JK-триггер выполняет наиболее универсальные функции (J – Jerk – резкое движение, толчок; K – Kill – ликвидировать). Он строится на базе RS-триггера с динамическим тактовым входом (рисунок 4.11), но, в отличие от него, в JK-триггере устранено запрещенное состояние при J= K= 1. При совпадении логических единиц на информационных входах J и K он работает как счетный (режим переключения), т.е. меняет свое состояние на противоположное при каждом новом такте. Логическая 1 на входе J устанавливает триггер в состояние единицы (режим записи 1, установка), логическая 1 на входе К переводит триггер в состояние логического нуля (режим записи 0, сброс) при наличии тактирования. При наличии логических нулей на входах J и К тактовый импульс не меняет состояние триггера (режим хранения). Работу триггеров можно описать таблицей состояний и функциями переходов (рисунок 4.12).

Рисунок – 4.11

Функции переходов синхронных триггеров описывают состояние триггера Q+ после прихода очередного тактового импульса (его фронта или среза)как логическую функцию входных сигналов и исходного состояния триггера Q до прихода тактового импульса

Рисунок – 4.12

Примеры микросхем триггеров приведены на рисунке 4.12. Наряду с тактируемыми, микросхемы К555М2 и К555ТВ6 имеют дополнительные входы для предварительной установки в единичное или нулевое состояние (комбинированные триггеры).

При этом

входы установки

и

и являются асинхронными (приоритетными).

Предельная частота функционирования

триггеров К555ТМ2 составляет 25 МГц, К555ТВ6

– 30 МГц.

являются асинхронными (приоритетными).

Предельная частота функционирования

триггеров К555ТМ2 составляет 25 МГц, К555ТВ6

– 30 МГц.

4.1.5 MS –триггер

Двухтактный триггер состоит из двух ступеней – двух триггеров: первая ступень – М ( master - хозяин ), а вторая ступень – S ( slave – помощник ). Тип двухтактного триггера определяется типом триггера первой ступени. Возьмём двухтактный RS – триггер (рис. 4.13).

Если сигнал С=1, то первая ступень находится в режиме приема информации, а вторая - в режиме хранения, так как сигнал синхронизации на её входе равен нулю. Если С=0, то первый триггер переходит в режим хранения, а второй - в режим приема информации и копирует состояние первого триггера.

Именно в этот момент информация появляется на выходе триггера (Q).

Рисунок 4.13 – Двухтактный RS – триггер

Рисунок 3.14 – Изображение двухтактного RS – триггера

4.2 Асинхронные и синхронные триггеры

По способу записи информации триггеры могут быть асинхронными и синхронными.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах, составляющих данный триггер.

Синхронные триггеры с динамическим тактированием изменяют своё состояние только в момент определённого перехода тактового сигнала (либо 0→1, либо 1→0, т.е. по переднему или заднему фронту тактового импульса). При неизменном уровне сигнала на тактовом входе никакие изменения на информационных входах не отражаются на состоянии триггера.

На рисунке 4.15 показана схема D-триггера с тактированием по переднему фронту тактового сигнала.

Рисунок – 4.15 D-триггер с динамическим тактированием

Триггер состоит из трёх асинхронных RS-триггеров на элементах И-НЕ. Один из триггеров основной (DD5, DD6), два других — вспомогательные (DD1, DD2 и DD3, DD4) которые запоминают состояние линии D в момент положительного перепада сигнала С и предотвращает повторное срабатывание.

Когда тактовый сигнал неактивен (С=0), оба вспомогательных триггера имеют на выходе сигнал 1 (основной триггер, таким образом, находится в режиме хранения), причём один из них находится в состоянии «включён» (на выходах логических элементов сигналы 1 и 0), а второй — в «запрещённом» состоянии 11. Какой из триггеров находится в «запрещённом» состоянии, зависит от сигнала на входе D. Так, если D=0, то триггер DD3, DD4 находится в состоянии 11, а триггер DD1, DD2 — в состоянии 10, а при D=1 наблюдается обратная картина.

Как только вход С претерпевает скачок 0→1, вспомогательные триггеры фиксируются в противофазных состояниях 10 и 01, которые не меняются ни при каких изменениях сигнала D. Соответственно, основной триггер оказывается в одном из двух состояний, в зависимости от сигнала D в момент скачка тактового сигнала.

Рисунок 4.16 – JK-триггер с дополнительными асинхронными инверсными входами S и R

5 Регистр

Регистр - это микроэлектронное устройство, предназначенное для хранения и преобразования информации, представленной в двоичной форме. Информация представляется двоичными последовательностями (сигналов) в виде «слов» определенной длины. Слова могут иметь длину кратную 4 битам, т.е. 4, 8, 12, 16 и т.д

Регистры (англ. Register) представляют собой несколько триггеров соединённых между собой различными способами.

Вообще регистров бывает два основных вида:

параллельный регистр;

последовательный регистр или регистр сдвига.

Рисунок

– 5 Схема соединения триггеров в

параллельном регистре

Рисунок

– 5 Схема соединения триггеров в

параллельном регистре

В параллельном типе регистров триггеры соединены параллельно, то есть каждый внутренний триггер имеет свой вход D и свой выход Q, которые не зависят от других триггеров, а также вход С, который называется тактовым входом и для всех входящих в регистр триггеров он является общим. Параллельные регистры бывают двух типов:

тактируемые регистры, которые срабатывают по фронту сигнала управления (вход С);

стробируемые регистры, которые срабатывают по уровню входного сигнала (вход С);

Наибольшее распространение получили тактируемые параллельные регистры.

5.1 Регистры, срабатывающие по фронту сигнала

Данные типы регистров практически ничем не отличаются от D триггеров. Напомню, что на выходе Q устанавливается такой уровень напряжения, который был на входе D, в момент положительного фронта тактового сигнала на входе С. Так как регистр состоит из нескольких D триггеров, то и количество (4,6,8,16) запоминаемых сигналов (бит) у регистра больше.

Рисунок

– 5.1 Параллельные регистры, срабатывающие

по фронту импульса

Рисунок

– 5.1 Параллельные регистры, срабатывающие

по фронту импульса

Большинство регистров восмибитные и в основном различаются отсутствием или наличием инверсии сигнала на выходе, входом сброса (R), входом разрешения записи (WE), типом выходов (2C или 3C) и входом EZ. Таблицы истинности тактируемых регистров практически не отличаются от таблицы истинности D триггеров и имеют следующий вид:

Таблица –5 Таблица истинности регистра с входом разрешения записи WE

|

Входы |

Выход | ||

|

WE |

C |

D |

Q |

|

0 |

0→1 |

0 |

0 |

|

0 |

0→1 |

1 |

1 |

|

0 |

0 |

X |

Не меняется |

|

0 |

1 |

X |

Не меняется |

|

1 |

X |

X |

Не меняется |

Основное применение регистры с тактируемым входом нашли в схемах где необходимо хранить некоторый код в течении необходимого времени, а по фронту импульса на тактовом входе С выдавать на выходы Q.

5.2 Регистры, срабатывающие по уровню сигнала

Данные типы регистров являются как бы гибридом между буфером и регистром (ещё такие регистры называют регистры-защёлки, англ. Latch). Принцип работы данных регистров состоит в следующем: когда на стробирующем входе высокий логический уровень, сигнал поступает с входов на выходы регистра, а если на стробирующем входе низкий уровень сигнала, регистр переходит в режим хранения последнего из пропущенных значений входного сигнала. Регистры-защелки не очень распространены из-за своего специфического характера работы, но в некоторых случаях удобнее, регистров срабатывающих по фронту сигнала на тактовом входе.

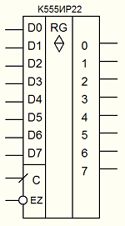

Типичный представитель параллельных регистров срабатывающих по уровню стробирующего сигнала, является микросхема К555ИР22, которая представляет собой восьмиразрядный параллельный регистр, со стробирующим входом С и выходами с тремя состояниями (3С).

Рисунок – 5.2 микросхема К555ИР22